System-level chip and communication method supporting usb and gpio conversion

A system-level chip and USB interface technology, applied in the field of FPGA applications, can solve problems such as high cost and limit user design flexibility, achieve low cost, avoid design complexity, and optimize the effect of system-on-chip architecture

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0030] The system-on-a-chip supporting USB and GPIO conversion and the communication method of the present invention will be further described in detail below in conjunction with the accompanying drawings and specific embodiments. The advantages and features of the present invention will become clearer from the following description. It should be noted that all the drawings are in a very simplified form and use imprecise scales, and are only used to facilitate and clearly assist the purpose of illustrating the embodiments of the present invention.

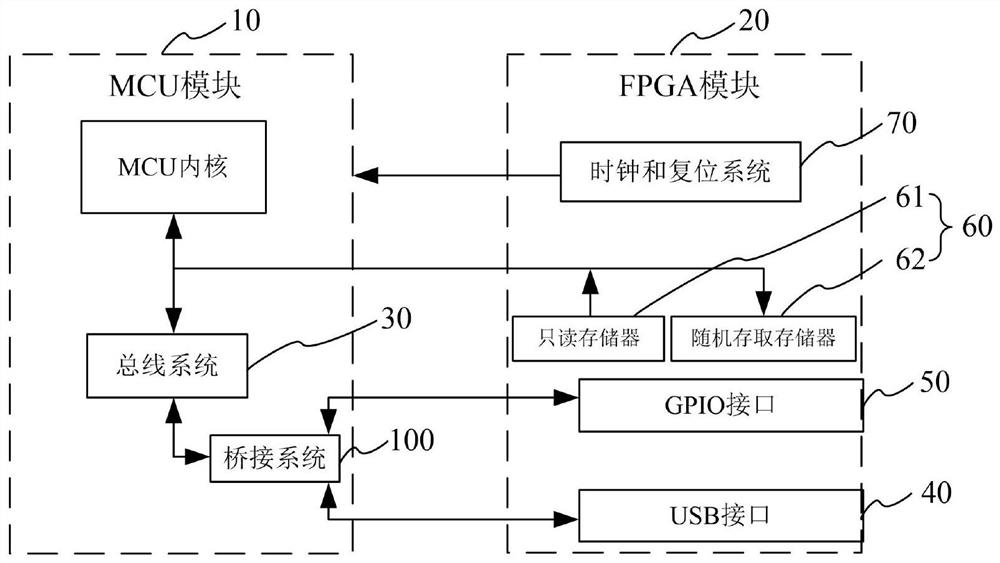

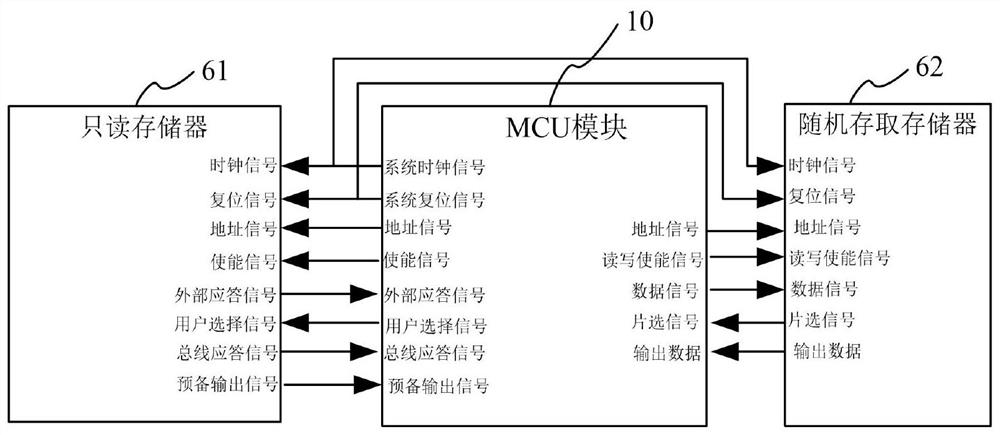

[0031] The embodiment of the present invention relates to a system-level chip supporting USB (Universal Serial Bus) and GPIO (General Input / Output Port) conversion. figure 1 It is a schematic structural diagram of a system-on-a-chip supporting USB and GPIO conversion according to an embodiment of the present invention. see figure 1 , the system level chip of the embodiment of the present invention is mainly based on MCU (microcon...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More