Optimized data rearrangement method based on base-64 two-dimensional FFT architecture

A 64FFT, data optimization technology, applied in the field of signal processing, can solve the problems of less FFT output rearrangement technology, less mature technology, multiple clock cycles, etc., to reduce the number of operation execution cycles and efficient output reordering technology Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment

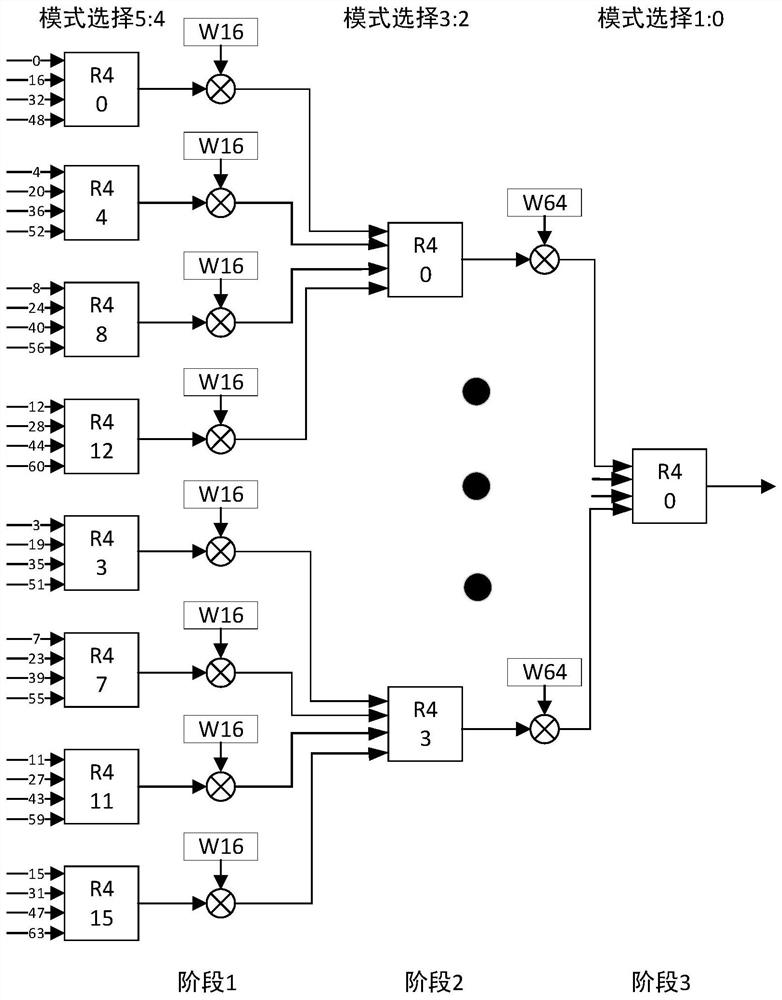

[0063] Such as figure 1 Shown is the parallel unroll architecture of base-64 blocks. There are 16 base 4 units in the first stage, 4 base 4 units in the second stage, and 1 base 4 unit in the third stage. In this architecture, all base 4 blocks are the same. Symbols R40, R44, R48, R412 represent the 0th, 4th, 8th, 1st two radix-4 butterfly blocks and so on. W16 and W64 represent the twiddle factors for the first and second stages. The first stage has 16 twiddle factors and uses read-only memories (ROMs) to store W16. Each ROM contains four twiddle factor values. The second stage consists of four base 4 cells and four ROMs for storing W64. Each ROMs in the second stage consists of 16 twiddle factor values.

[0064] Among the N multipliers in each stage, the first N / 4 multipliers in each stage have the same twiddle factor. So at execution time, these multipliers are removed. Therefore, the first stage has 1 two multipliers instead of 16, and the second stage has 3 multip...

PUM

Login to view more

Login to view more Abstract

Description

Claims

Application Information

Login to view more

Login to view more - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap