Method and device for reducing wafer overlay deviation

A technology for overlaying deviation and wafers, which is applied in photoplate-making process exposure devices, microlithography exposure equipment, photo-engraving process of patterned surfaces, etc., can solve problems such as scrap wafers and deviations, avoid resource waste, reduce The effect of overlay bias

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0039] In order to make the purpose, technical solution and advantages of the present application clearer, the implementation manners of the present application will be further described in detail below in conjunction with the accompanying drawings.

[0040] The "plurality" mentioned herein means two or more. "And / or" describes the association relationship of associated objects, indicating that there may be three types of relationships, for example, A and / or B may indicate: A exists alone, A and B exist simultaneously, and B exists independently. The character " / " generally indicates that the contextual objects are an "or" relationship.

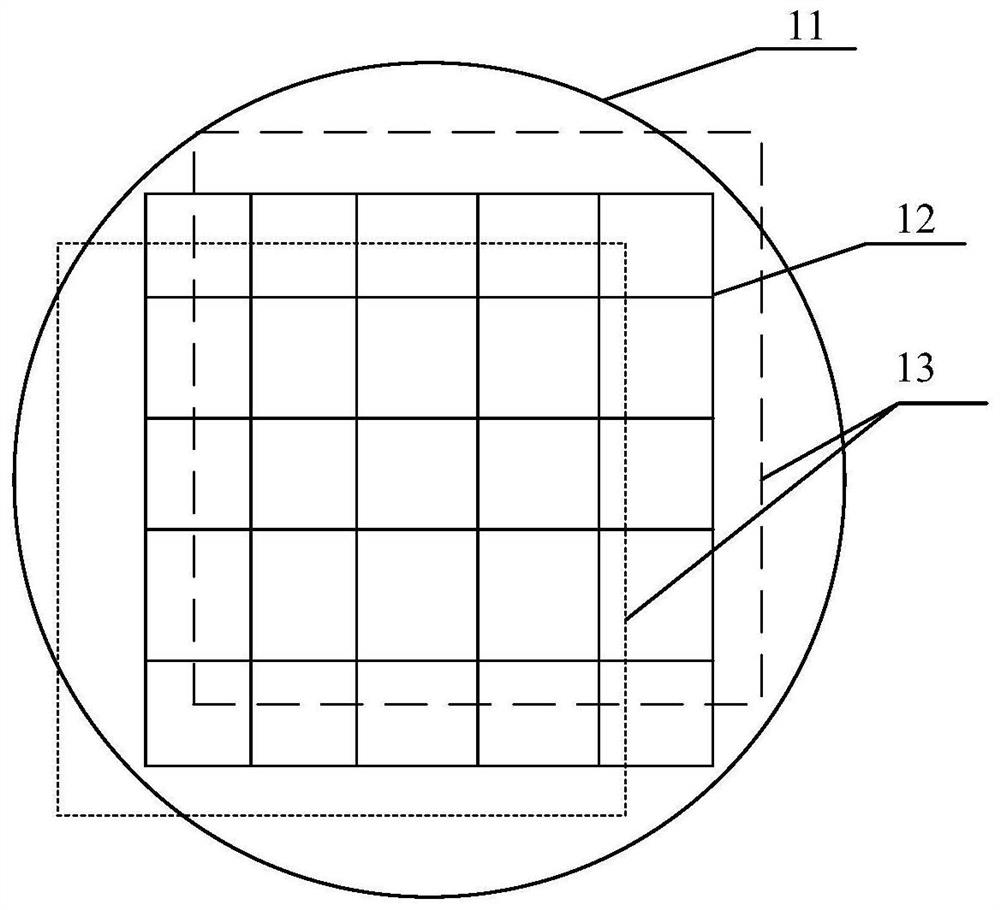

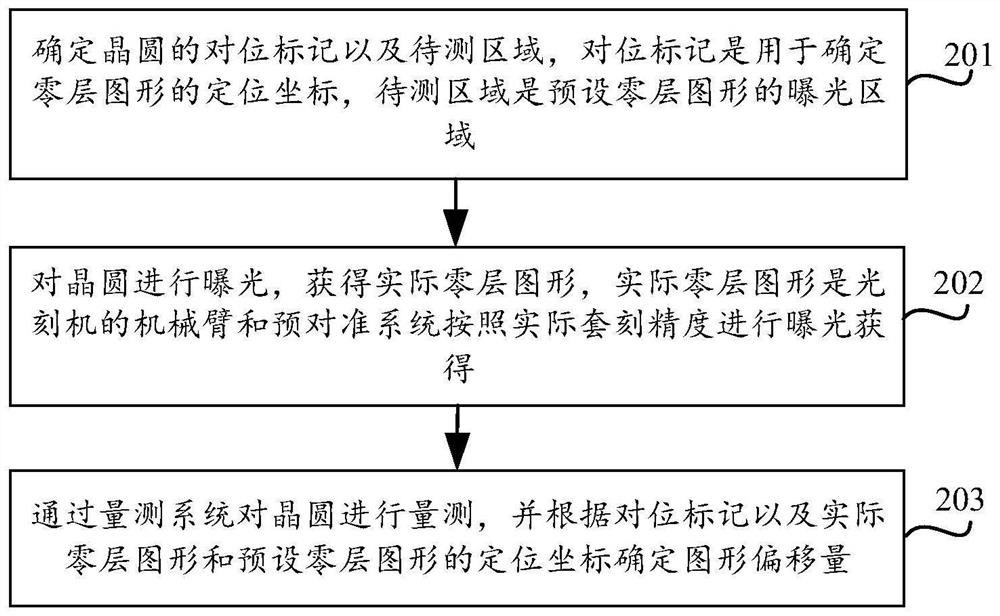

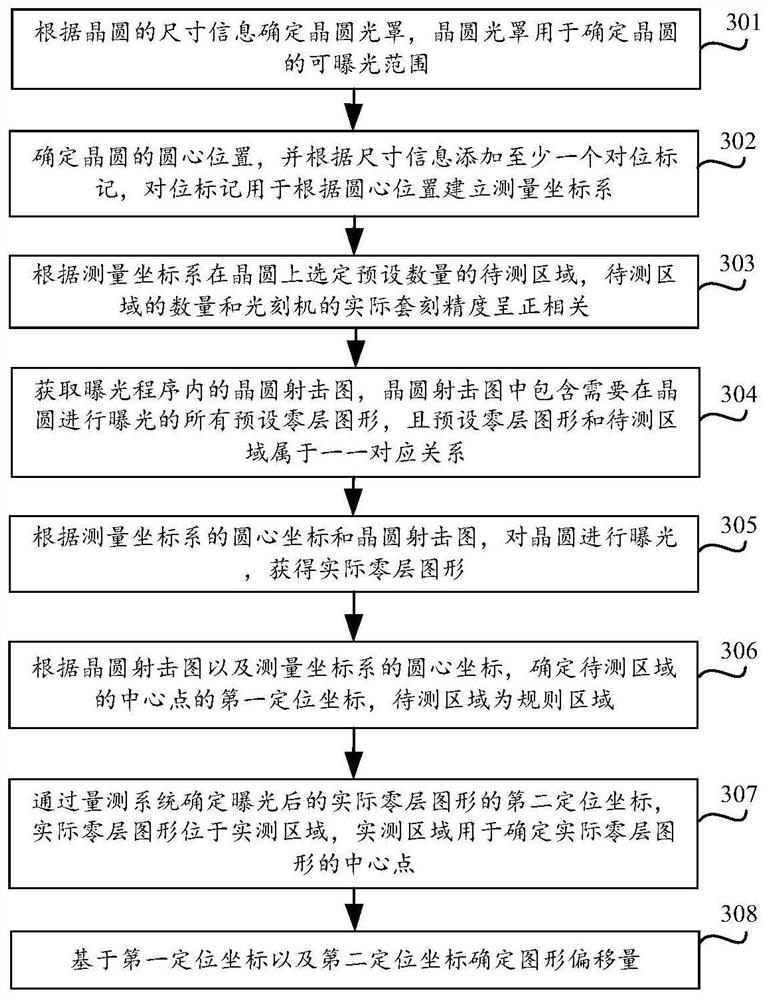

[0041] In related technologies, when a lithography machine performs zero-layer exposure on a wafer (silicon wafer), the imaging position of the circuit pattern on the wafer after exposure depends entirely on the precision of the mechanical transfer arm and the pre-alignment system of the lithography machine and The displacement accuracy of t...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More