Anti-electrostatic protecting structure by NMOS

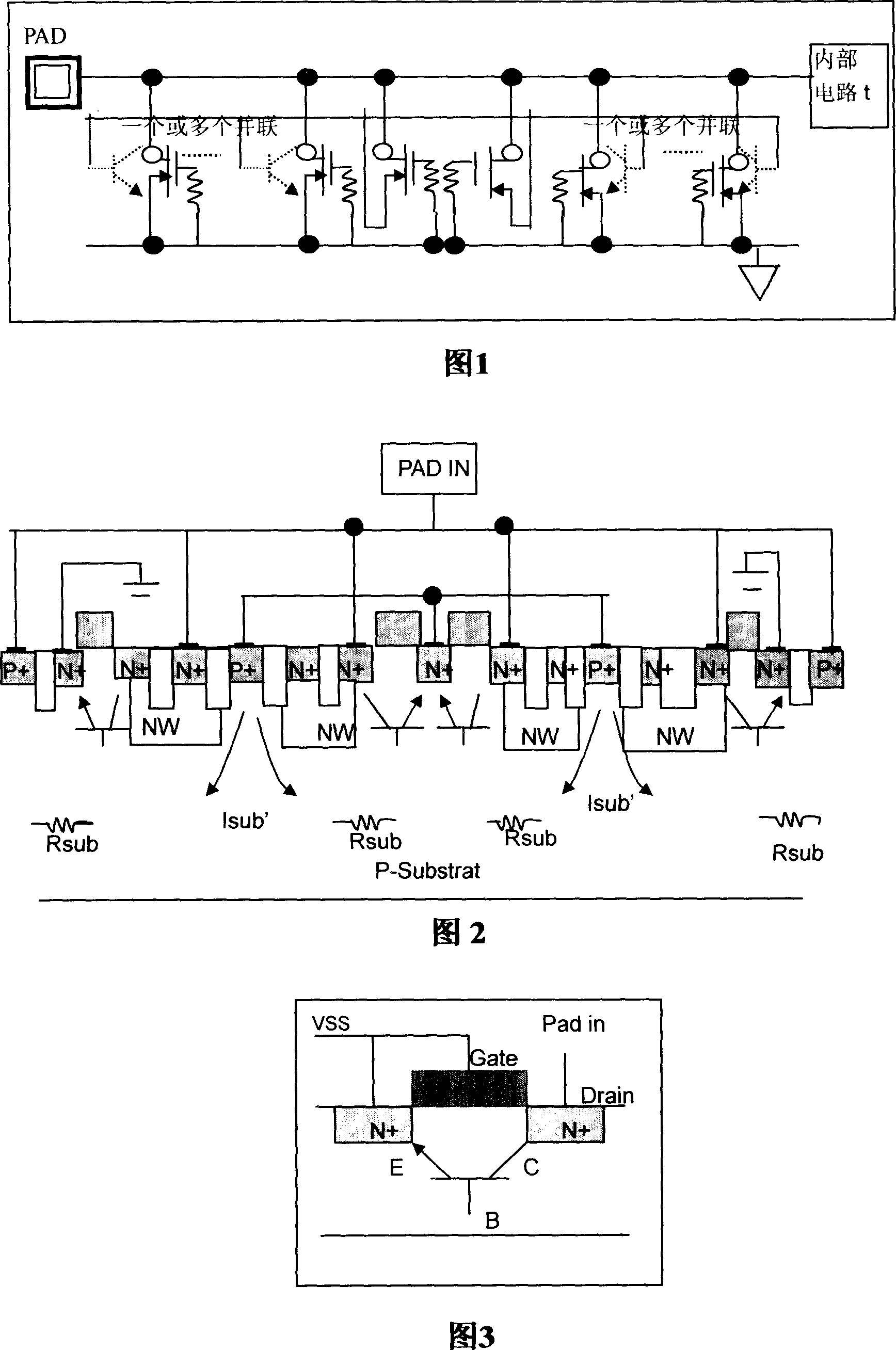

A technology of electrostatic protection and protection structure, which is applied in the direction of emergency protection circuit devices, emergency protection circuit devices, circuits, etc. for limiting overcurrent/overvoltage, and can solve the problem of low ESD protection ability of protection tubes, and solve the problem of opening voltage Different effects

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

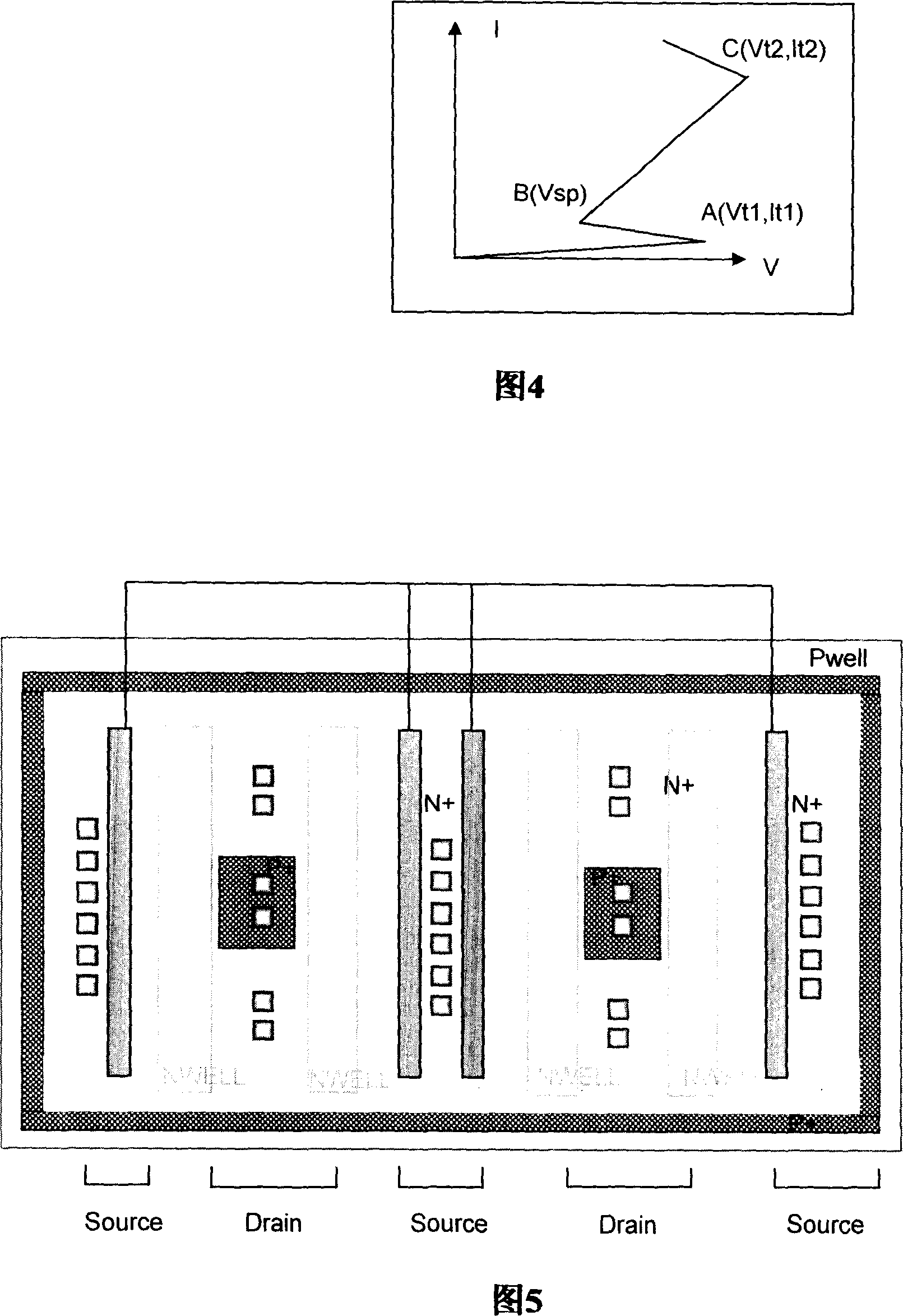

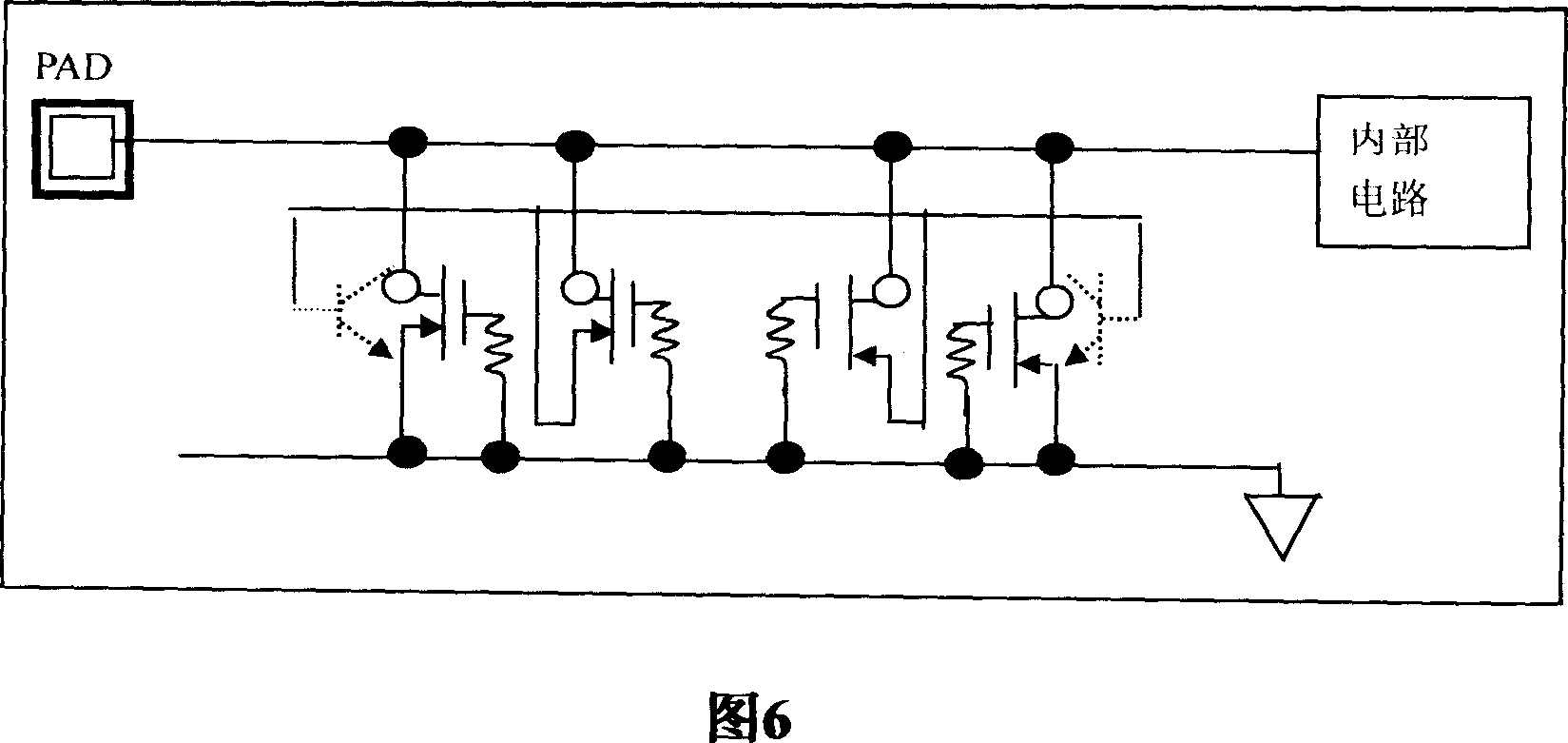

[0012] The present invention will be described in further detail below in conjunction with the accompanying drawings and specific embodiments.

[0013] Firstly set forth the inventive idea of the present invention: firstly, the working state of GGNMOS when ESD takes place is first explained, because the base (substrate) of the NPN triode of NMOS parasitic and the PN junction of the emitter (source) should bleed It is in forward conduction, so the bias voltage applied to the base should be 0.7V higher than that of the emitter. This bias voltage is related to the substrate current and the substrate resistance. When the substrate current is constant, the greater the substrate resistance, the greater the substrate resistance. The greater the bias on the base, the earlier the parasitic NPN can be turned on. However, experiments have proved that when ESD occurs, the NMOS parasitic NPN that is always in the center is turned on first, which may result in a low ESD protection capabil...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More