Apparatus and method for testing conductive bumps

A technology of conductive bumps and testing devices, which is applied in the direction of measuring devices, semiconductor/solid-state device testing/measurement, single semiconductor device testing, etc., and can solve problems such as labor time-consuming, inapplicable product wafer testing and evaluation, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

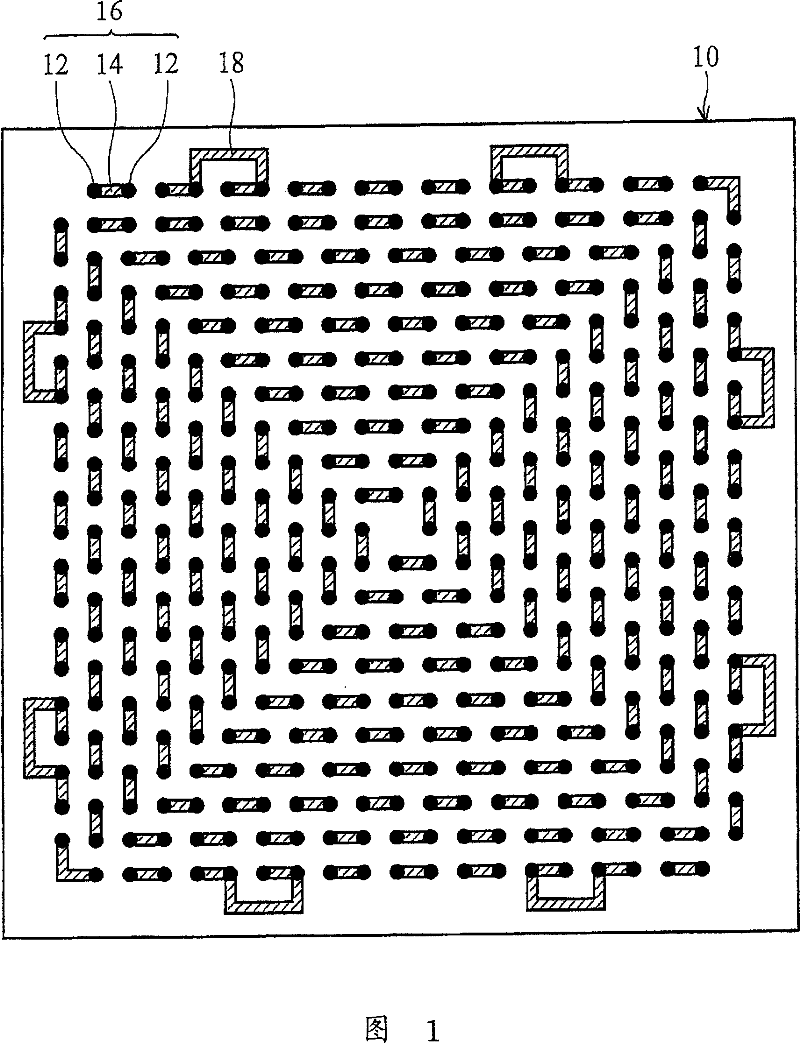

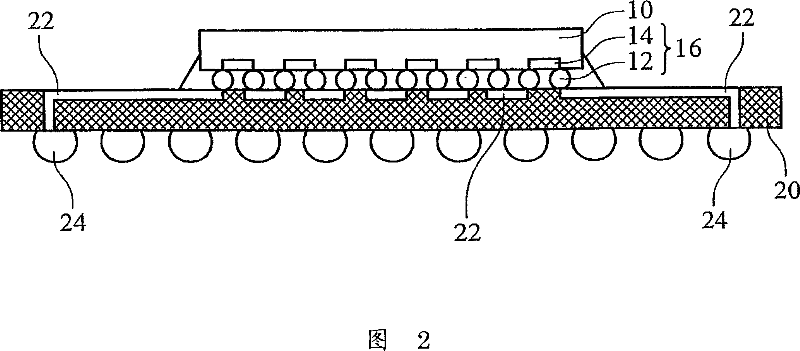

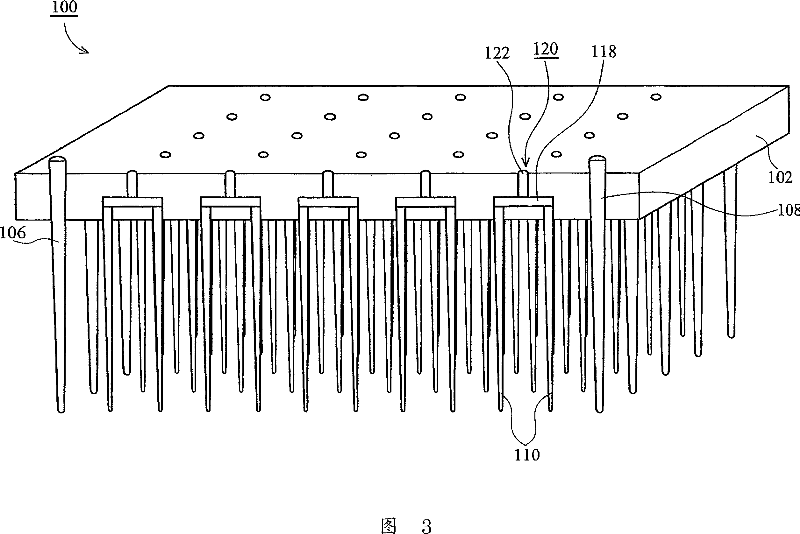

[0031] In order to make the above and other objects, features and advantages of the present invention more comprehensible, a preferred embodiment is specifically cited below, together with the accompanying drawings, and is described in detail as follows:

[0032] An embodiment of the present invention will be described in detail with reference to FIGS. 3 to 7 as follows. 3 to 6 are a series of schematic diagrams for illustrating a conductive bump testing device according to an embodiment of the present invention, and FIG. 7 is a flow chart for illustrating a conductive bump testing method according to an embodiment of the present invention .

[0033] Please refer to FIG. 3 , which illustrates an apparatus 100 for testing conductive bumps. Here, the device 100 includes a support substrate 102 in which a plurality of test probes are formed. The support substrate 102 includes an insulating material such as ceramic material, epoxy, resin, polyimide, FR4 glass fiber, or polymer. ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More