Trench isolation technology and method

一种沟渠、工艺的技术,应用在形成沟渠隔离结构领域,能够解决提高锗脱气等问题

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

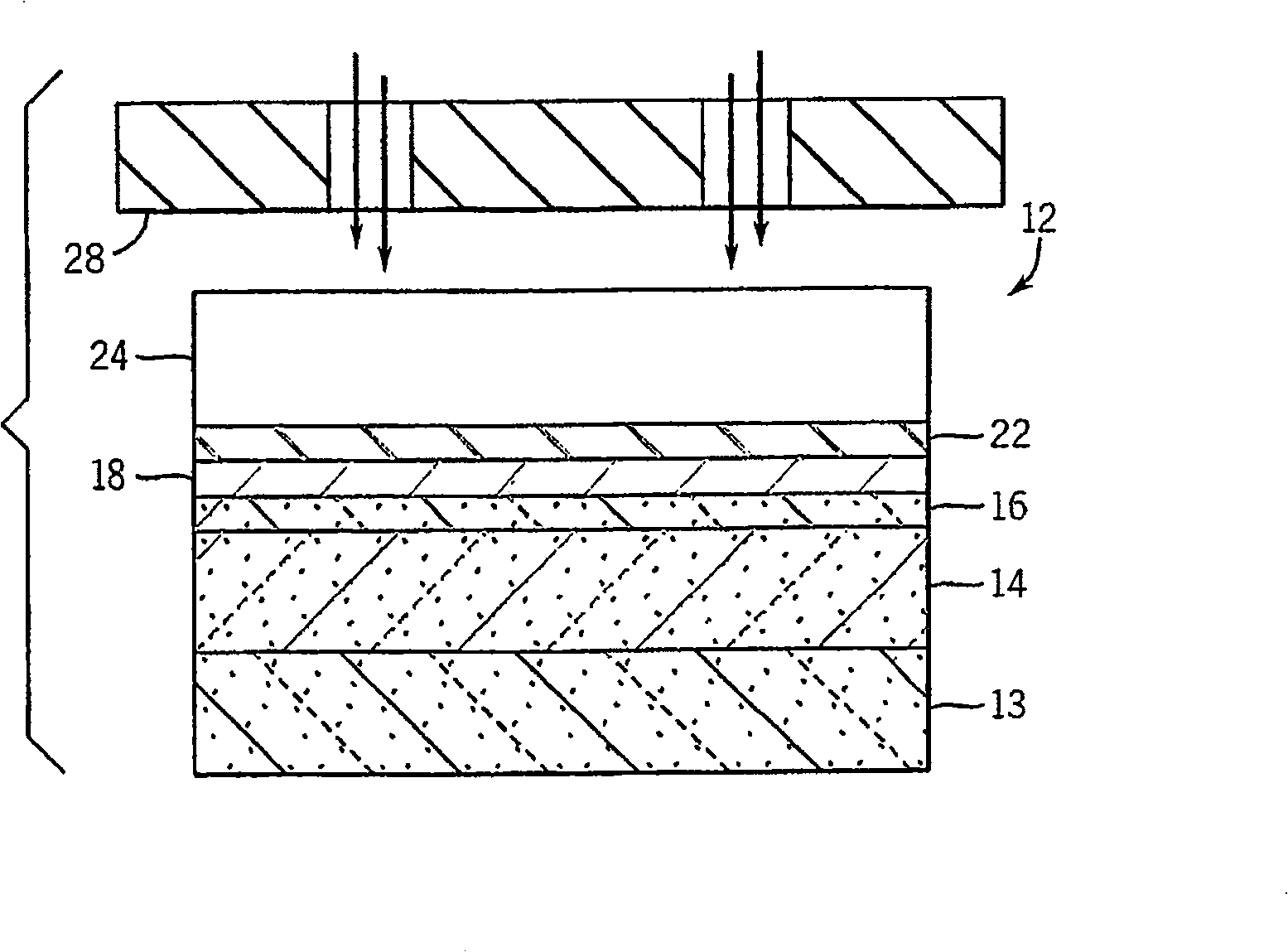

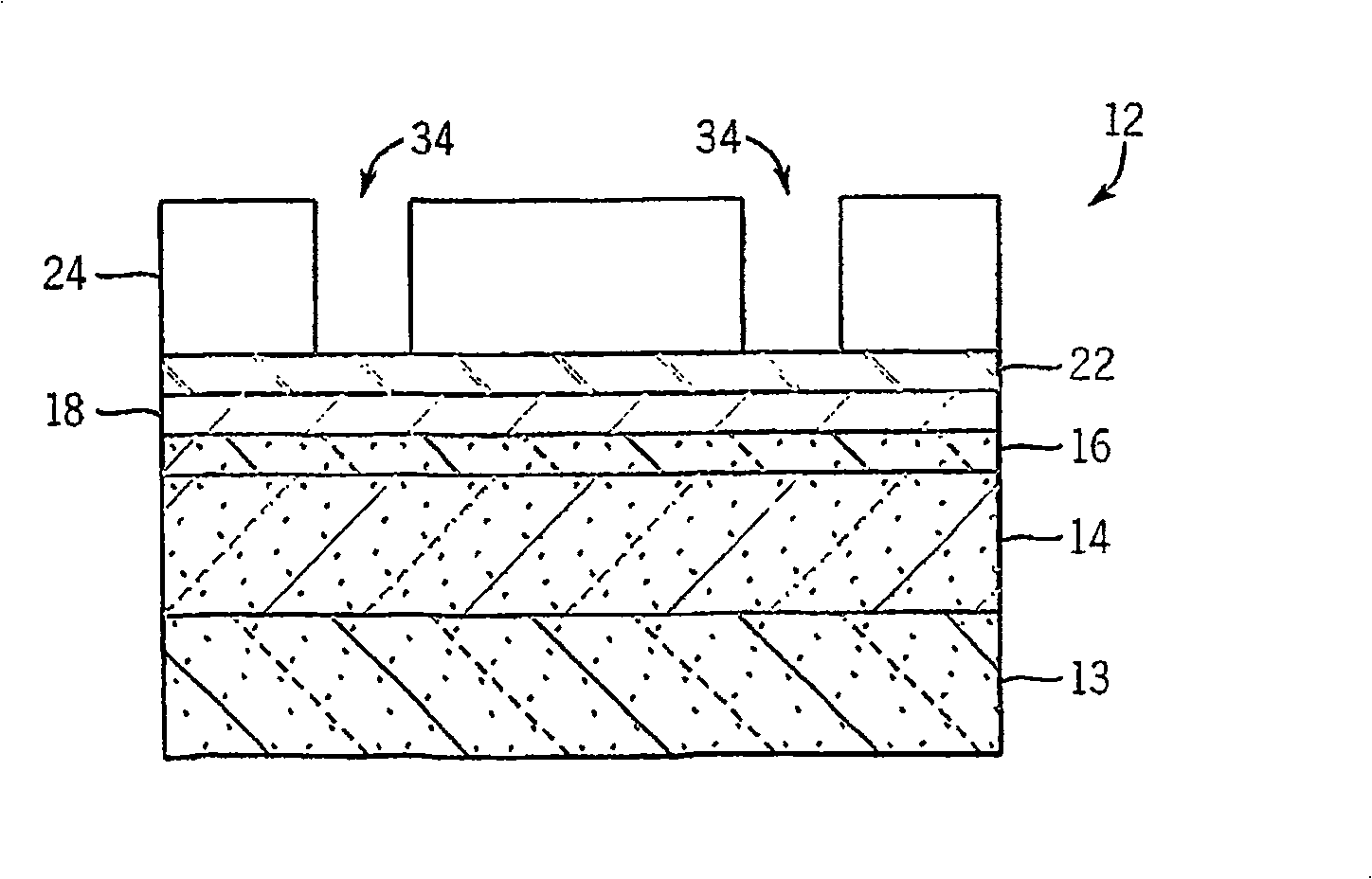

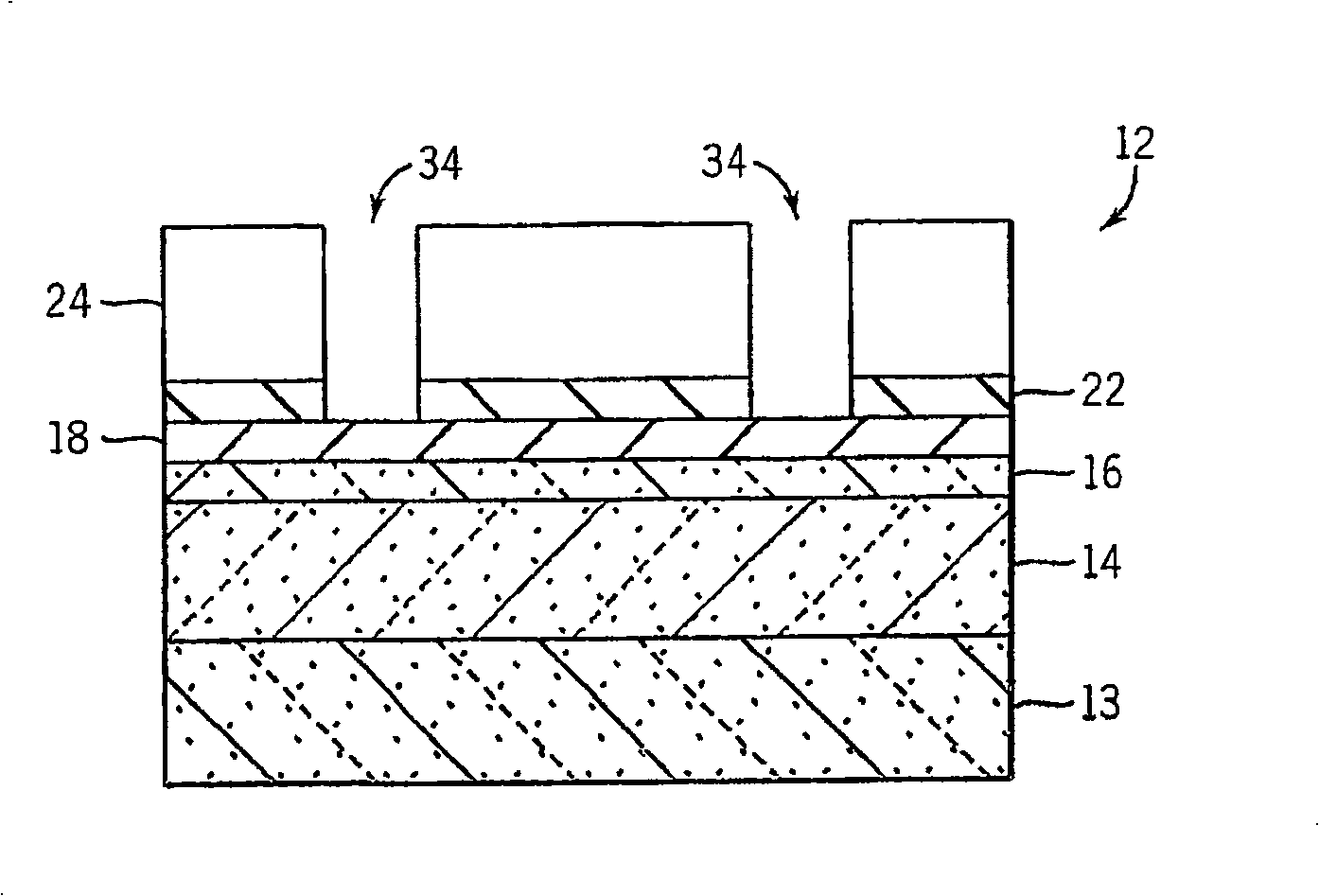

[0036] Figure 1 to Figure 9 A method of manufacturing an integrated circuit (IC) is described according to an exemplary embodiment. Such as Figure 1 to Figure 9The method can reduce the germanium degassing and out-diffusion problems of the silicon germanium layer or structure. This process can be used in shallow trench isolation (STI), or any process that requires a liner oxide and uses germanium or other substances that have a high temperature outgassing tendency. Advantageously, the pad oxide can be formed at low temperature and provides a high quality oxide with good compatibility. Such as Figure 1 to Figure 9 In the described embodiment, the low temperature process refers to a process performed at a temperature lower than about 700°C.

[0037] refer to Figures 1 to 9 , which illustrates a cross-sectional view of portion 12 of an integrated circuit (IC). Part 12 is based on process 100 ( Figure 9 ) to form a shallow trench isolation (STI) structure. Portion 12 ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com