Method for packaging small-lot chips

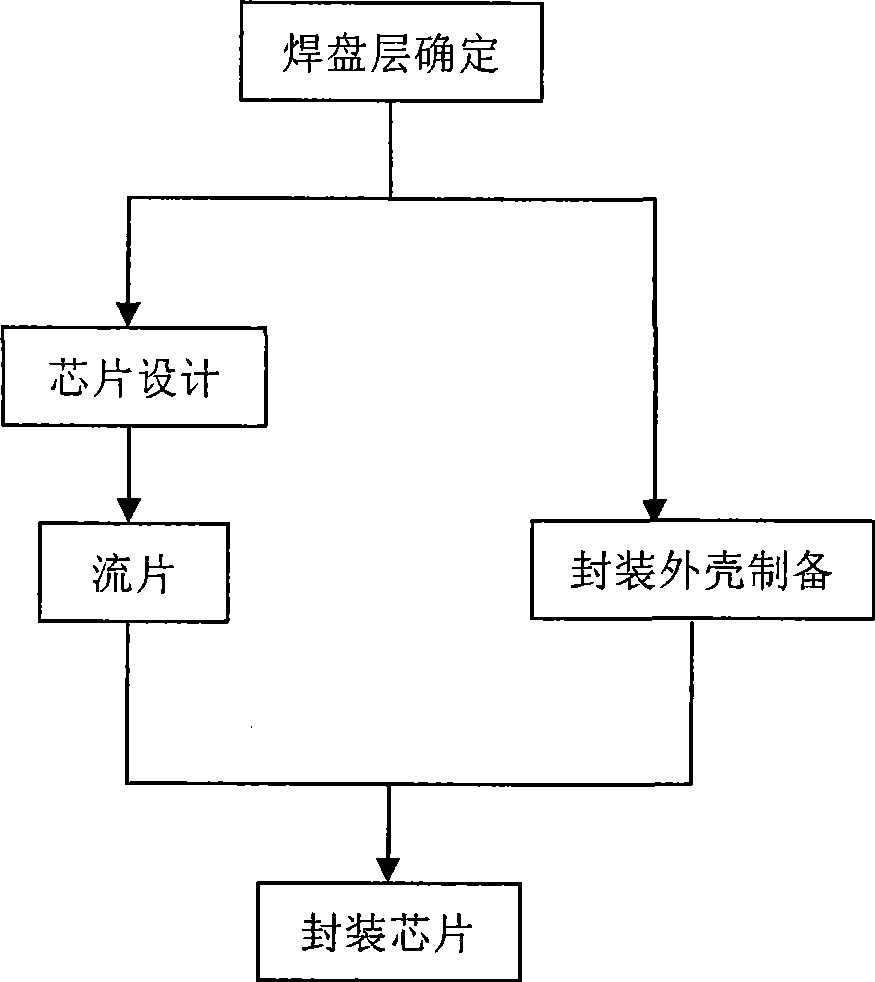

A small-batch, chip-based technology, which is applied in the manufacture of electrical components, circuits, semiconductors/solid-state devices, etc., can solve the problems of reducing the cost of small-batch chip packaging and high packaging costs, and is conducive to popularization and use, reducing packaging design links and costs Reduced effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0049] In order to make the object, technical solution and advantages of the present invention clearer, the present invention will be described in further detail below in conjunction with specific embodiments and with reference to the accompanying drawings.

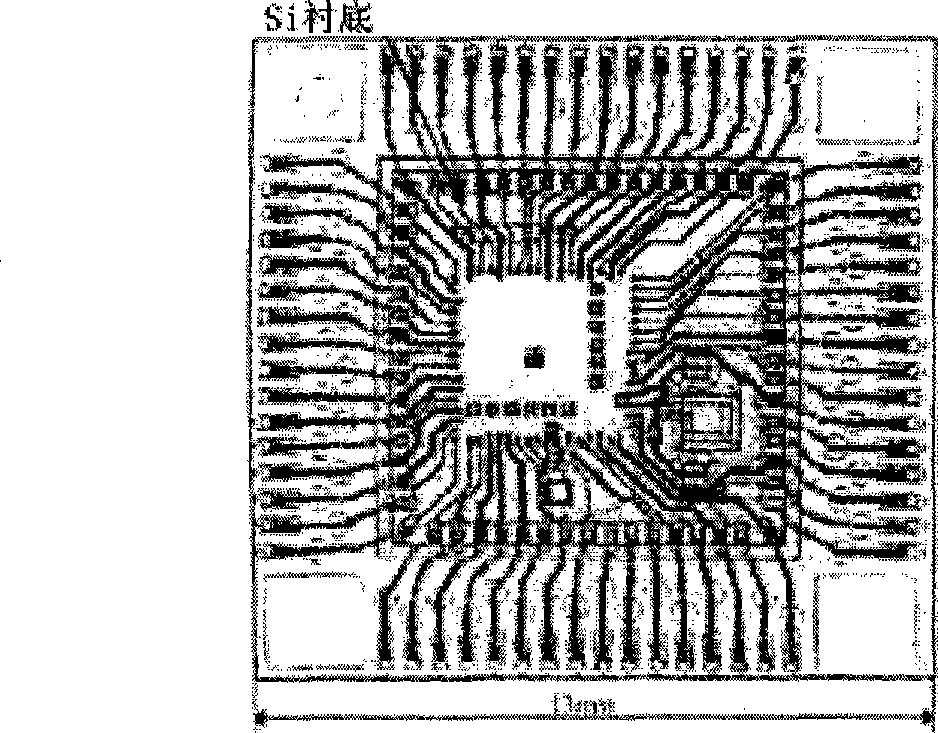

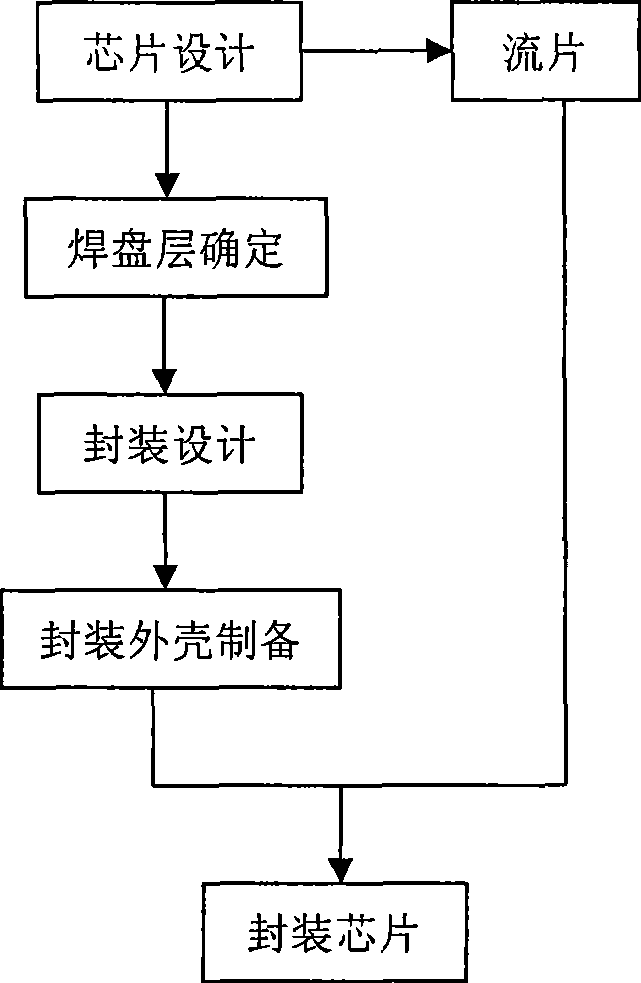

[0050] The semiconductor industry has extremely high requirements on the environment and production accuracy. Using ultra-clean rooms and expensive equipment, chip foundries (foundry factories) and packaging manufacturers have invested hugely, often tens of millions to billions of dollars, designed for large-scale production services. In fact, in addition to commercial large-scale chips, research institutes and many companies need to produce and package small-batch chips for scientific research or new product development. These chips are small in quantity (often only dozens to hundreds of pieces) and have many varieties. Not only do they require separate tape-outs, but they often use different high-end packaging forms. T...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More