On-line error correcting device for fault by parity check code and method thereof

A technology of parity check code and error correction device, which is applied in the field of online testing and can solve problems such as huge redundancy overhead.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

specific Embodiment approach 1

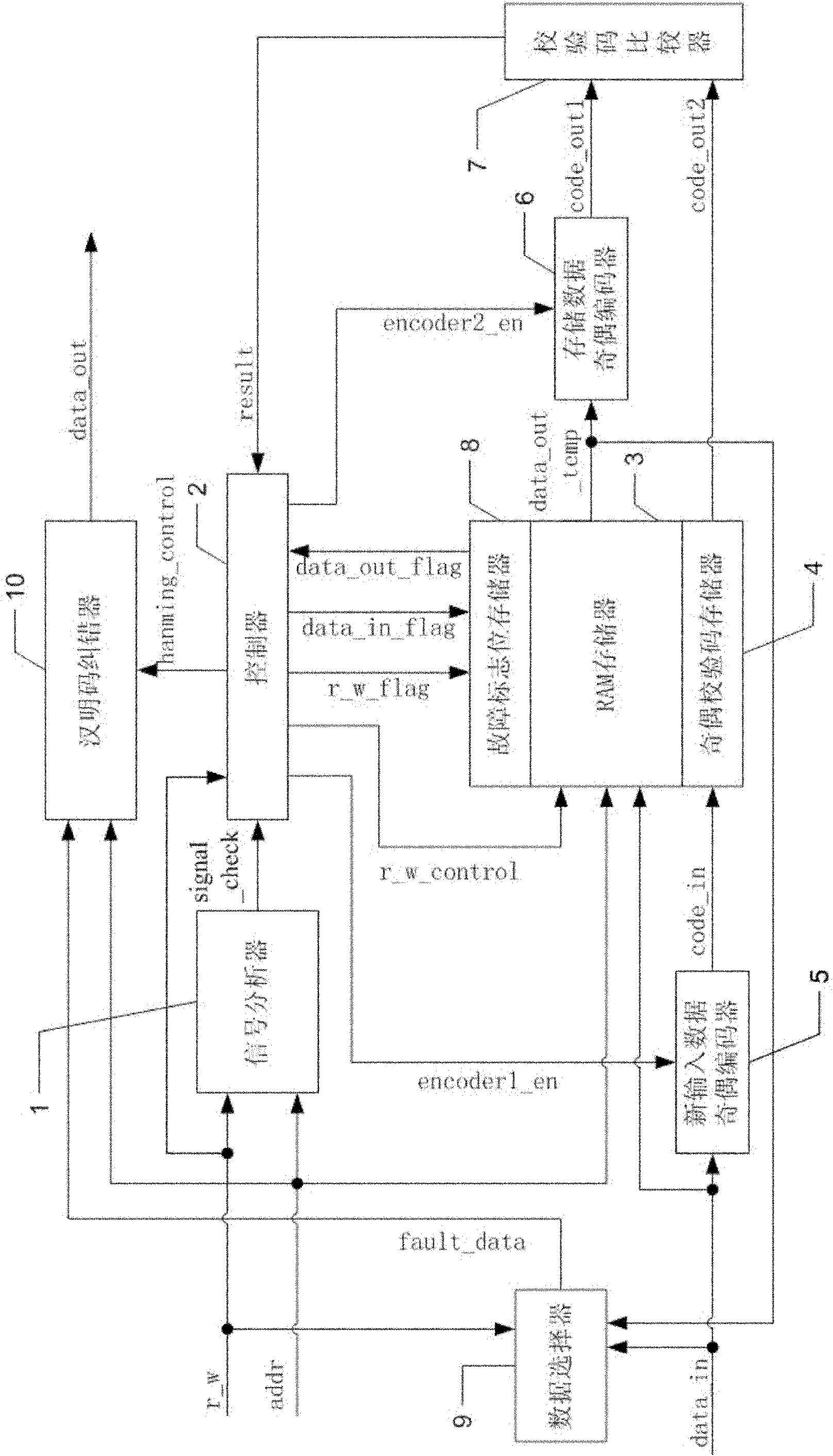

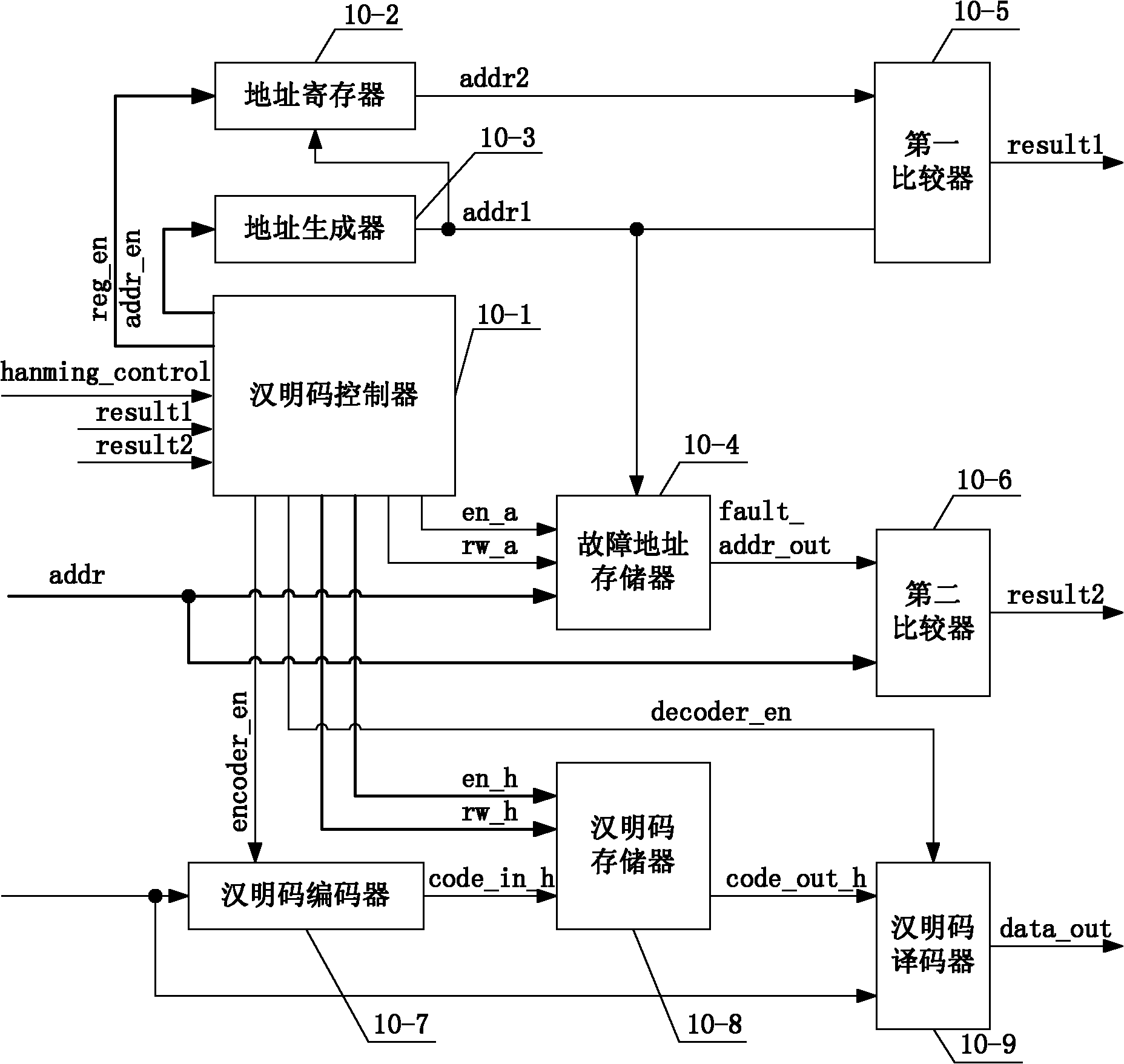

[0064] Specific implementation mode one: the following combination Figure 1 to Figure 3 Describe this embodiment mode, a kind of using parity check code to carry out fault online error correction device described in this embodiment mode, it comprises signal analyzer 1, controller 2, RAM memory 3, parity check code memory 4, new input data parity Encoder 5, stored data parity encoder 6, check code comparator 7, fault flag memory 8, data selector 9 and Hamming code error corrector 10,

[0065] The read-write control signal r_w and the address signal addr are sent to the signal analyzer 1, and the read-write control signal r_w is sent to the controller 2 and the data selector 9 at the same time, and the address signal addr is sent to the RAM memory 3, the parity checker at the same time Code memory 4, fault flag bit memory 8 and Hamming code error corrector 10,

[0066] The signal analyzer 1 outputs the new signal input flag signal_check to the controller 2, the controller 2 ou...

specific Embodiment approach 2

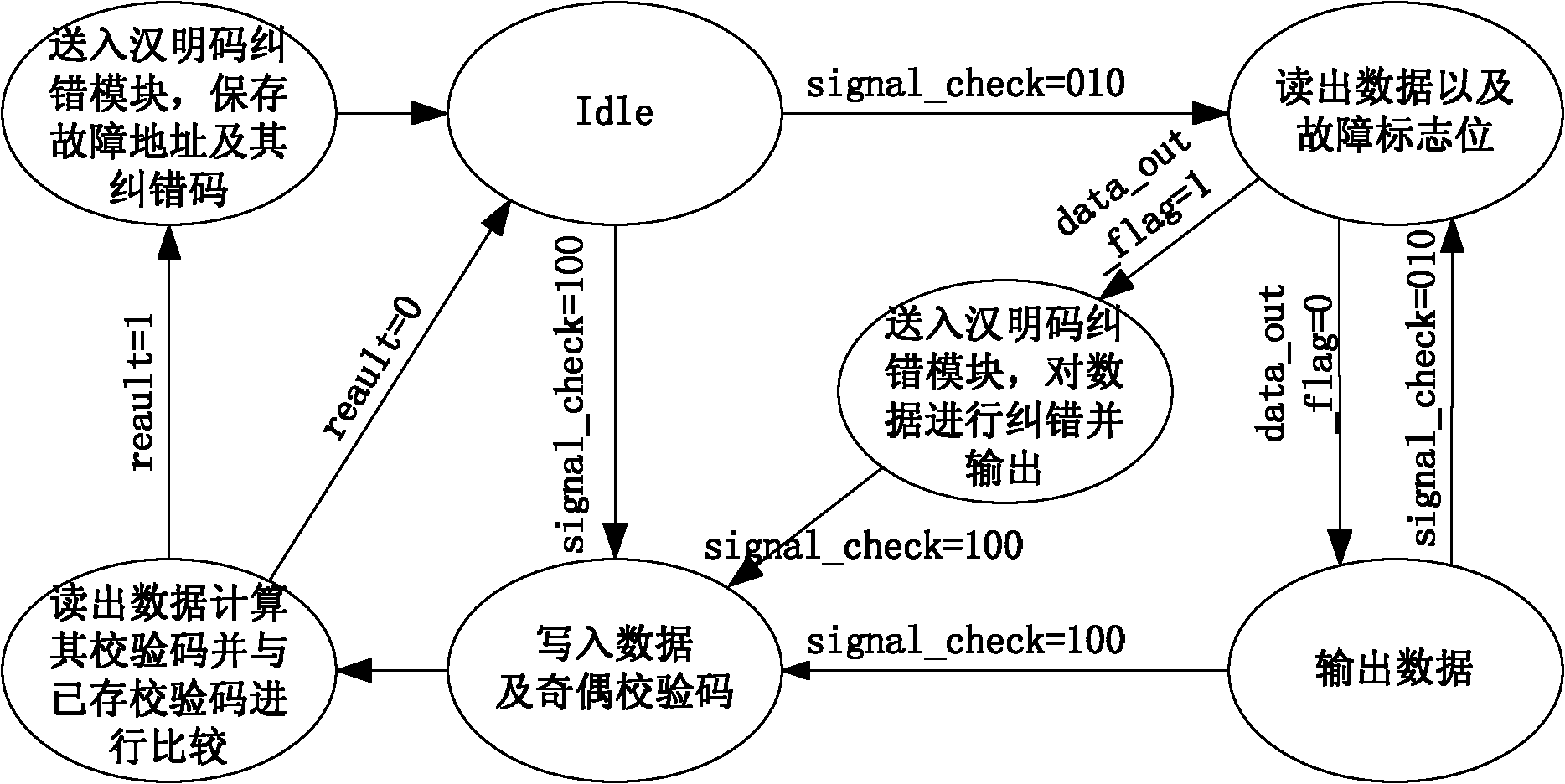

[0078]Specific Embodiment 2: Based on the online error correction method of a faulty online error correction device using parity codes described in Embodiment 1, it is characterized in that the method is divided into two parts: reading and writing.

[0079] The detection method during write operation includes the following steps:

[0080] Step 1, the signal analyzer 1 detects and analyzes whether there is a new write signal input,

[0081] If it is detected that there is a new write signal input, the signal analyzer 1 will output the new signal input flag signal_check=(100) B , and then perform step 2; if no new write signal input is detected, signal analyzer 1 identifies signal_check=(000) with its output new signal input B , continue to detect;

[0082] Step 2, the data selector 9 selects the new input data data_in as the output of the error data fault_data, and as the input of the Hamming code error corrector 10,

[0083] Step 3, controller 2 receives new signal input fl...

specific Embodiment approach 3

[0116] Specific embodiment three: this embodiment further explains embodiment two, the process that Hamming code encoder 10-7 encodes during writing operation is:

[0117] The input data is: a 0 a 1 …a k-1 , the Hamming code data is: H 0 h 1 …H k-1 ;

[0118] Step a, construct the parity check matrix H of the optimal odd-weight code:

[0119]

[0120] Each element h in check matrix H i,j =0 / 1, n is the codeword of the error correction code, k is the length of the information bit, and satisfies: nn-k -1;

[0121] Step b, calculate the check digit:

[0122] H 0 = a 0 · h 00 ⊕ a 1 · h 01 ⊕ . . . ⊕ a k - 1 · h 0 , ...

PUM

Login to view more

Login to view more Abstract

Description

Claims

Application Information

Login to view more

Login to view more - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap