Method for testing a partially assembled multi-die device, integrated circuit die and multi-die device

An integrated circuit and multi-die technology, applied in the direction of measuring electricity, measuring devices, measuring electrical variables, etc., can solve problems such as limited test flexibility

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

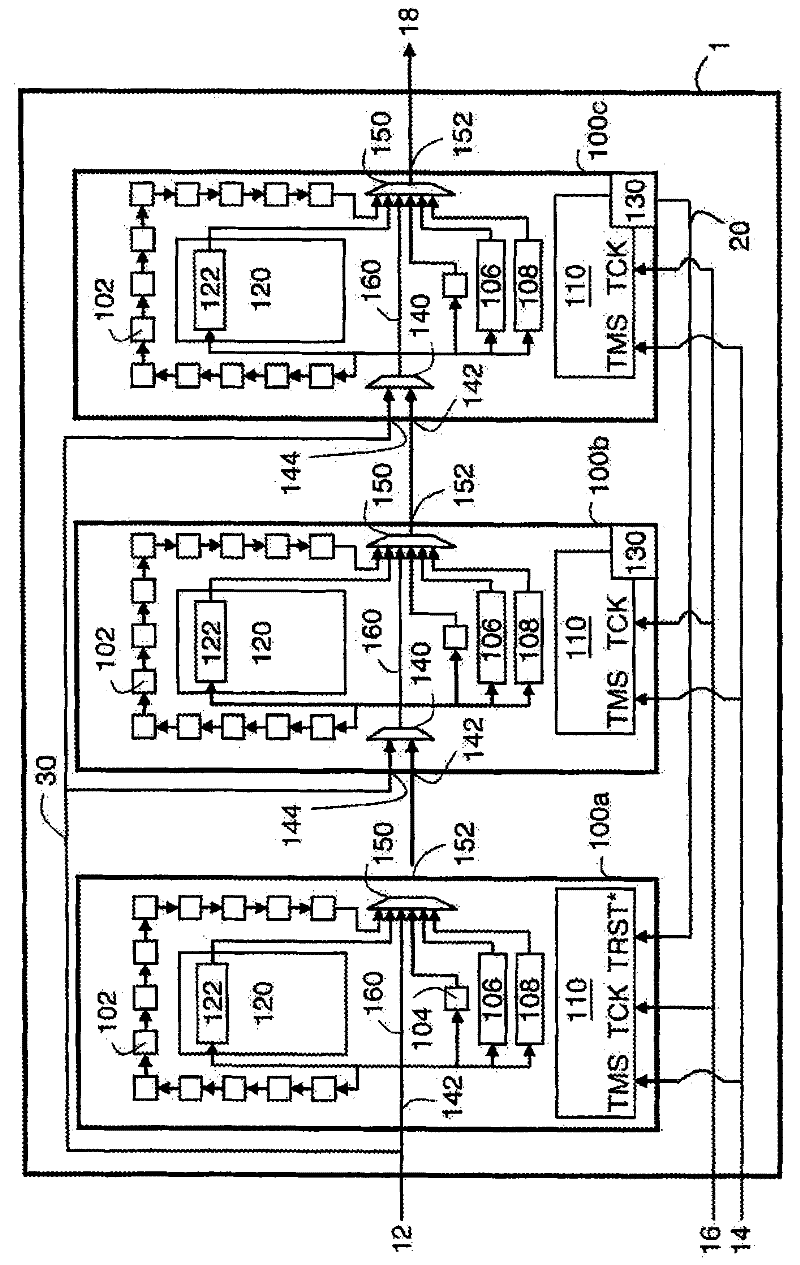

[0041] figure 1 An embodiment of a multi-die device disclosed in WO2007 / 010493 is shown that can be used to test isolated dies as well as modules as a single device in a JTAG compliant manner once the assembly of the SiP has been completed. As a non-limiting example only, device 1 is shown with 3 dies 100a-c on a carrier (not shown). The global structure of the finished multi-chip device of the present invention can be compared with figure 1 The devices shown are substantially similar, with differences discussed in more detail below.

[0042] Device 1 has multiple system interconnects, including device level TDI 12 , device level test mode select (TMS) input 14 , device level test clock (TCK) input 16 and device level TDO 18 . figure 1 Each of the illustrated IC dies 100 a - c is represented by a test apparatus comprising test access ports (TAPs) each having a TAP controller 110 . The TAPs of die 100a-c may each include a plurality of shift registers, such as a boundary sca...

PUM

Login to view more

Login to view more Abstract

Description

Claims

Application Information

Login to view more

Login to view more - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap