Method for manufacturing master board and TFT (Thin Film Transistor) array substrate

A manufacturing method and array substrate technology, applied in semiconductor/solid-state device manufacturing, optics, instruments, etc., can solve the problems of product qualification rate and yield reduction, TFT array substrate electrostatic breakdown, potential difference, etc., to improve the qualification rate and Yield rate, the effect of reducing electrostatic breakdown phenomenon

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

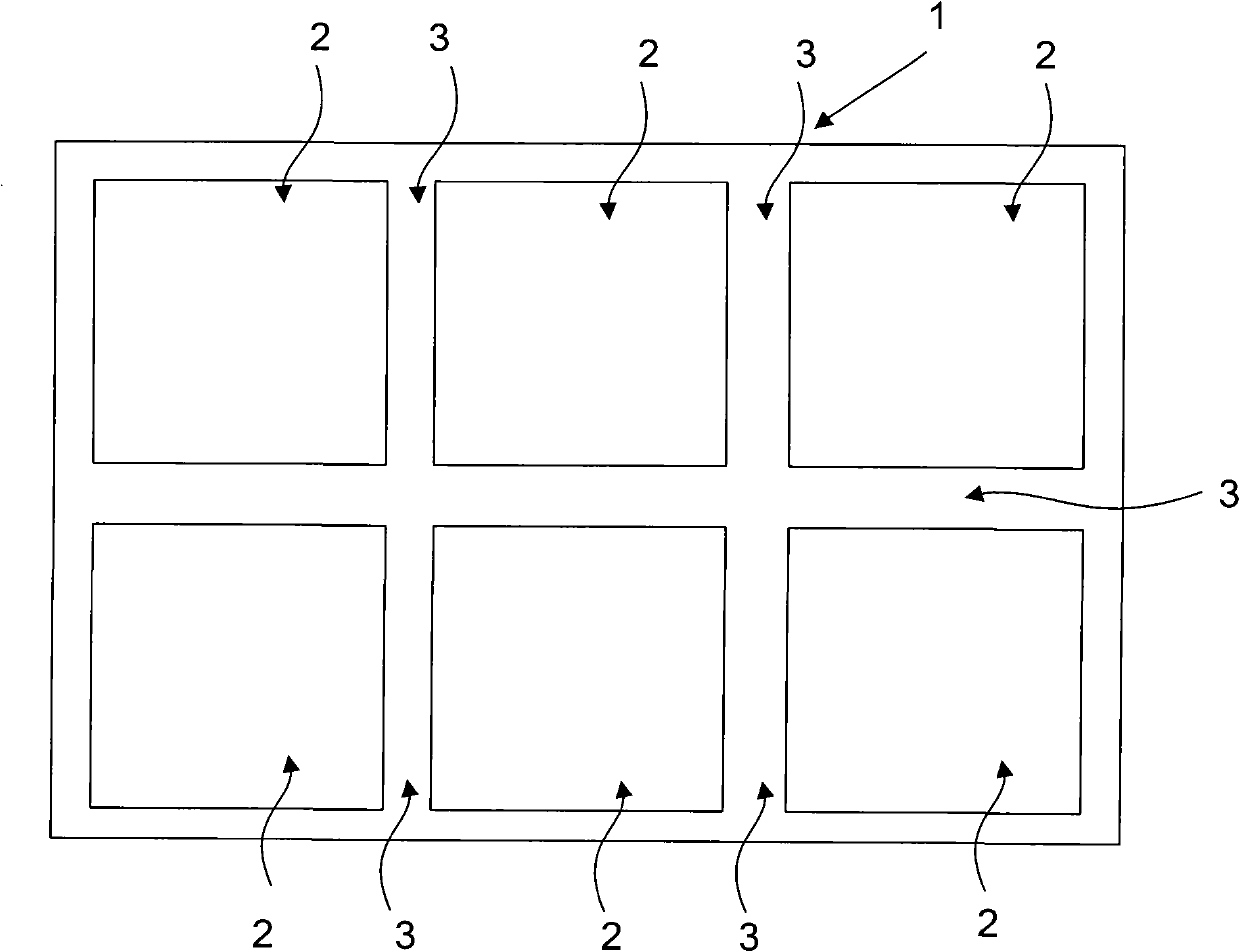

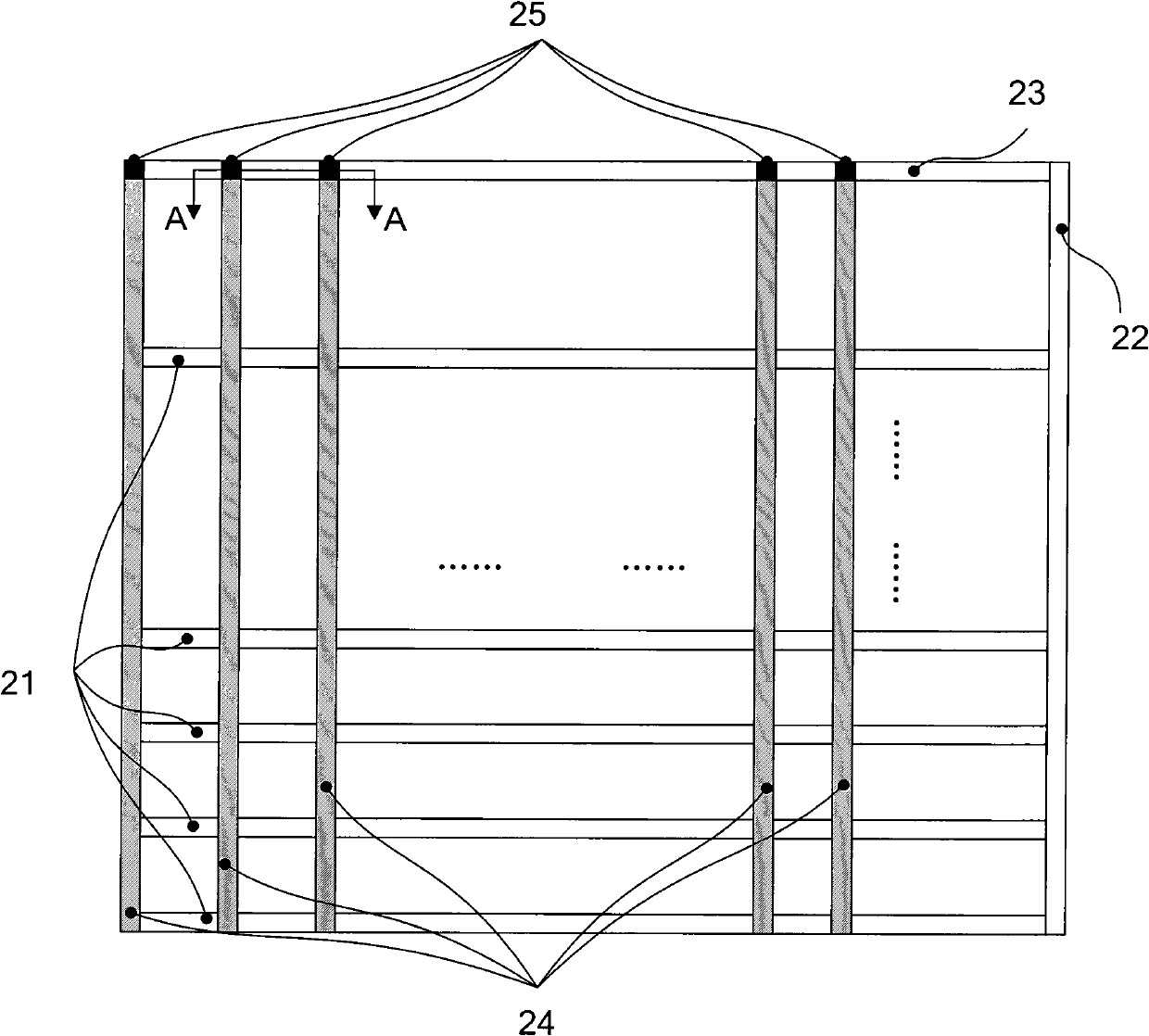

[0047] An embodiment of the present invention provides a motherboard, such as figure 1As shown, the motherboard in this embodiment includes a substrate 1 having at least one display area 2, and the periphery of the display area 2 is provided with a pre-cut area 3. After the TFT array process is completed, it is necessary to cut The region 3 is cut, and each display region 2 is cut, and each display region 2 finally forms a complete TFT array substrate. In order to reduce the electrostatic breakdown phenomenon that occurs during the manufacturing process of the TFT array substrate, the pre-cut areas on the adjacent sides of each display area of the motherboard in the embodiment of the present invention are respectively provided with electrically connected gate and data communication lines, and The gate connecting lines are electrically connected to the gate scanning lines in the corresponding display area, and the data connecting lines are electrically connected to the data s...

Embodiment 2

[0078] An embodiment of the present invention provides a motherboard, the overall structure of the motherboard is the same as figure 1 Similarly, it includes a substrate with at least one display area, and a pre-cut area is provided between two adjacent display areas on the substrate. After the TFT array process is completed, it needs to be cut in the pre-cut area, and each Each display area is cut, and each display area finally forms a complete TFT array substrate.

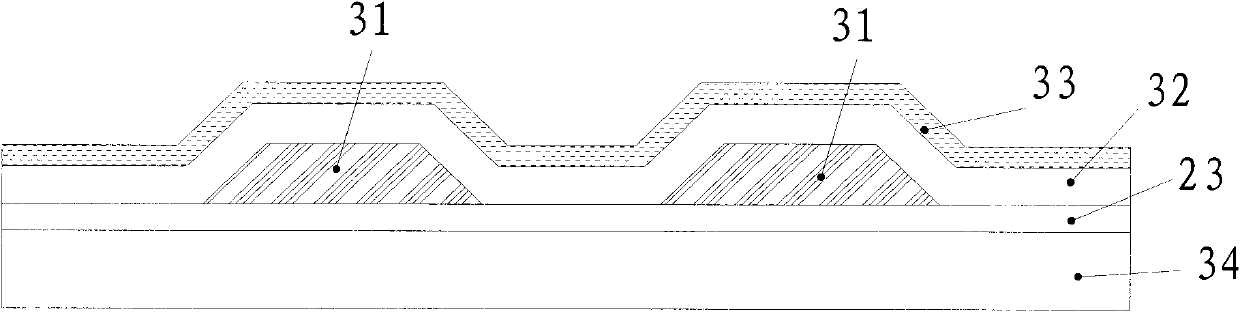

[0079] In the embodiment of the present invention, in order to reduce the electrostatic breakdown phenomenon that occurs during the manufacturing process of the TFT array substrate, a solution similar to that of embodiment 1 is adopted to electrically connect the two metal layers so that their potentials are generally equal. The following takes one of the display areas as an example to describe its specific electrical connection method in detail. Figure 6 is a schematic diagram of one of the display areas, Fi...

Embodiment 3

[0108] An embodiment of the present invention provides a motherboard, the overall structure of the motherboard is the same as figure 1 Similarly, it includes a substrate with at least one display area, and a pre-cut area is provided between two adjacent display areas on the substrate. After the TFT array process is completed, it needs to be cut in the pre-cut area, and each Each display area is cut, and each display area finally forms a complete TFT array substrate.

[0109] In the embodiment of the present invention, in order to reduce the electrostatic breakdown phenomenon that occurs during the manufacturing process of the TFT array substrate, a solution similar to that of embodiment 1 is adopted to electrically connect the two metal layers so that their potentials are generally equal. The following takes one of the display areas as an example to describe its specific electrical connection method in detail. Figure 10 is a schematic diagram of one of the display areas, F...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More