Method for polishing silicon through hole wafer and polishing combination for the same

A polishing composition and through-silicon via technology, applied in the field of polishing, can solve the problems of excessive difference in removal rate, decrease in silicon removal rate, increase in polishing rate of silicon and conductive materials, etc., and achieve reliable results

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0024] The polishing method of the TSV wafer of the present invention includes polishing the surface of the TSV wafer with the above-mentioned polishing composition of the present invention. During the polishing process, the polishing composition flows to the polishing pad and the TSV wafer at a flow rate, while the TSV wafer is brought into contact with the polishing pad by applying a polishing pressure, and both have a rotational speed, so that the TSV wafer is in contact with the polishing pad. The TSV wafer is polished.

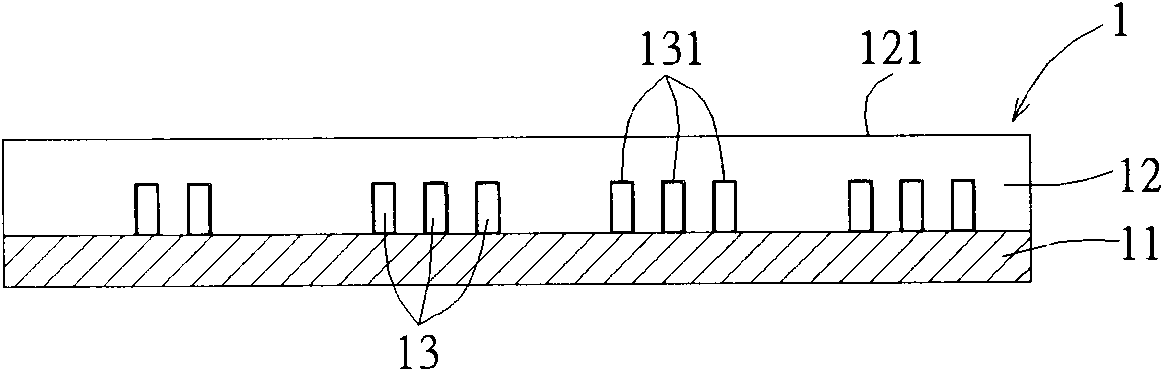

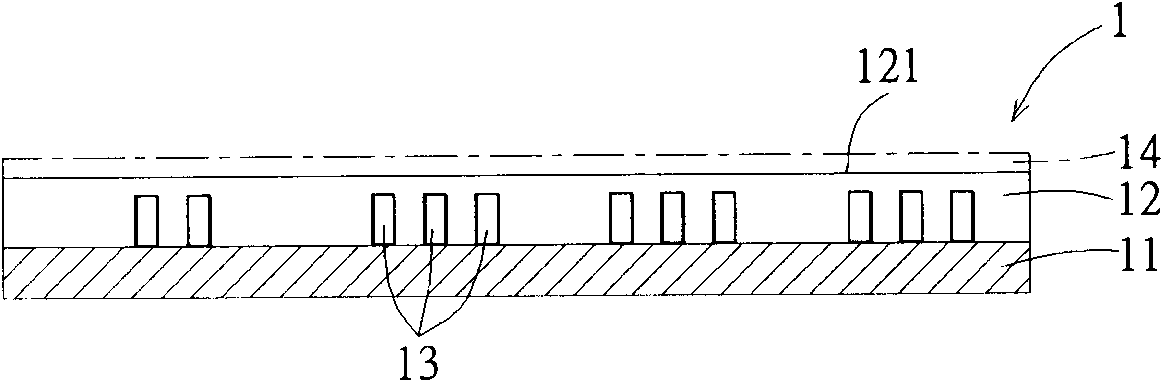

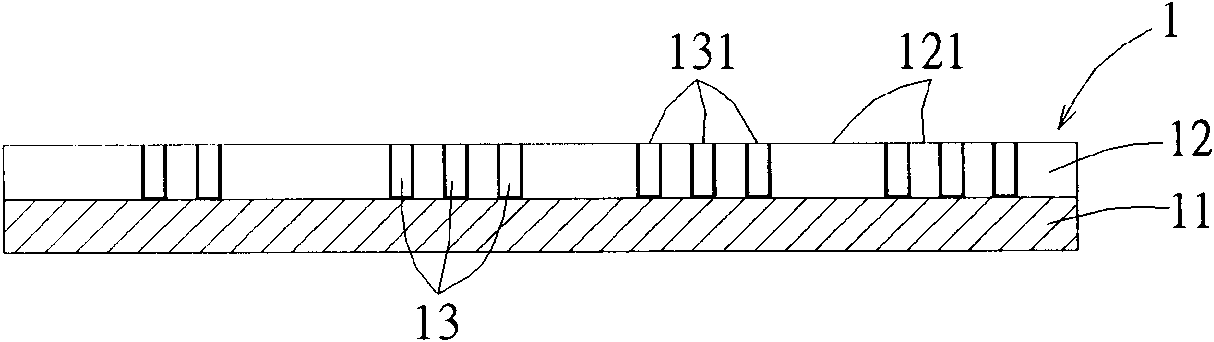

[0025] It must be explained that the above-mentioned "surface of the TSV wafer" means a surface of the TSV wafer away from the integrated circuit layer 11 thereof, which may be the surface 121 of the silicon wafer layer (eg figure 1 shown) or the top surface 131 (such as image 3 shown).

[0026] In this mode of operation, the removal rates of conductive material and silicon from TSV wafers can be achieved simultaneously above, even above, more or e...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com