Copper subsequent interconnection technique

A process and back-end technology, which is applied in the field of copper back-end interconnection technology, can solve the problems of reducing product yield, increasing leakage current, and narrowing the window, so as to improve the anti-etching ability, reduce the increase of leakage current, and improve The effect of yield

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Example Embodiment

[0025] The specific embodiment of the present invention will be further described below in conjunction with accompanying drawing:

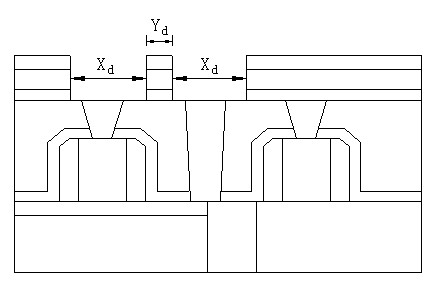

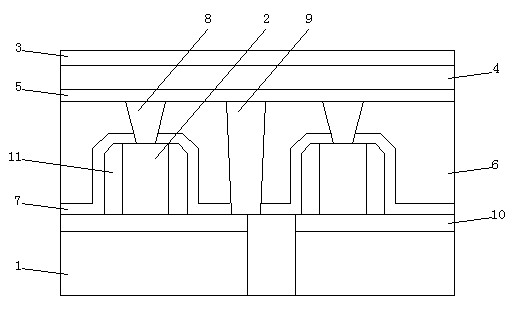

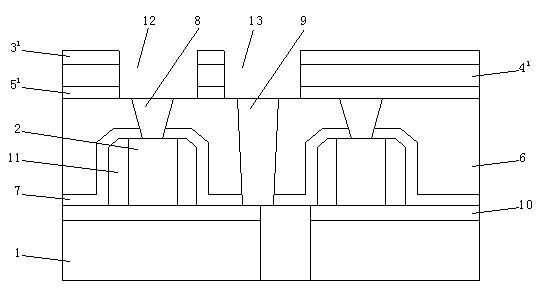

[0026] like Figure 2-7 As shown, the present invention provides a copper back-end interconnection process. In a process of 32 nanometers and below, a substrate 1 prepared by a Damascene process is provided with a gate 2 of a semiconductor device and implanted in the substrate 1. The source / drain doped region 10, and the contact hole etch barrier layer 7 covering the substrate 1 and the gate 2, covering the contact hole etch barrier layer 7 from top to bottom are sequentially provided with a first hard mask Film layer 3, metal insulating dielectric layer 4, metal etching barrier layer 5, contact hole insulating oxide layer film 6, contact hole etching barrier layer 7 partially covers source / drain doped region 10 and gate 2 on substrate 1 The upper surface of the upper surface and the upper surface and the outer surface of the gate spacer 11; wher...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Thickness | aaaaa | aaaaa |

| Thickness | aaaaa | aaaaa |

| Thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to view more

Login to view more - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap