Memory access controller supporting data descrambling and memory access controller descrambling method

A controller and data technology, applied in the direction of electrical digital data processing, instruments, etc., can solve the problems of inconvenient large-scale data processing, small parallelism, simplicity, etc., and achieve the effect of improving data processing capabilities

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

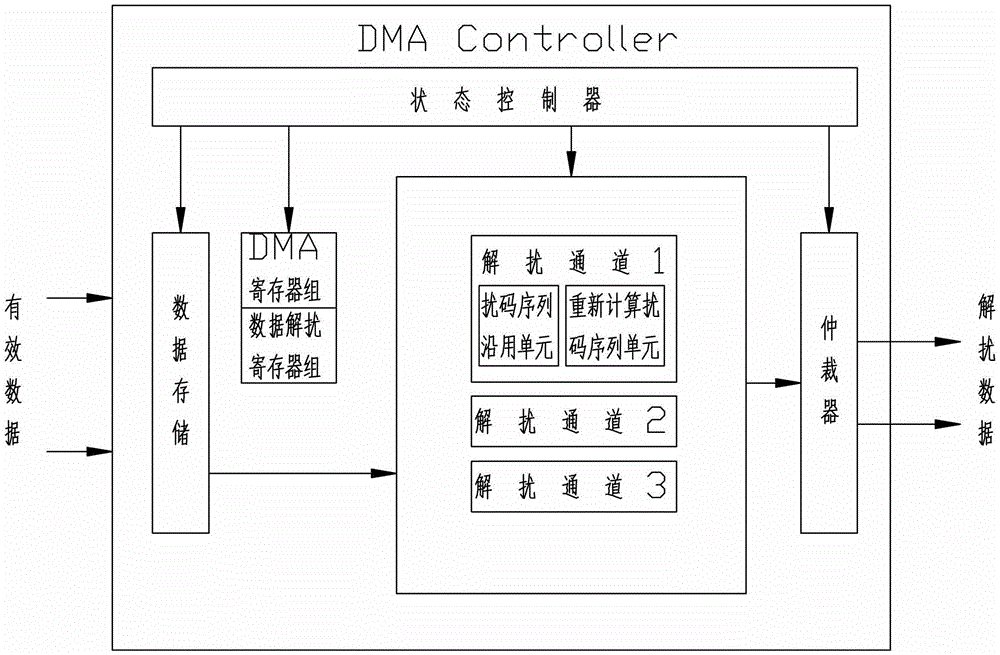

[0044] like figure 1 As shown, the memory access controller is provided with three descrambling channels and an arbiter, and the arbiter is located after the three descrambling channels. Wherein; the three descrambling channels perform corresponding descrambling on different types of source data according to the control instructions of the memory access controller; the arbiter judges the data obtained after descrambling to output the corresponding data .

[0045] The execution process is as follows: when the state controller in the memory access controller issues a data transmission start command, it will automatically obtain the valid data to be descrambled from the memory, and transfer it to the three descrambling channels, and then in the descrambling channel according to the DMA The DMA information stored in the register group and the control information stored in the data descrambling register group are descrambled for the valid data to be descrambled. When the valid da...

Embodiment 2

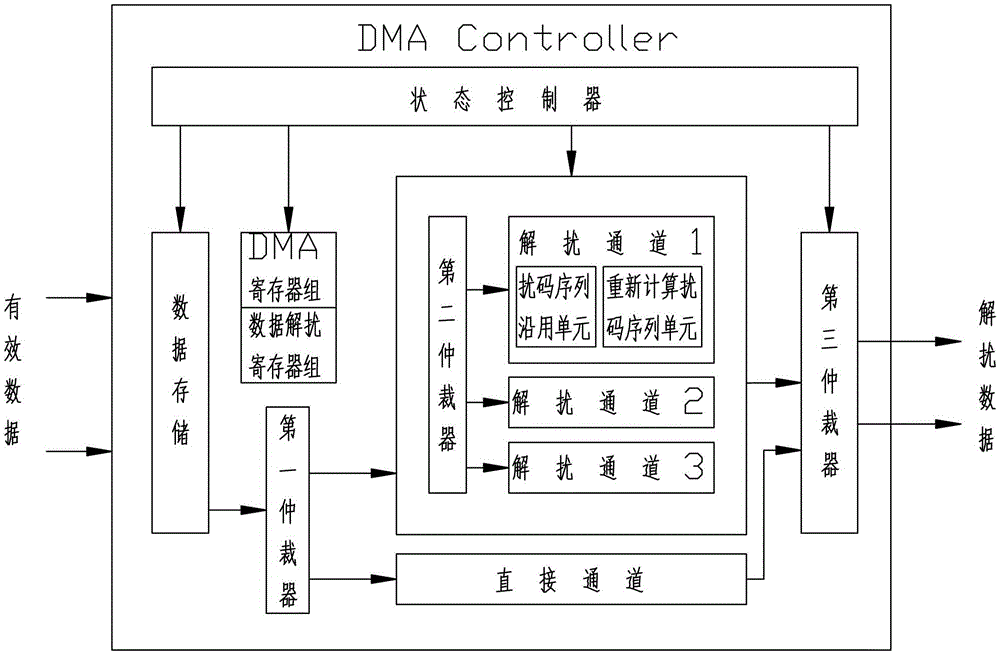

[0049] like figure 2As shown, the memory access controller is provided with three descrambling channels, one direct channel and three arbiters, wherein the three descrambling channels respond to different types of source data according to the control instructions of the memory access controller descrambling; direct channel, carrying non-descrambling data; three arbiters including a first arbiter, a second arbiter and a third arbiter, wherein;

[0050] The first arbiter judges the source data according to the control instruction of the memory access controller, so as to distinguish the descrambled data and the non-descrambled data;

[0051] The second arbiter judges the data to be descrambled according to the control instruction of the memory access controller, so as to distinguish different types of data and assign each descrambling channel for descrambling;

[0052] The third arbiter judges the data obtained after descrambling and the non-descrambling data according to the ...

Embodiment 3

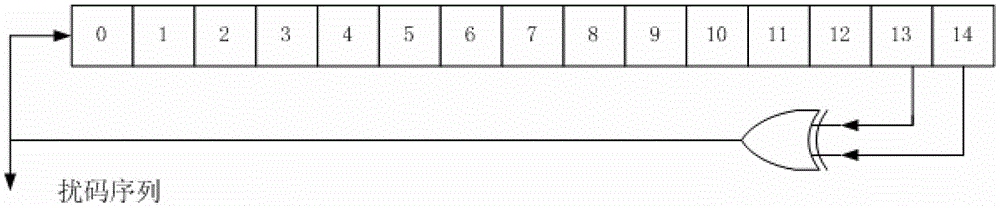

[0062] Example 3: Generating polynomial x for scrambling code 15 +x 14 +1, the specific production process is: in the process of DMA moving and data descrambling at the same time, the scrambling code sequence can be as follows: image 3 The cyclic shift register shown is generated.

[0063] 1. Initialize the control word, including the initial value (X) of the 16-bit register as shown in the figure, the calculation length of the scrambling code preparation sequence, etc.

[0064] 2. Start DMA to obtain data from the data source,

[0065] 3. Use the generated scrambling code sequence to descramble the data,

[0066] 4. The processed data is stored in the storage unit.

[0067] The scrambling code is generated as follows:

[0068] X[1] <= X[0];

[0069] X[2] <= X[1];

[0070] X[14] <= X[13];

[0071] X[0]<=X[14]^X[13].

[0072] Each clock cycle generates a scrambling code, that is, the value of X[13]^X[14].

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More