Method for simulating low speed parallel interface by using GPIO (general purpose input output)

An interface and low-speed technology, which is applied in the field of using GPIO to simulate low-speed parallel interfaces, can solve problems such as the inability to find conversion chips

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

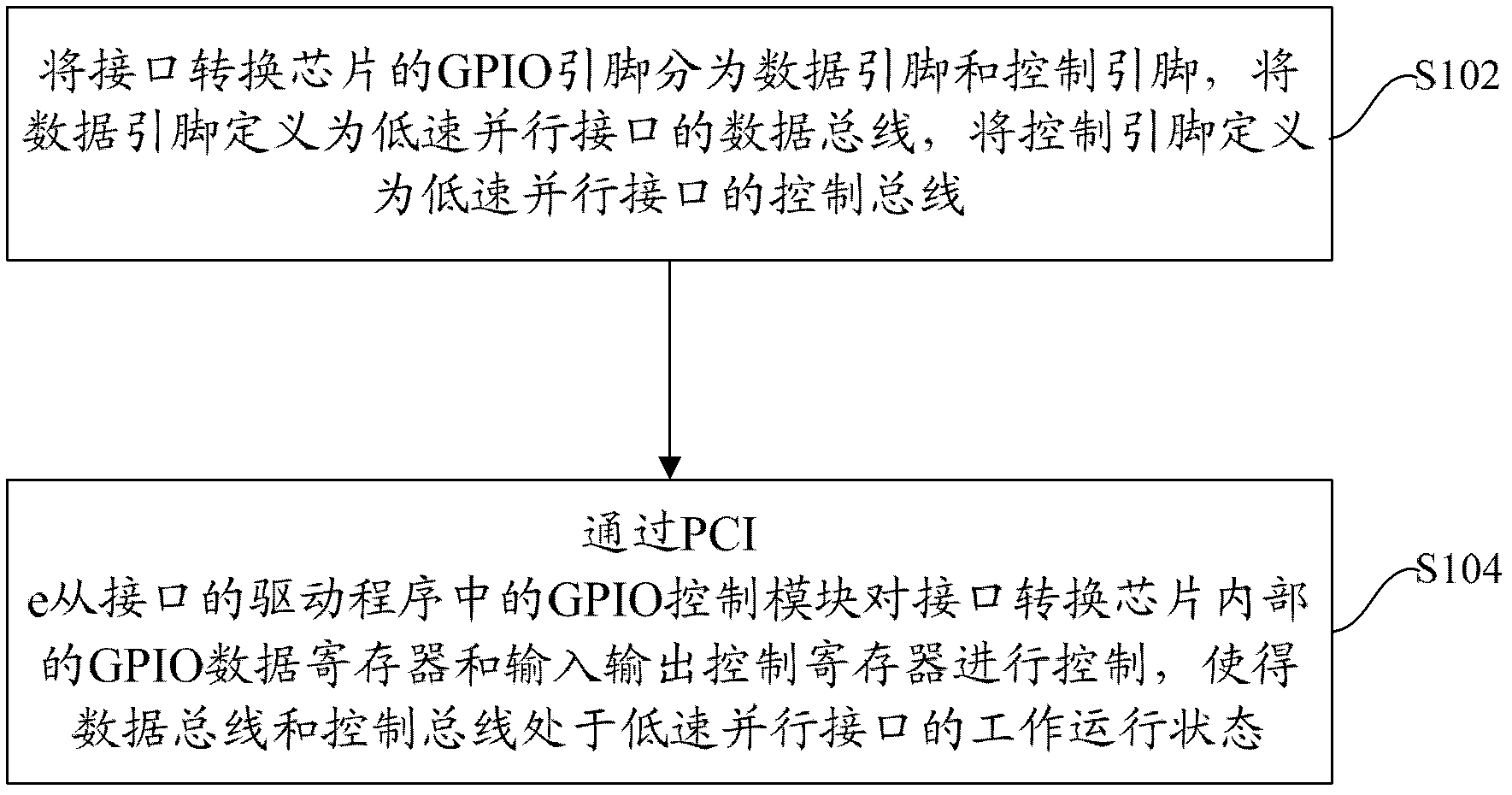

Image

Examples

Embodiment Construction

[0042] The following will clearly and completely describe the technical solutions in the embodiments of the present invention with reference to the accompanying drawings in the embodiments of the present invention. Obviously, the described embodiments are only some, not all, embodiments of the present invention. Based on the embodiments of the present invention, all other embodiments obtained by persons of ordinary skill in the art without making creative efforts belong to the protection scope of the present invention.

[0043] In the embodiment of the present invention, select PCIe bridge chip XR17V352IB113-F to design, this chip has PCIe slave interface, has 16 GPIOs, is GPIO[0] to GPIO[15] respectively, connects GPIO[0] to GPIO[15]. GPIO[3] is defined as a control signal pin, respectively: GPIO[0] is defined as its own buffer state output pin, GPIO[1] is defined as the other party’s read signal input pin, and GPIO[2] is defined as the other party’s buffer state input pin Pi...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More