Patents

Literature

770 results about "General-purpose input/output" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

A general-purpose input/output (GPIO) is an uncommitted digital signal pin on an integrated circuit or electronic circuit board whose behavior—including whether it acts as input or output—is controllable by the user at run time.

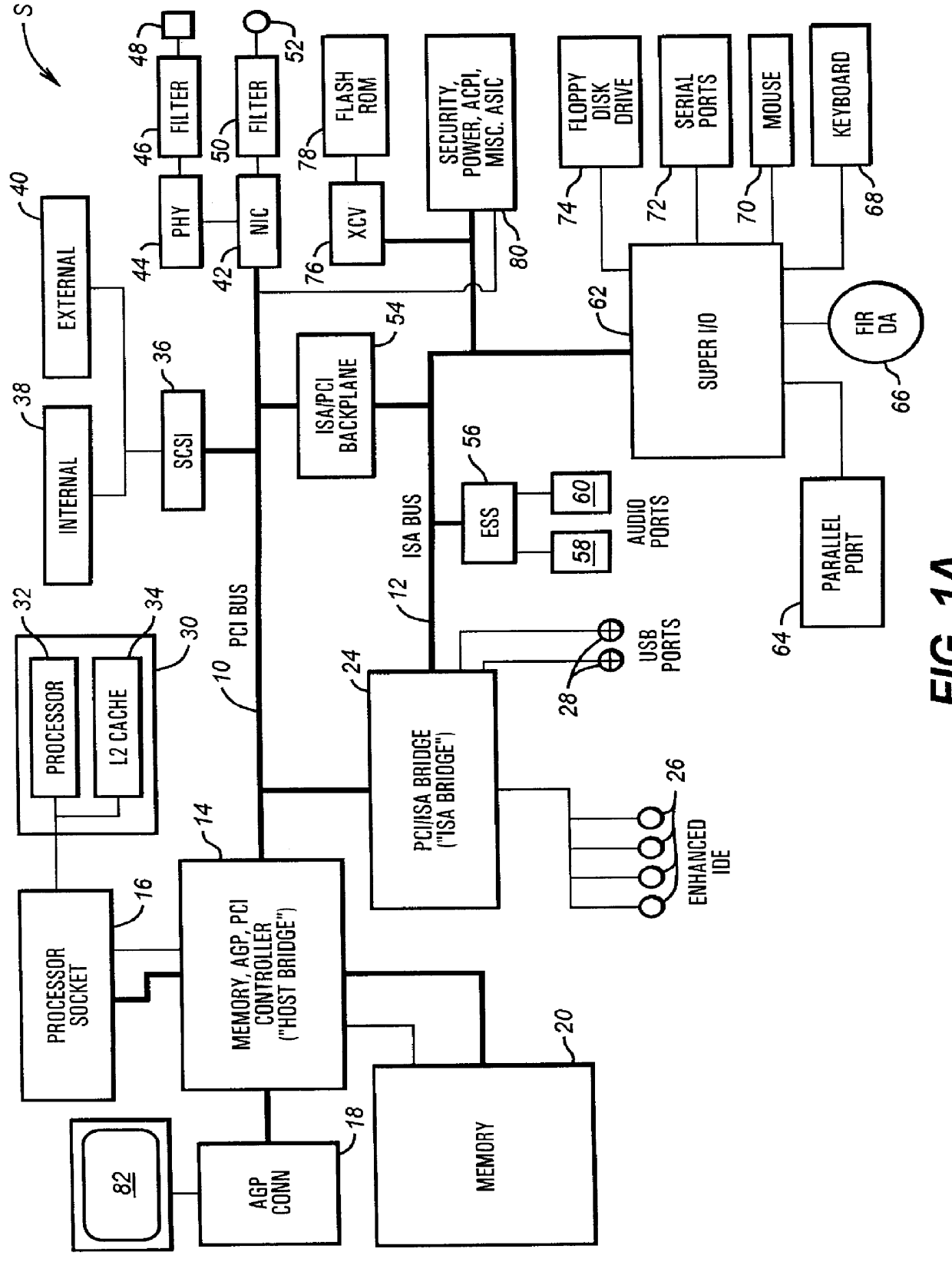

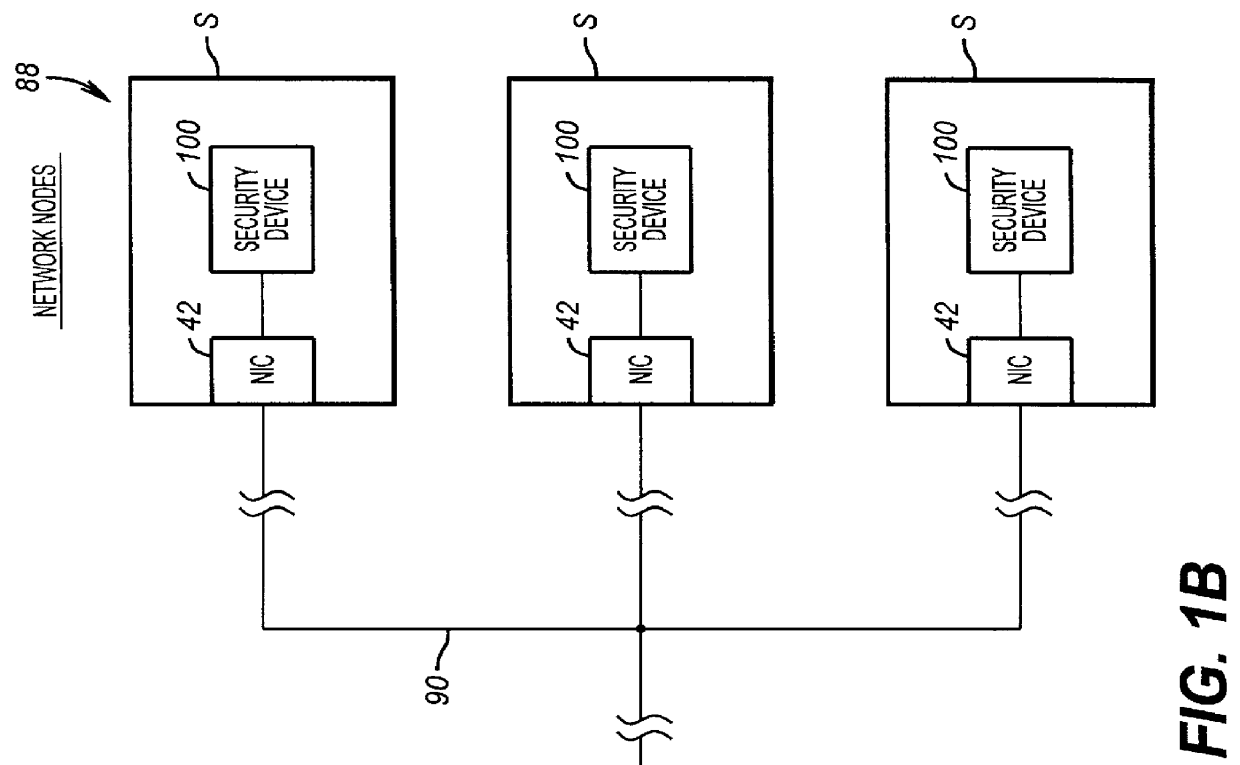

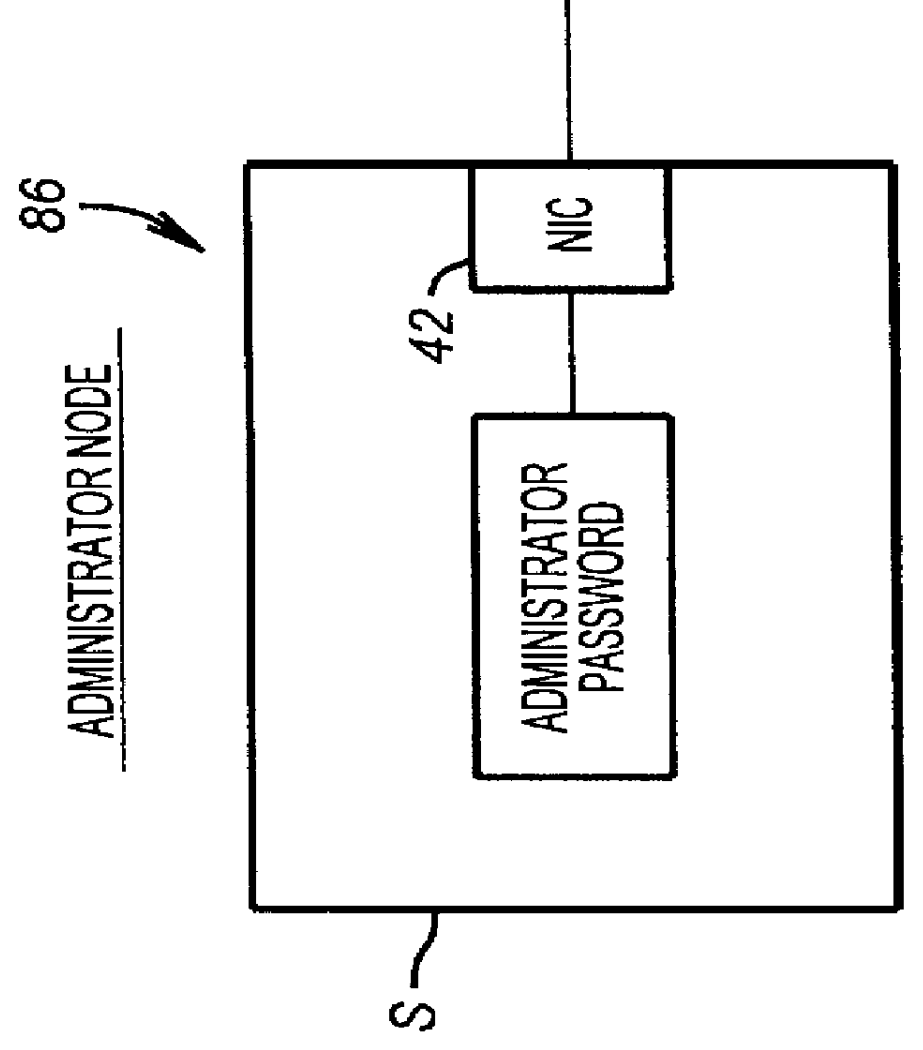

Secure general purpose input/output pins for protecting computer system resources

InactiveUS6138240AImprove securityError detection/correctionDigital data processing detailsGeneral purposePassword

A security device and methodology that prevents unauthorized access to general purpose I / O pins in a computer system. In a system according to the invention, secure general purpose I / O pins are utilized as enable signals for data transfer devices such as Universal Serial Port (USB) ports. In one embodiment of the invention, access to the secure general purpose I / O pins is governed by an administrator password that is protected by a memory slot in a security device. When an administrator (or other authorized user) desires access to the general purpose I / O register that controls the secure general purpose I / O pins, the administrator enters the administrator password. If the password is correct, the relevant slot of the security device is unlocked, thereby permitting completion of write cycles to the secure general purpose I / O register. If a write cycle to the secure general purpose I / O register is attempted while the relevant slot in the security device is locked, the write cycle is ignored. Control and monitoring of various system resources in a secure manner is thereby permitted via use of the secure general purpose I / O pins.

Owner:HEWLETT PACKARD DEV CO LP

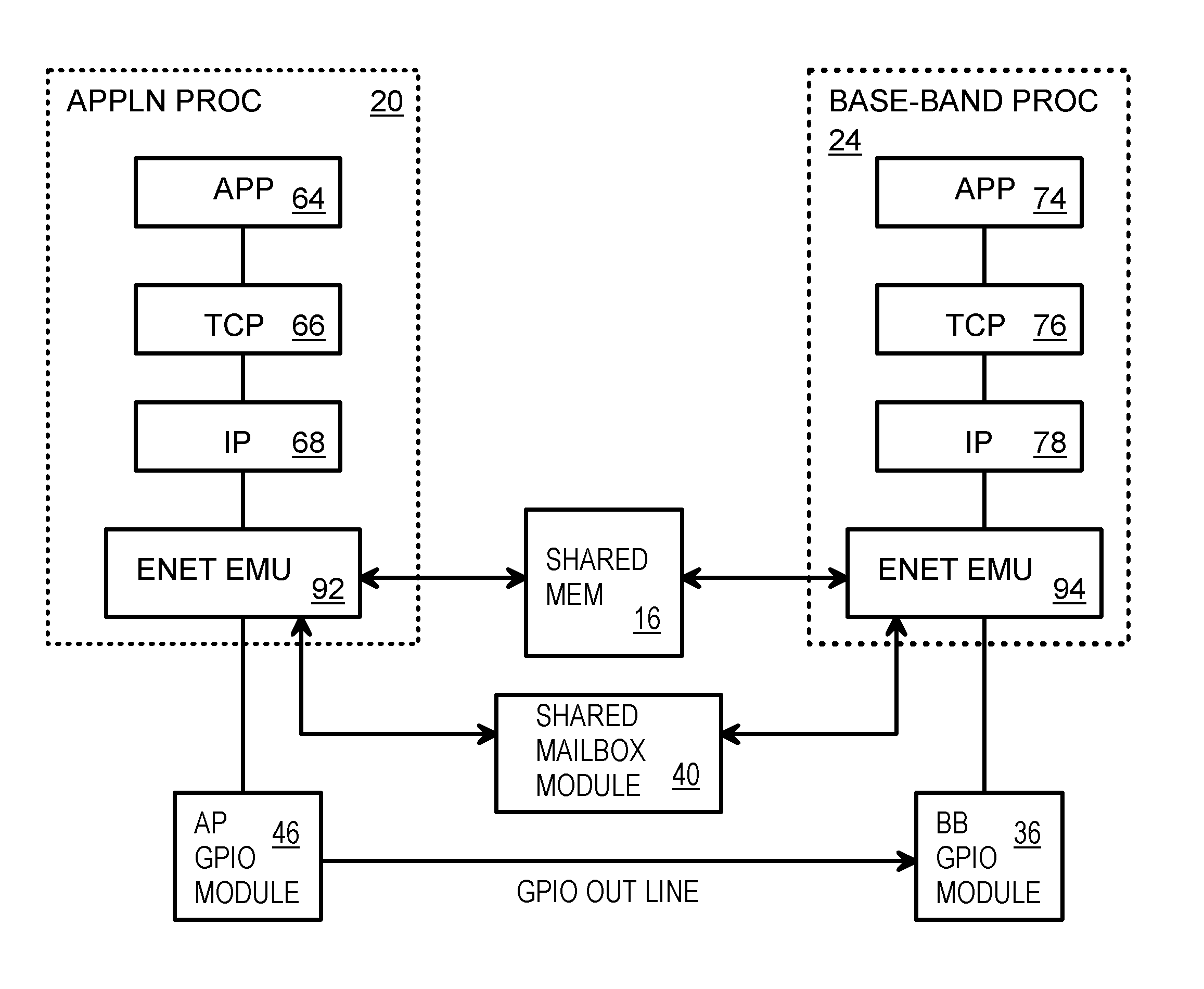

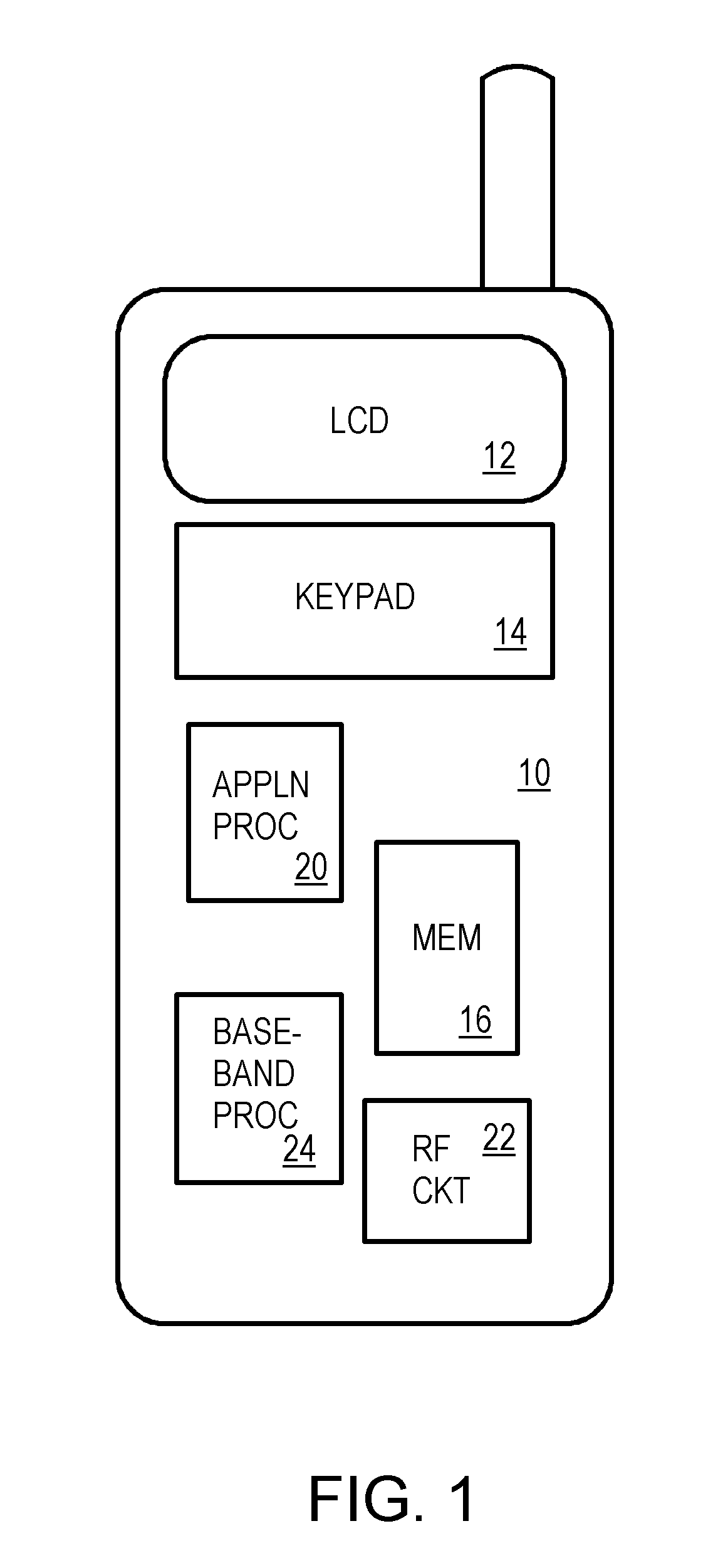

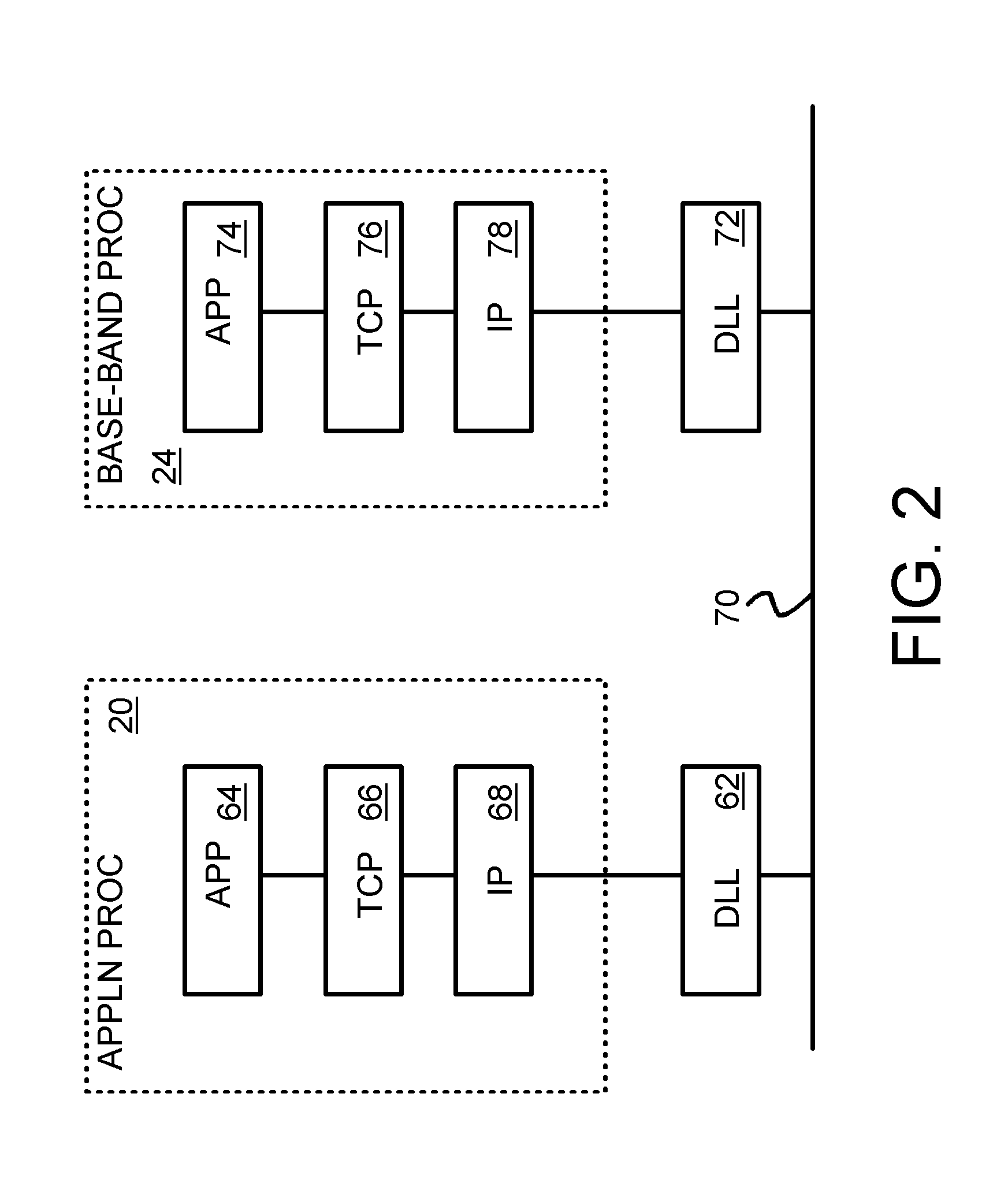

Ethernet emulation using a shared mailbox between two processors in a feature phone

A feature phone has a base-band processor and an applications processor that communicate with each other by emulating an internal Ethernet within the phone. TCP / IP stacks in each processor receive data from high-level applications for transmission to the other processor. Ethernet-emulating drivers are called by the IP layers. An Ethernet-emulating transmit driver writes IP-packet data to a shared memory and sends an interrupt to the other processor, which activates a receive routine that reads the IP packet data from the shared memory and sends it up through the TCP / IP stack. There is no twisted-pair cable or other media since the shared memory acts as the transfer media. A shared mailbox holds the packet length and sends an interrupt to one processor when written, while a general-purpose input-output GPIO module sends an interrupt to the other processor. The internal emulated-Ethernet is entirely within the phone and separate from cellular networks.

Owner:INTELLECTUAL VENTURES I LLC

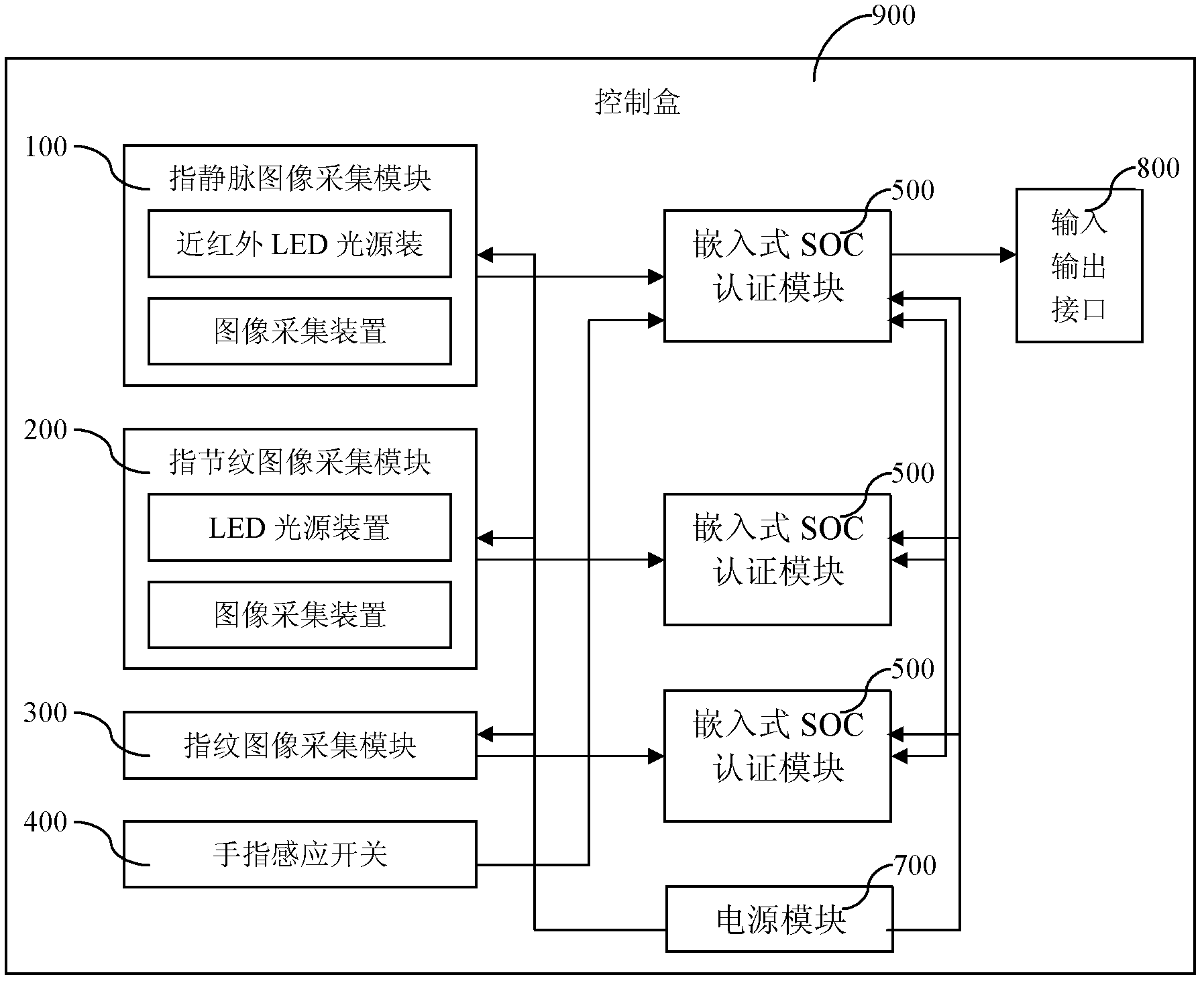

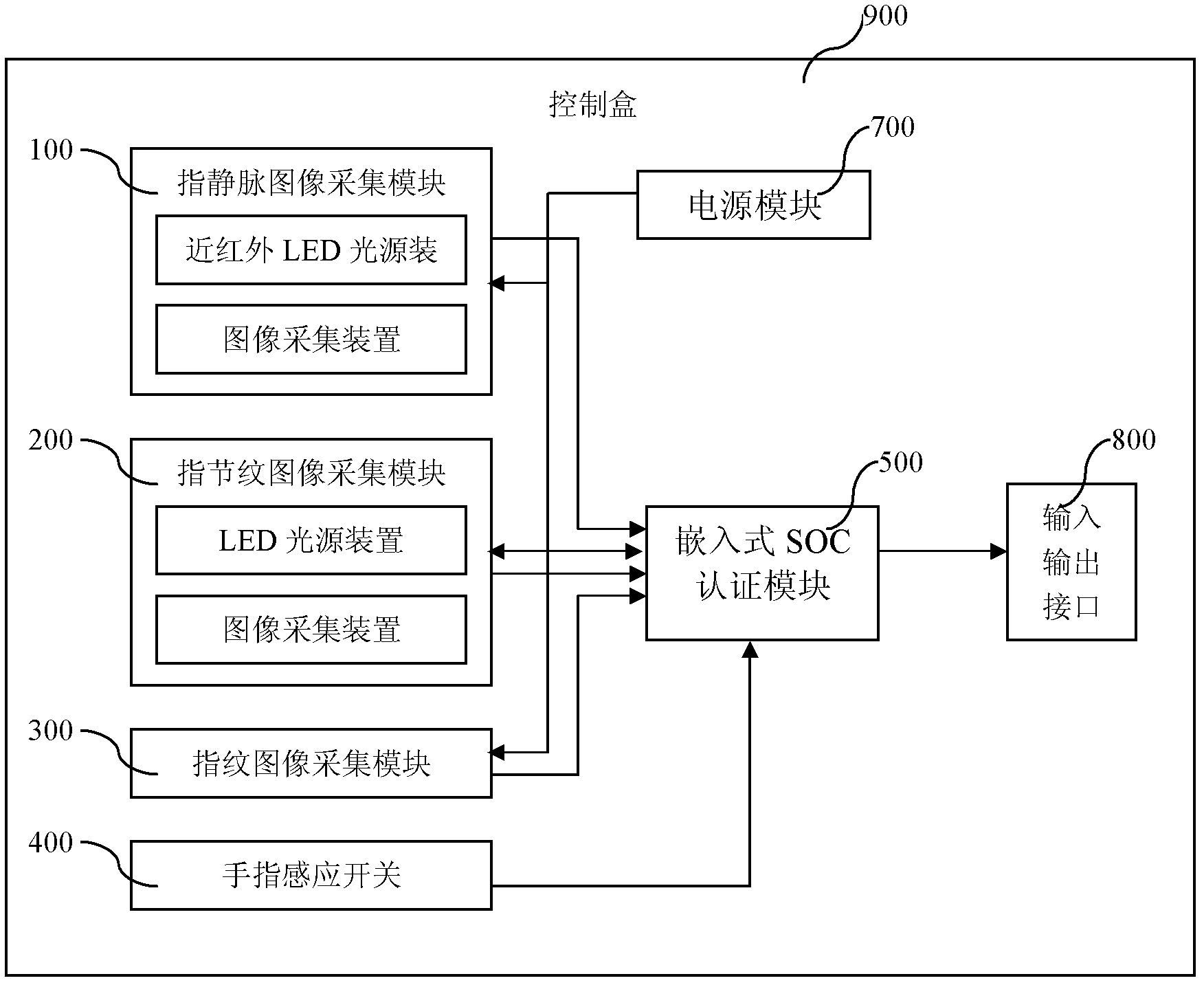

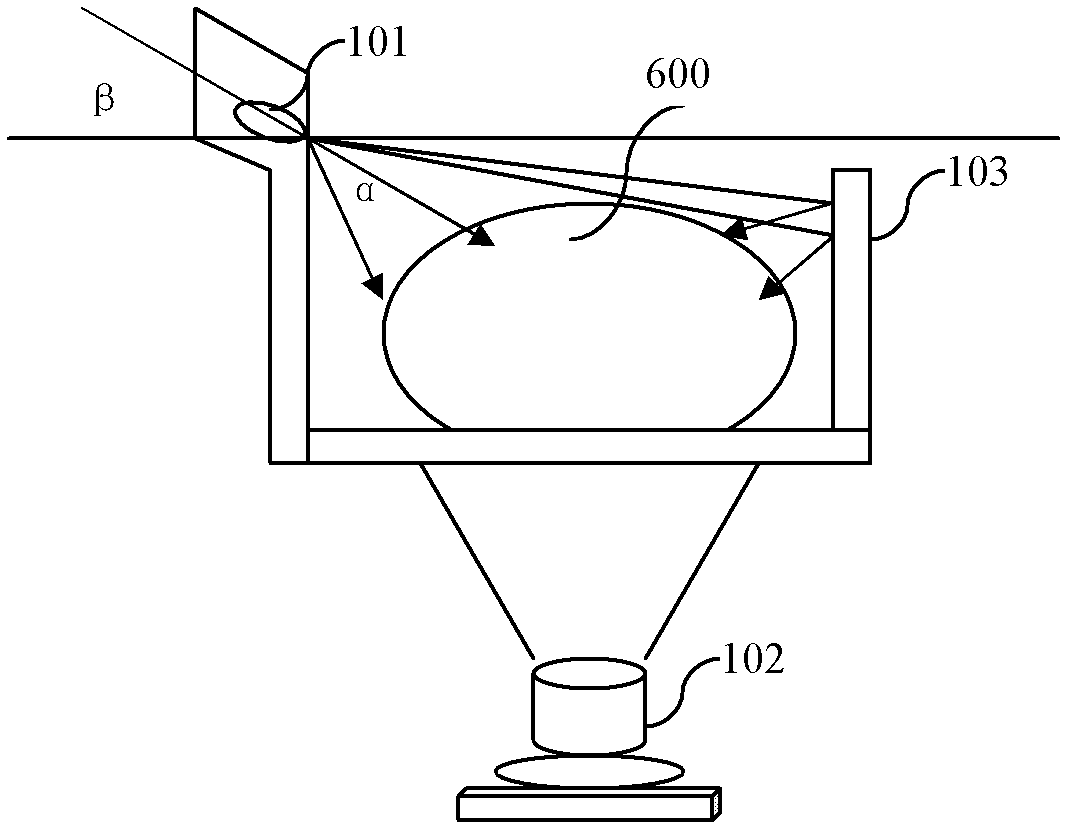

Multi-mode identity authentication method and device based on biological characteristics of fingers

InactiveCN102542263AEfficient integrationImprove collection qualityCharacter and pattern recognitionVeinComputer module

The invention relates to a multi-mode identity authentication device based on the biological characteristics of fingers, which comprises a finger vein image collection module, a finger knuckle stripe image collection module, a fingerprint image collection module, a finger induction switch, an embedded type start of conversion pulse (SOC) authentication module, a control box, an input / output interface and a power supply module; the modules, the finger induction switch and the input / output interface are all installed on the control box, the finger vein image collection module, the finger knuckle stripe image collection module and the fingerprint image collection module are connected with an image input interface of the embedded type SOC authentication module so as to realize the collection of the biological characteristics of veins, finger knuckle stripes and fingerprints, and the finger induction switch is connected with a GPIO (General Purpose Input / Output) interface of the embedded type SOC authentication module so as to realize the detection of the placement of the fingers; and the power supply module is connected with each module so as to provide a power supply required for working. The invention relates to a multi-mode identity authentication method based on the biological characteristics of the fingers, which comprises characteristic registration and characteristic comparison comprising nine steps respectively. According to the multi-mode identity authentication device and the method based on the biological characteristics of the fingers, the safety of identity identification is effectively enhanced. The multi-mode identity authentication device and the method based on the biological characteristics of the fingers have extensive application prospect.

Owner:北京鑫光智信软件技术有限公司

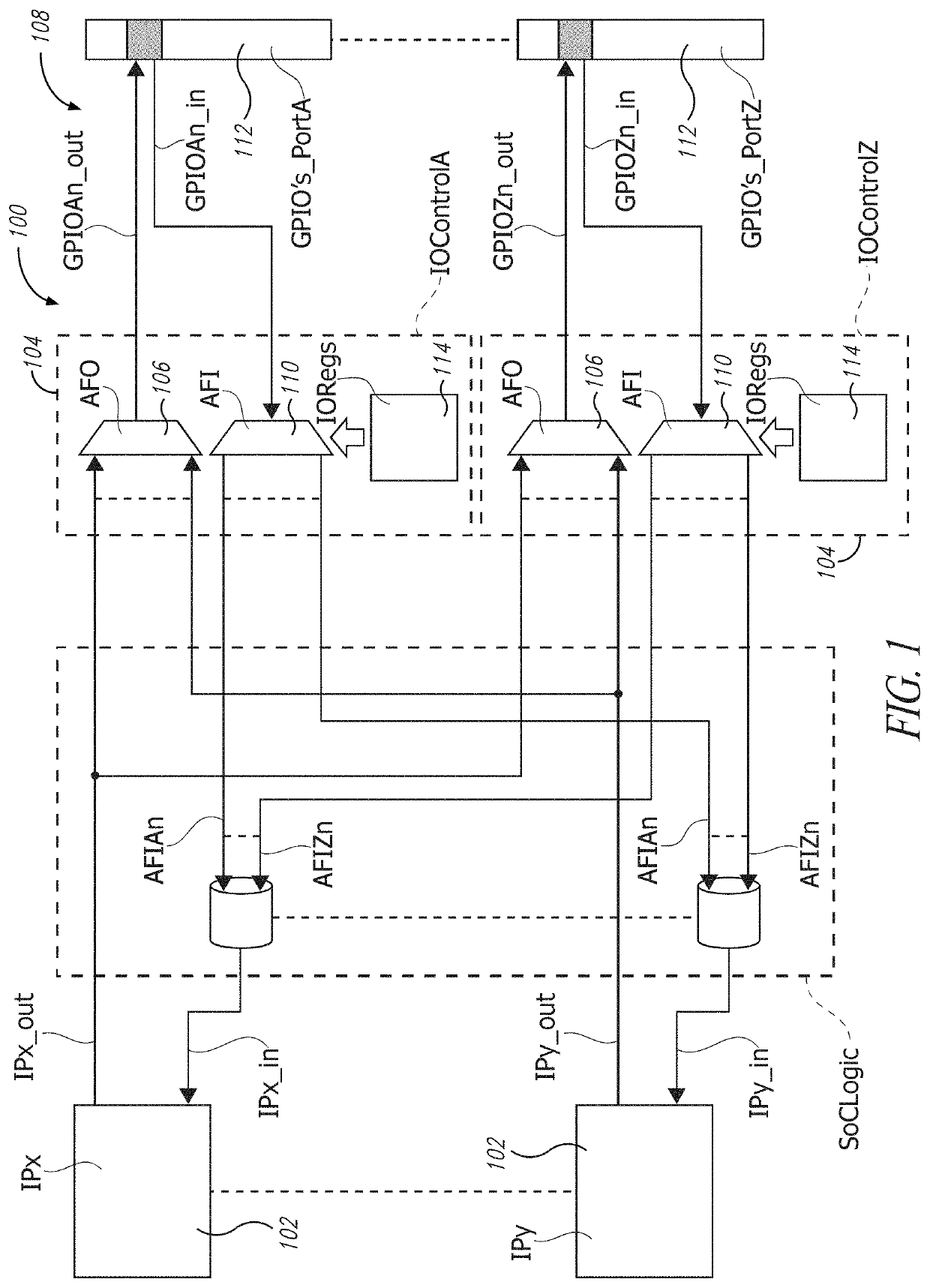

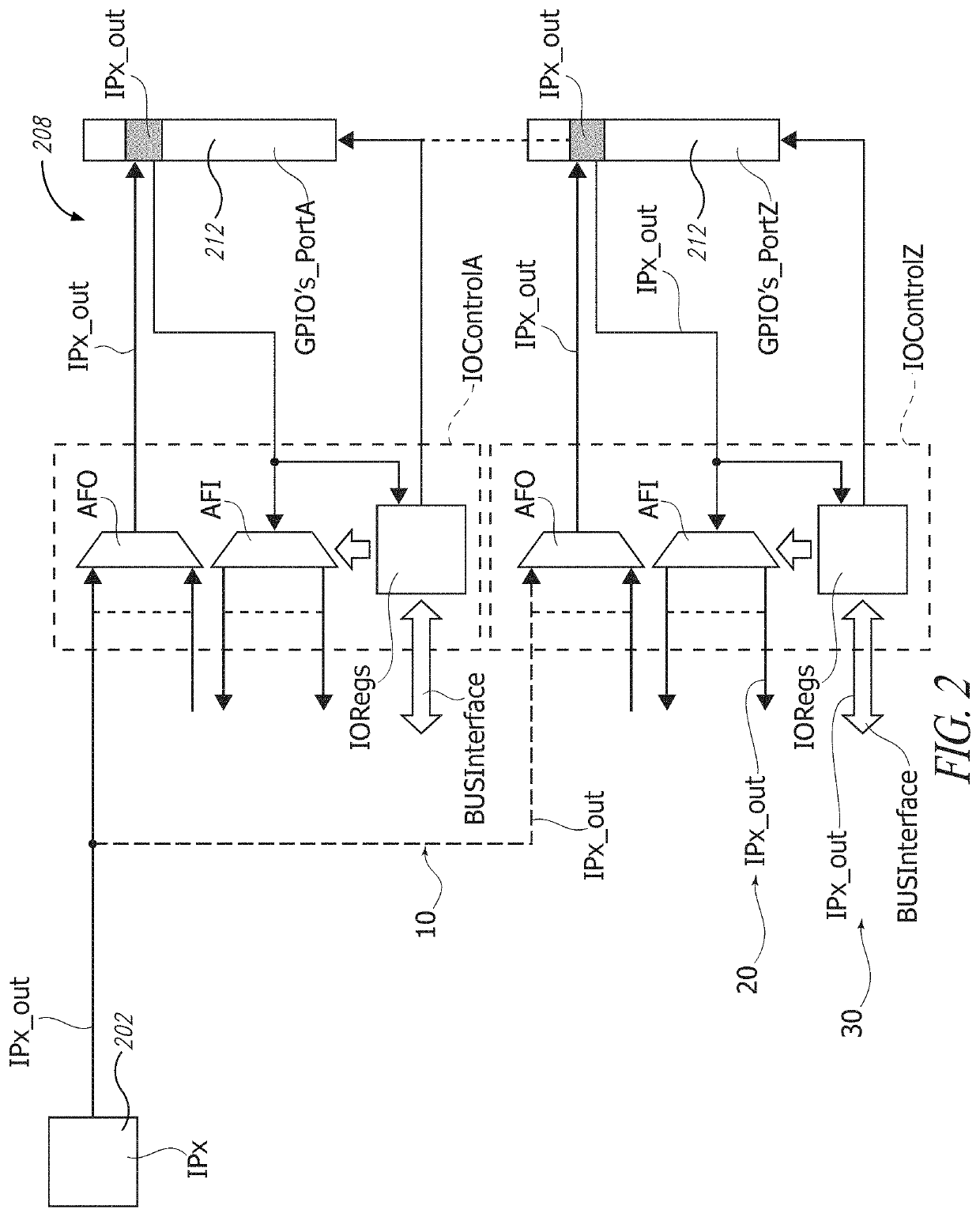

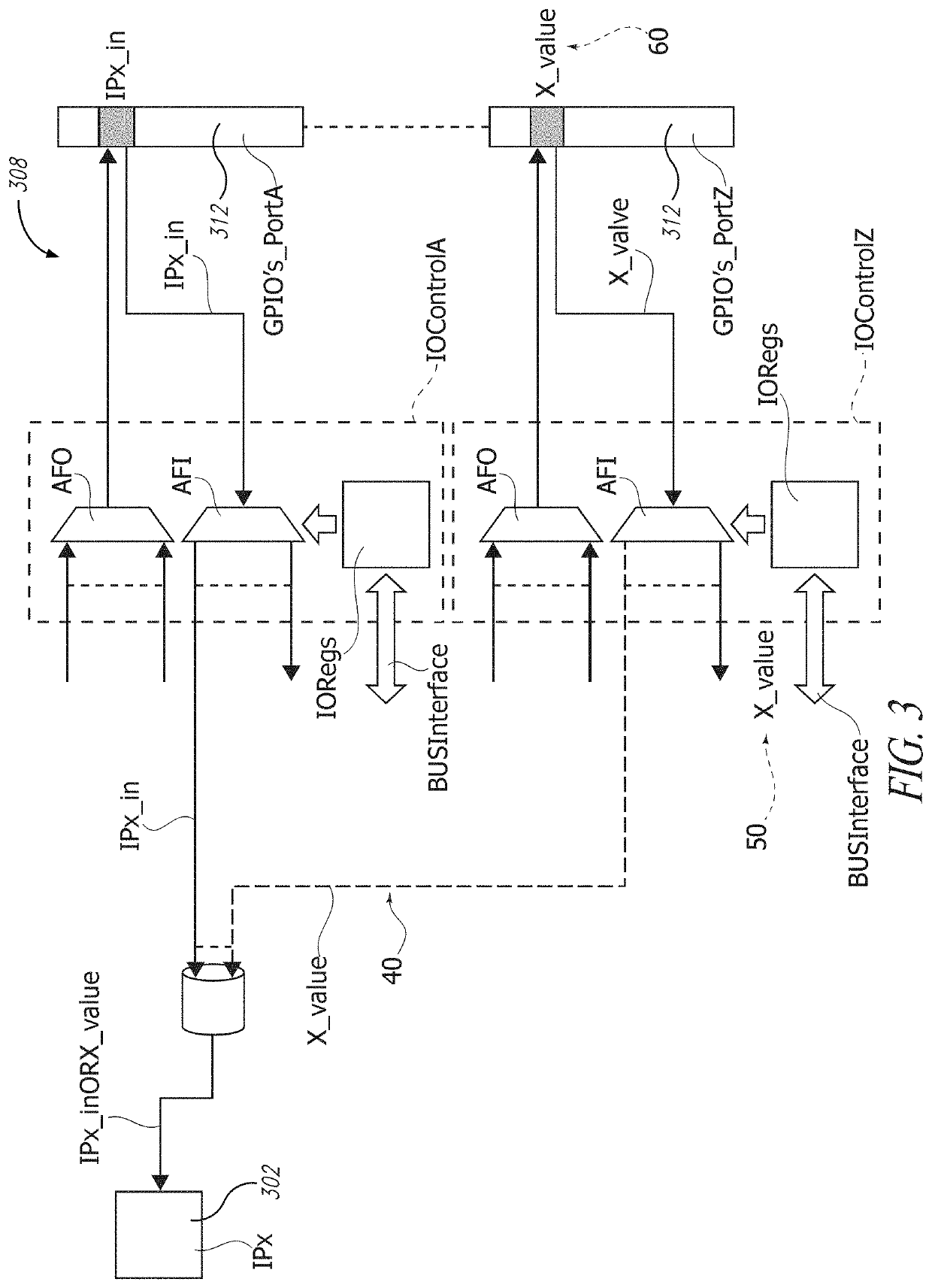

System with secure SoC connections among IP and multiple GPIOs, and corresponding method

ActiveUS11144678B2Improve robustnessDigital computer detailsDigital data protectionComputer networkIntegrated circuit

An integrated circuit includes one or more intellectual property (IP) cores, one or more general purposes input / output (GPIO) interfaces, each GPIO interface having one or more ports, and one or more security circuits, each security circuit being coupled between an IP core and a GPIO interface. A security circuit, in operation, selectively enables communications between the IP core and the GPIO interface coupled to the security circuit based on an indication of the security status of the IP core, an indication of the security status of the GPIO interface or both the indication of the security status of the IP core and the indication of the security status of the GPIO interface.

Owner:STMICROELECTRONICS SRL

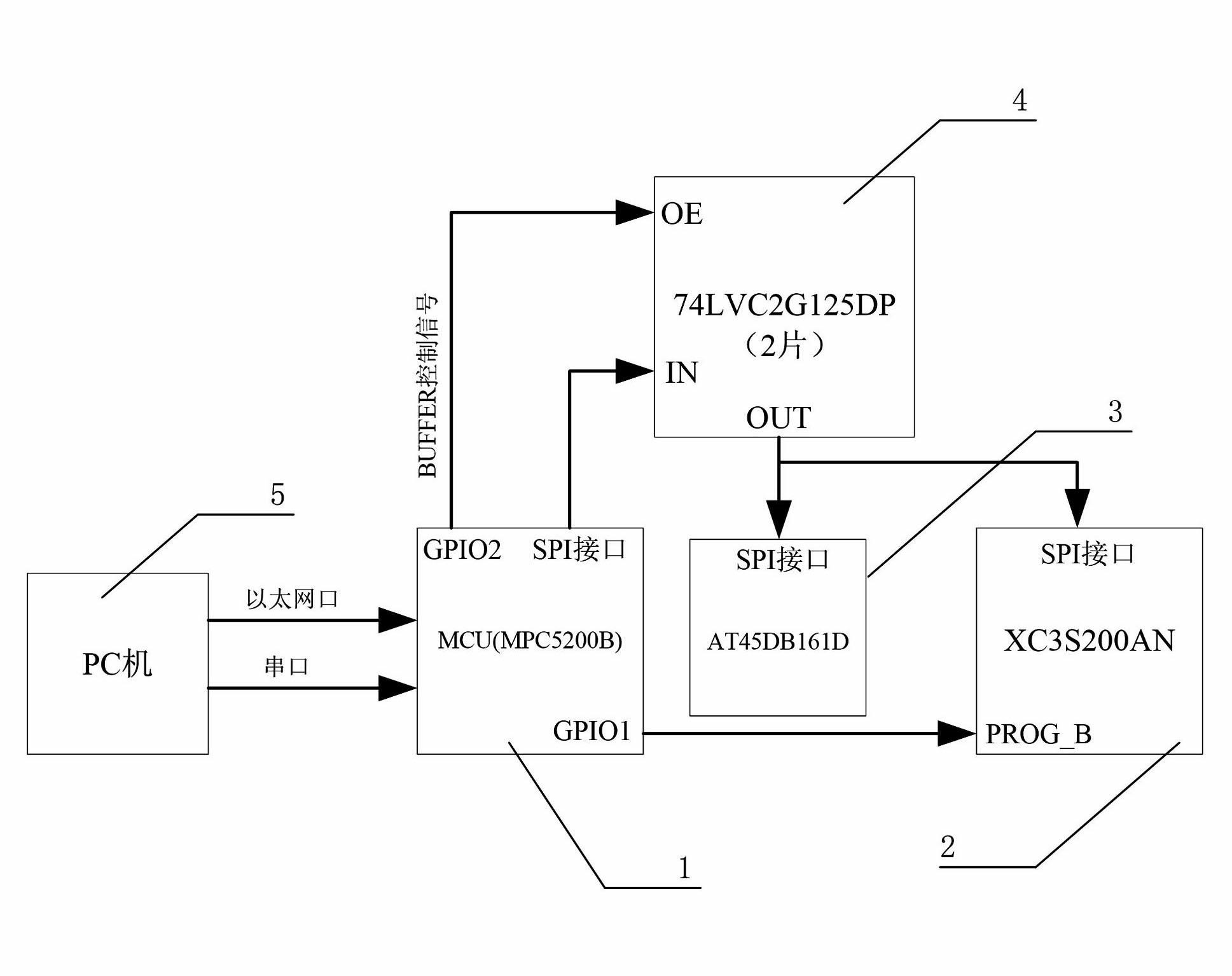

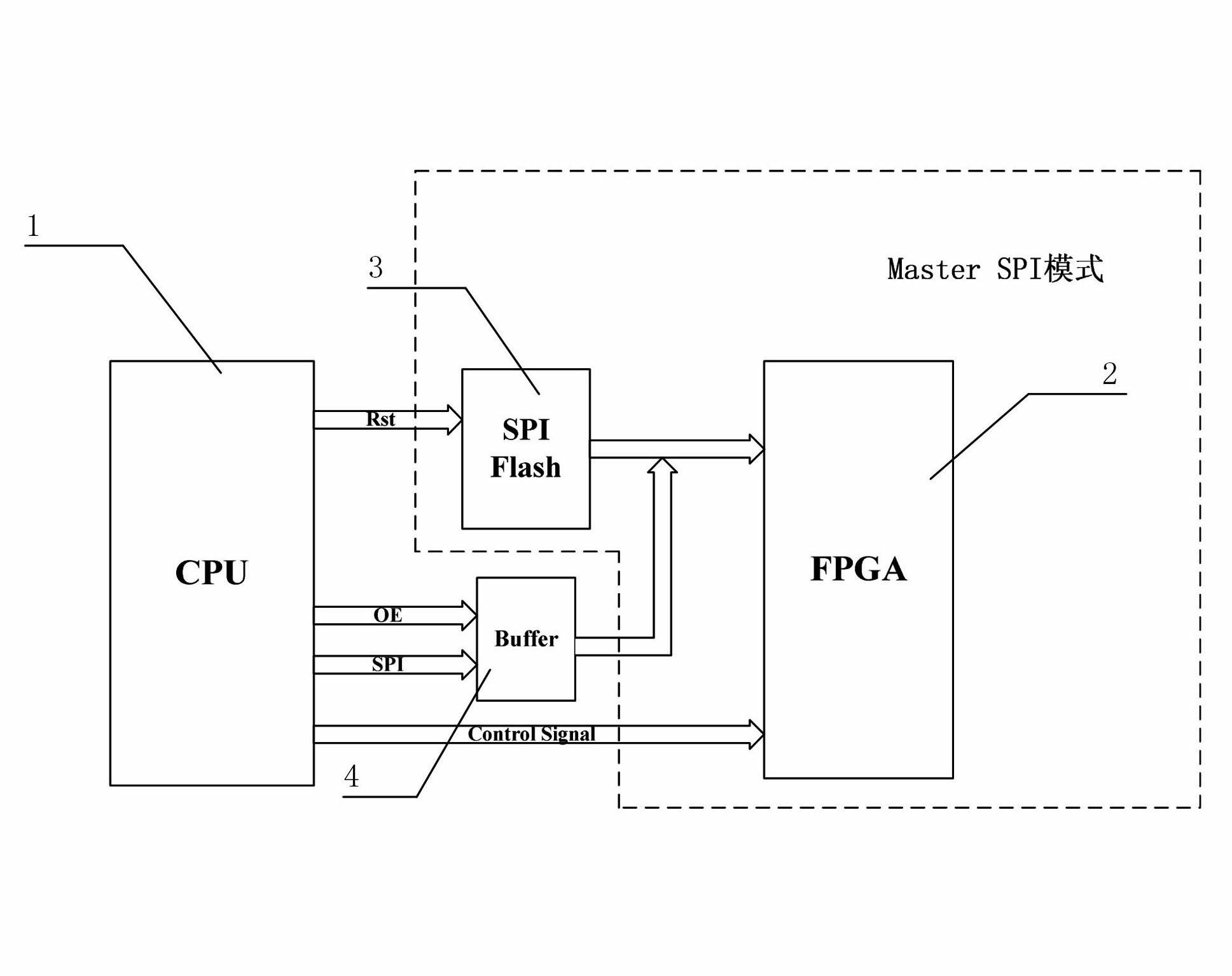

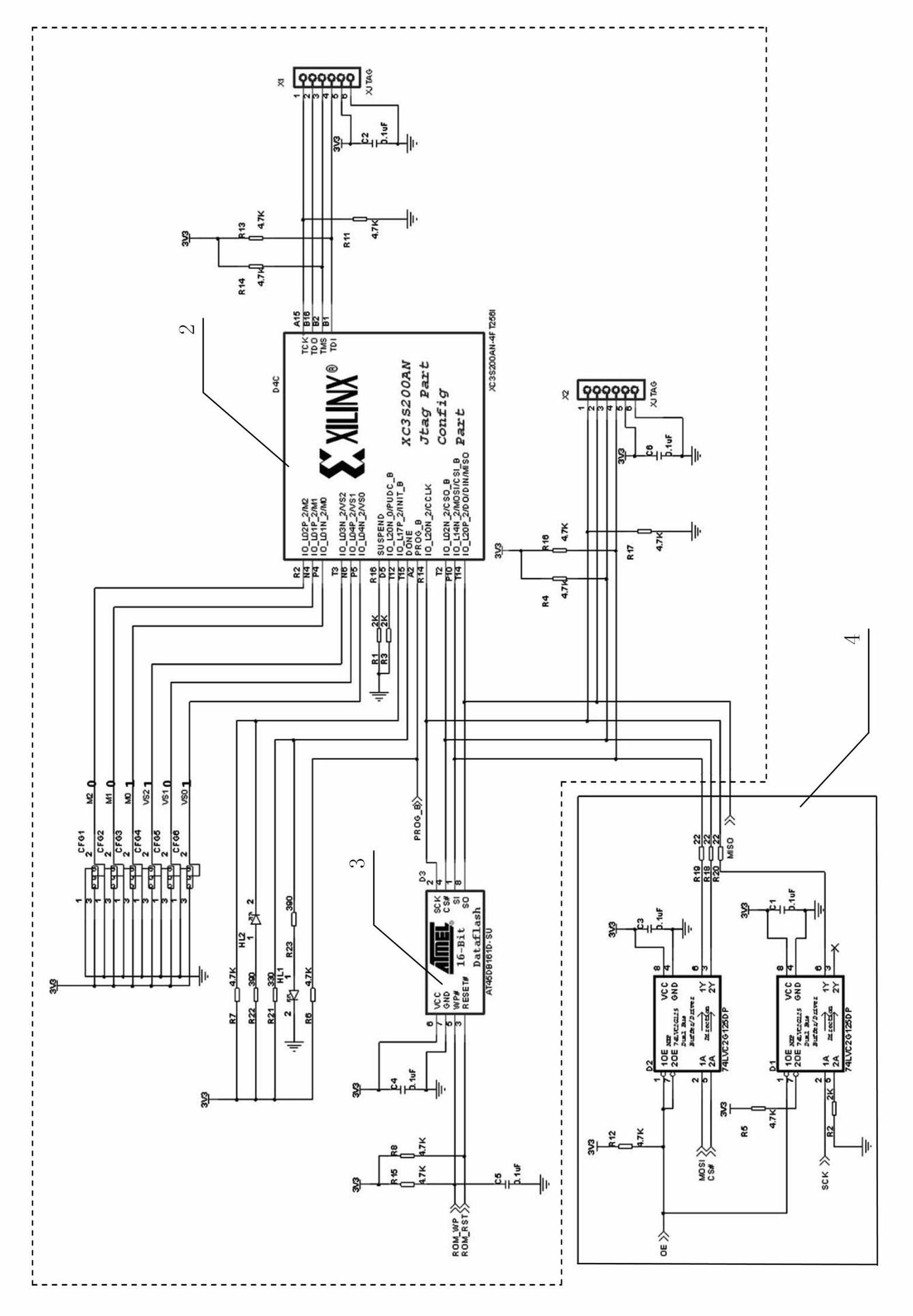

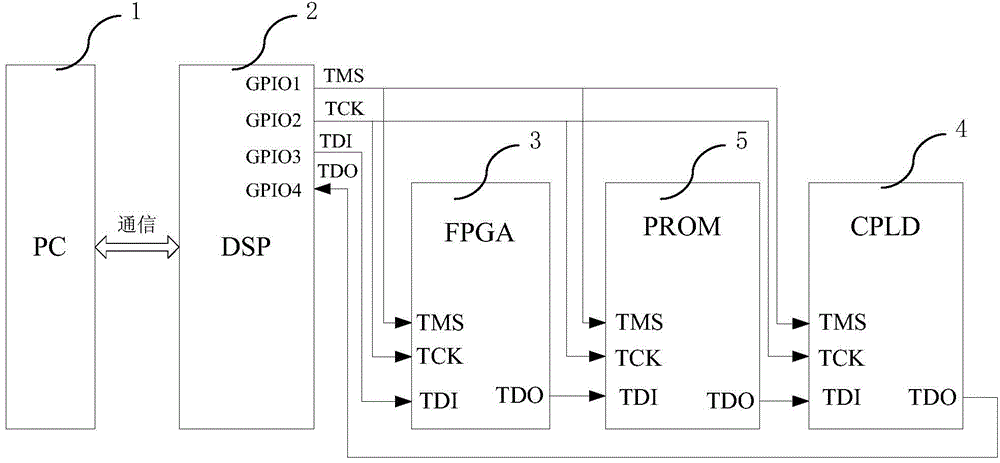

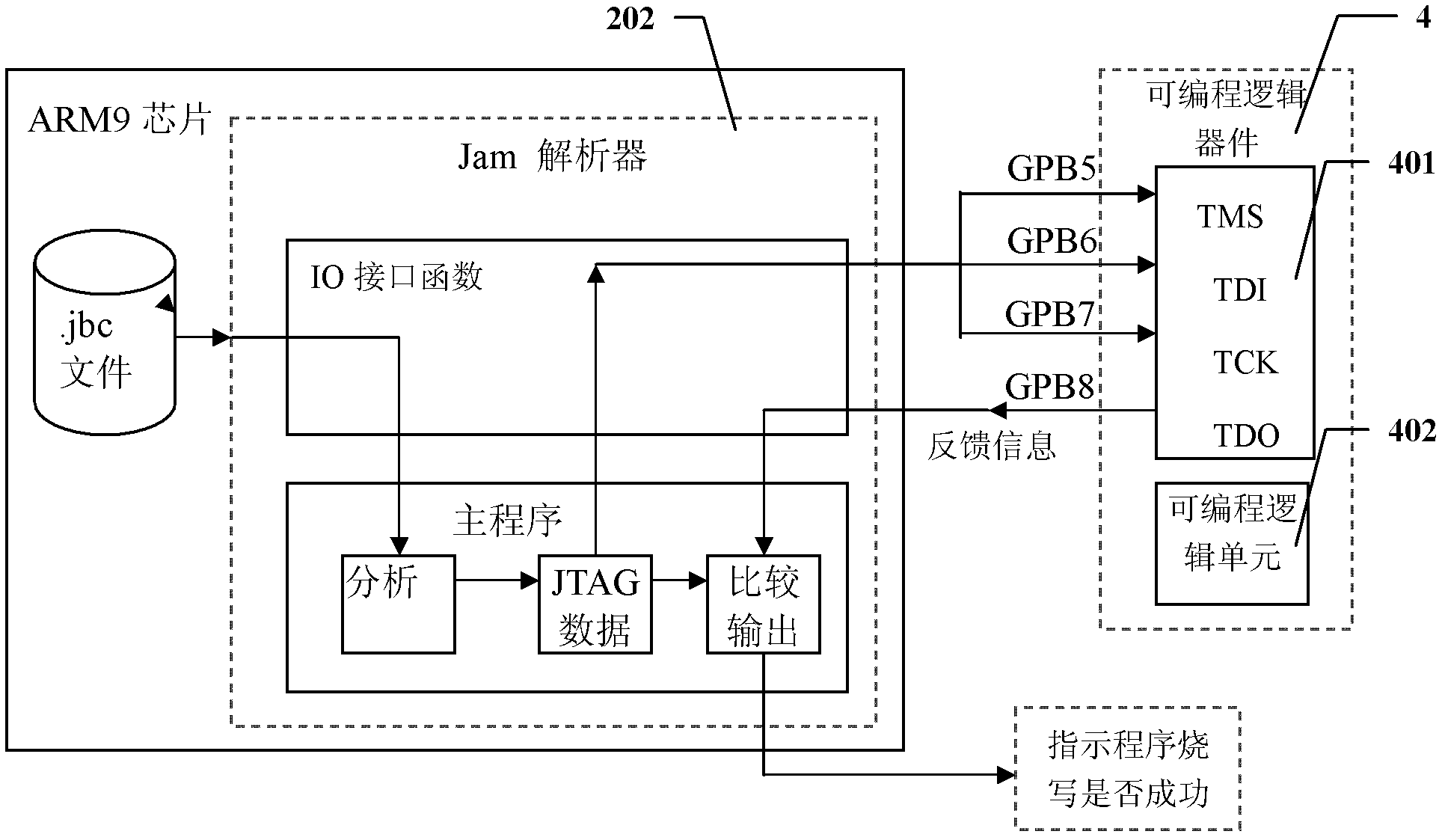

Device for updating FPGA (Field Programmable Gate Array) from a long distance by CPU (Central Processing Unit) and method therefor

ActiveCN102609287ALow costEasy to operateProgram loading/initiatingOperabilityReal-time operating system

The invention discloses a device for updating an FPGA (Field Programmable Gate Array) from a long distance by a CPU (Central Processing Unit) and a method for updating the FPGA from a long distance by the CPU. The device comprises a controller module, an FPGA module, a configuration module and a buffer module, wherein the controller module is connected with an upper computer in a wired / wireless way, a second GPIO (General Purpose Input / Output) interface of the controller module is connected with an enable pin of the buffer controller, an SPI (Serial Peripheral Interface) of the controller module is connected with a data input end of the buffer module, a first GPIO interface of the controller module is connected with a configuration signal of the FPGA module, a data output end of the buffer module is connected with SPIs of the FPGA module and the configuration module respectively, a FPGA configuration file is updated from a long distance based on MPC5200B and a real-time operation system VxWorks. According to the device and the method, the cost is saved, the operability of the system is improved, the design difficulty is reduced, the on-line updating of the FPGA is easily realized, and the configuration efficiency and the configuration flexibility of the FPGA are improved.

Owner:ZHUZHOU CSR TIMES ELECTRIC CO LTD

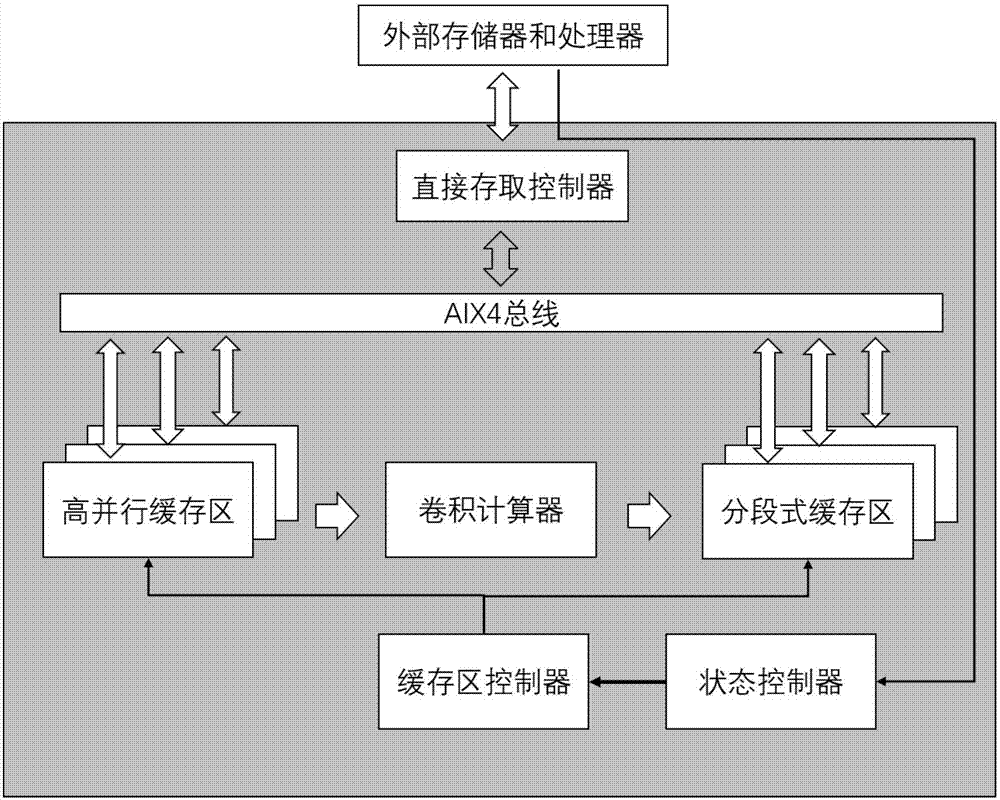

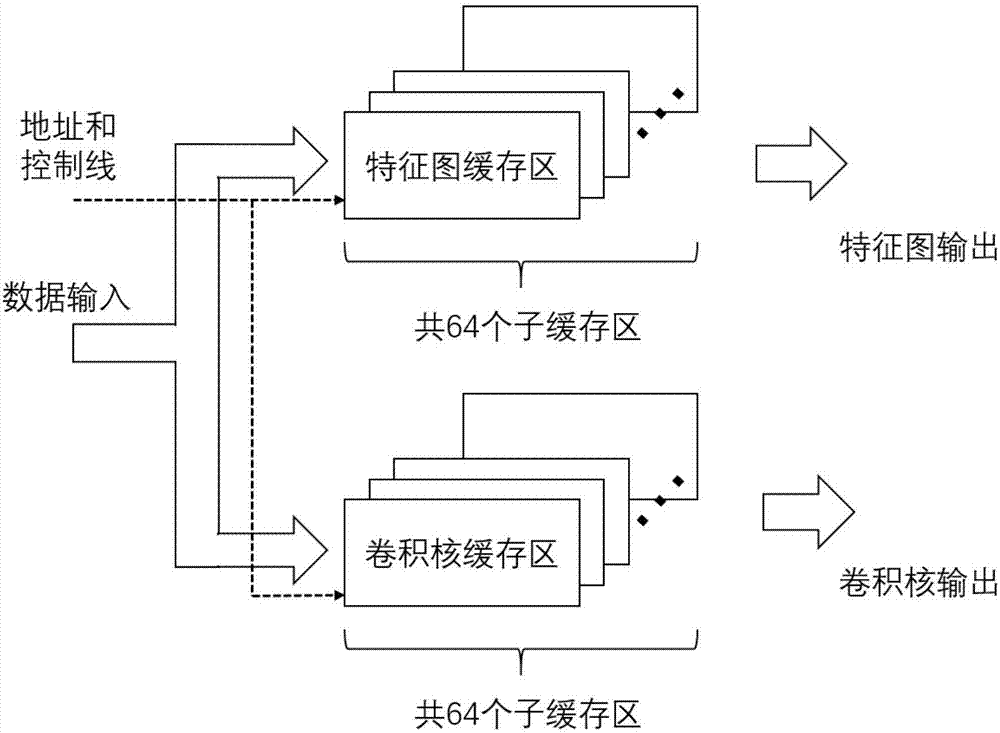

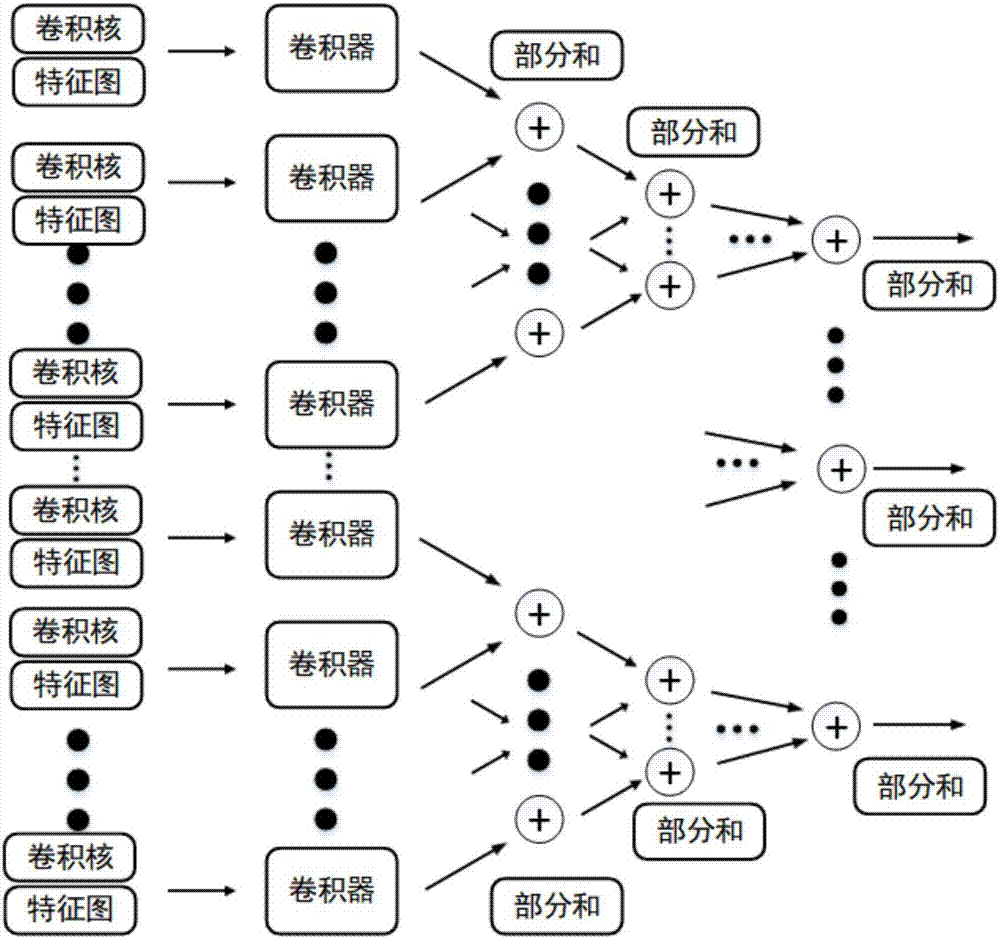

FPGA (field programmable gate array)-based universal fixed-point-number neural network convolution accelerator hardware structure

InactiveCN107392309AImprove versatilityIncrease computing speedPhysical realisationData conversionFace detectionHardware structure

The invention discloses an FPGA (field programmable gate array)-based universal fixed-point-number neural network convolution accelerator hardware structure which comprises a universal AXI4 high-speed bus interface, a universal GPIO (general purpose input / output) interface, a universal convolver, a universal read-write control unit, a universal state controller and a universal convolution result buffer. Universal memory hardware is provided, and high-parallel read-write operations are supported; the universal convolver can be used for accurate configuration of fixed point numbers, configuration of convolution operation levels and high-parallel convolution operation in coordination with high-parallel read-write operations after data storage; the universal read-write control unit includes ram, rom and Fifo read-write control logics and address generating logics; the universal state controller makes corresponding unit operating reactions aiming at a convolution layer and read-write and calculation processes to control an integral calculation process; the universal convolution result buffer is used for high-speed parallel caching and sending of a processing result to a bus according to a convolution result sectional accumulation method. By verification in application to Yolo algorithm based human face detection and CNN (convolutional neural network) based human face recognition, high operating speed and high data precision are embodied.

Owner:SOUTHEAST UNIV WUXI INST OF TECH INTEGRATED CIRCUITS +1

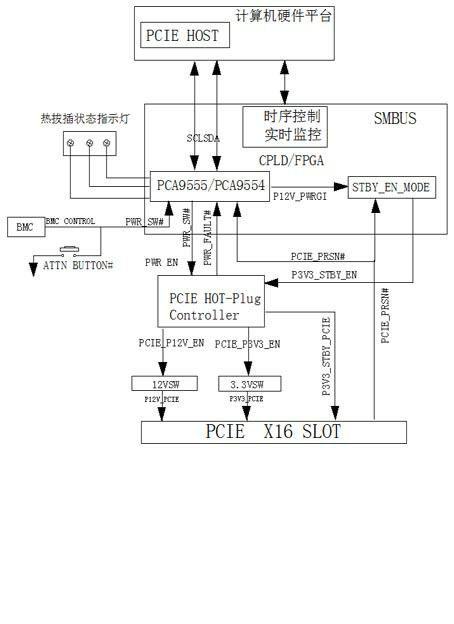

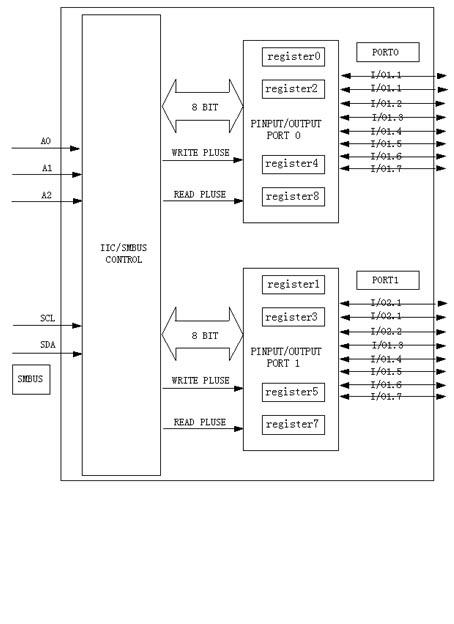

Method for realizing hot-plug of PCIE equipment by CPLD or FPGA

ActiveCN102662903AAvoid situations that shut down your computer systemImprove reliabilityEnergy efficient computingElectric digital data processingSequence controlProgrammable logic device

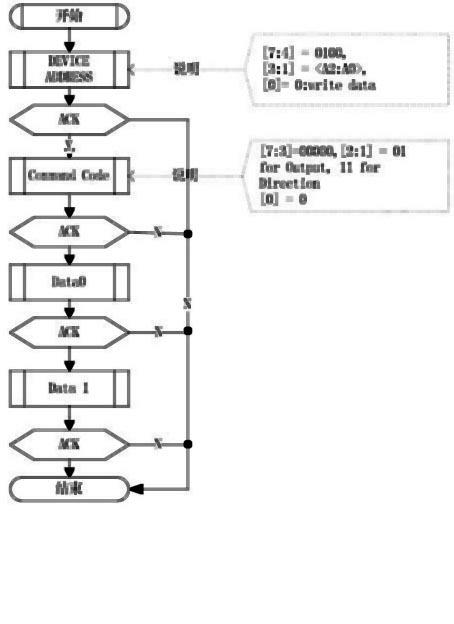

The invention provides a method for realizing hot-plug of PCIE (Peripheral Component Interconnect Express) equipment by CPLD (Complex Programmable Logic Device) or FPGA (Field Programmable Gate Array). A hardware system comprises PCIE HOST, CPLD / FPGA, PCIE HOT-PLUG CONTROLLER, and a PCIE insertion groove co-constructed system hardware platform, wherein multiple PCA9555 functional modules are hung under the PCIE HOST, and the function of converting SMBUS (System Management Bus) into GPIO (General Purpose Input / Output) is simulated in the CPLD / FPGA by the PCA9555 functional modules; different PCA9555 are distinguished by addresses A2, A1 and A0; the PCIE HOST communicates with the PAC9555 by the SMBUS; and the sequence control of a computer system and the hot-plug control of the PCIE equipment are integrated, and the PCA9555 function is realized by a programmable logic device CPLD / FPGA. Therefore, PCA9555 chips are not needed, the device use is reduced, the system cost is lowered, the power consumption is reduced, the board card space is saved, the computer system is lower in power consumption, and the reliability, stability and expandability are improved.

Owner:LANGCHAO ELECTRONIC INFORMATION IND CO LTD

Serial port awakening system not using handshake control line and serial port communication method

ActiveCN106372012ACorrectly identify interruptsFlexible collocationElectric digital data processingControl lineComputer science

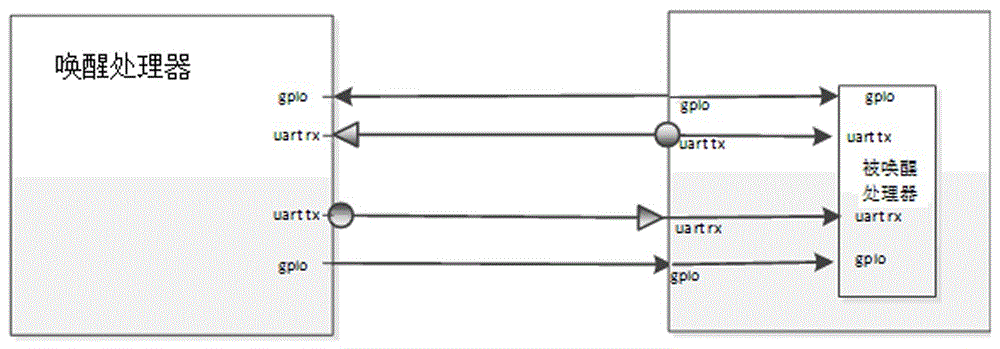

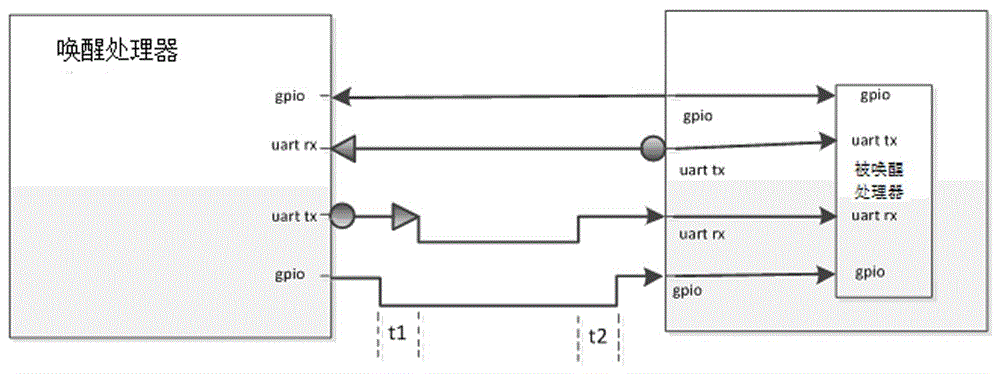

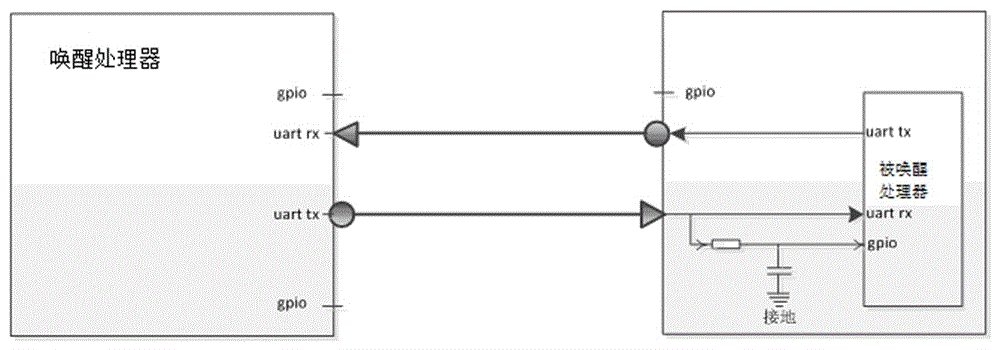

The invention discloses a serial port awakening system not using a handshake control line and a serial port communication method. The serial port awakening system comprises an awakening processor and an awakened processor, wherein a universal input / output end, a serial port receiving end and a serial port sending end are arranged on the awakening processor; the universal input / output end, the serial port receiving end and the serial port sending end are also arranged on the awakened processor; and the serial port receiving end of the awakened processor is connected with the universal input / output end of the awakened processor. The invention furthermore discloses a method for performing serial port communication by using the serial port awakening system. By use of the system and the method, hardware connection lines can be simplified, so that the mutual coupling property of the system is reduced; and due to use of standard serial port communication, the universality of the system can be improved.

Owner:长沙丰灼通讯科技有限公司

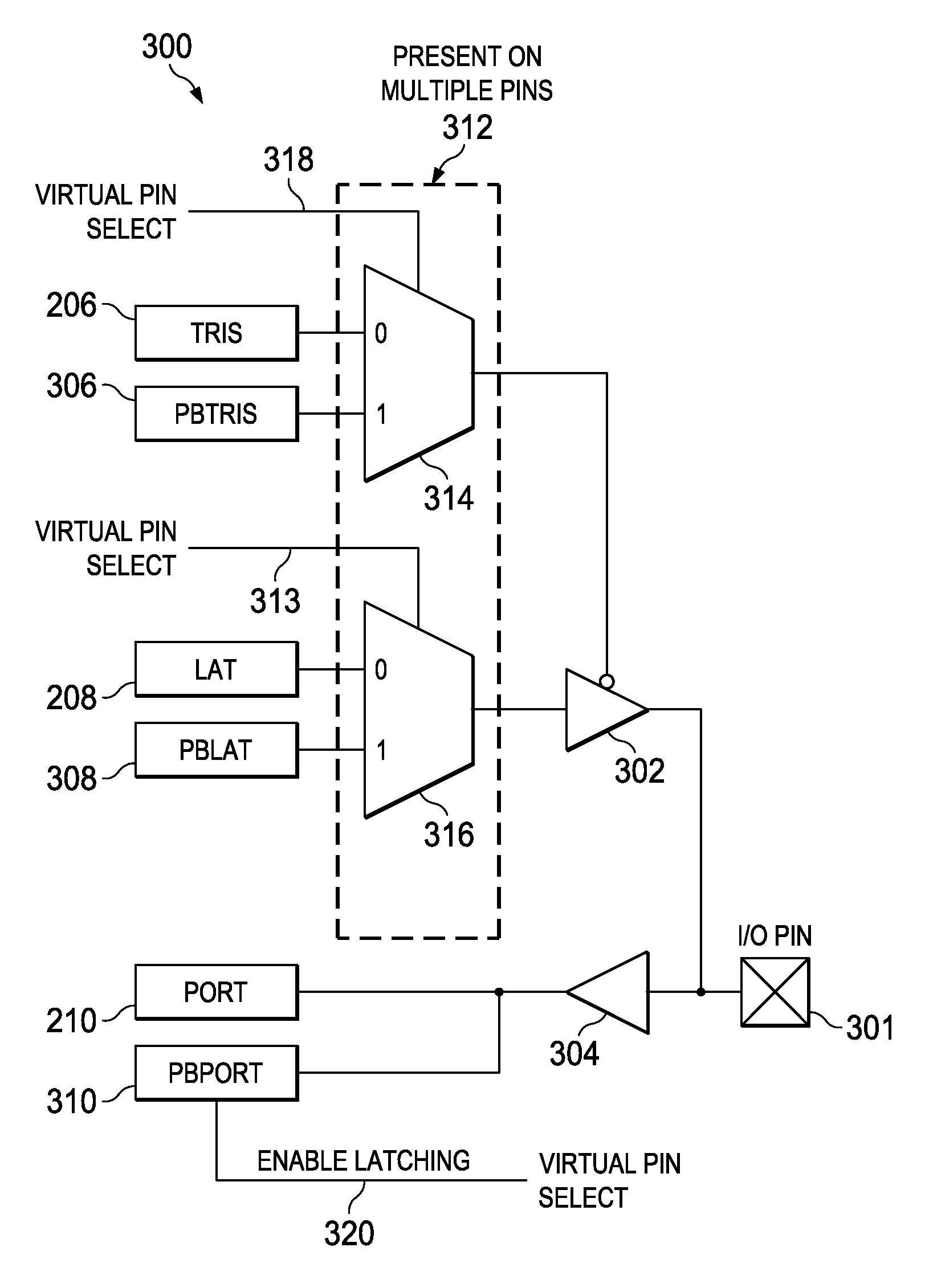

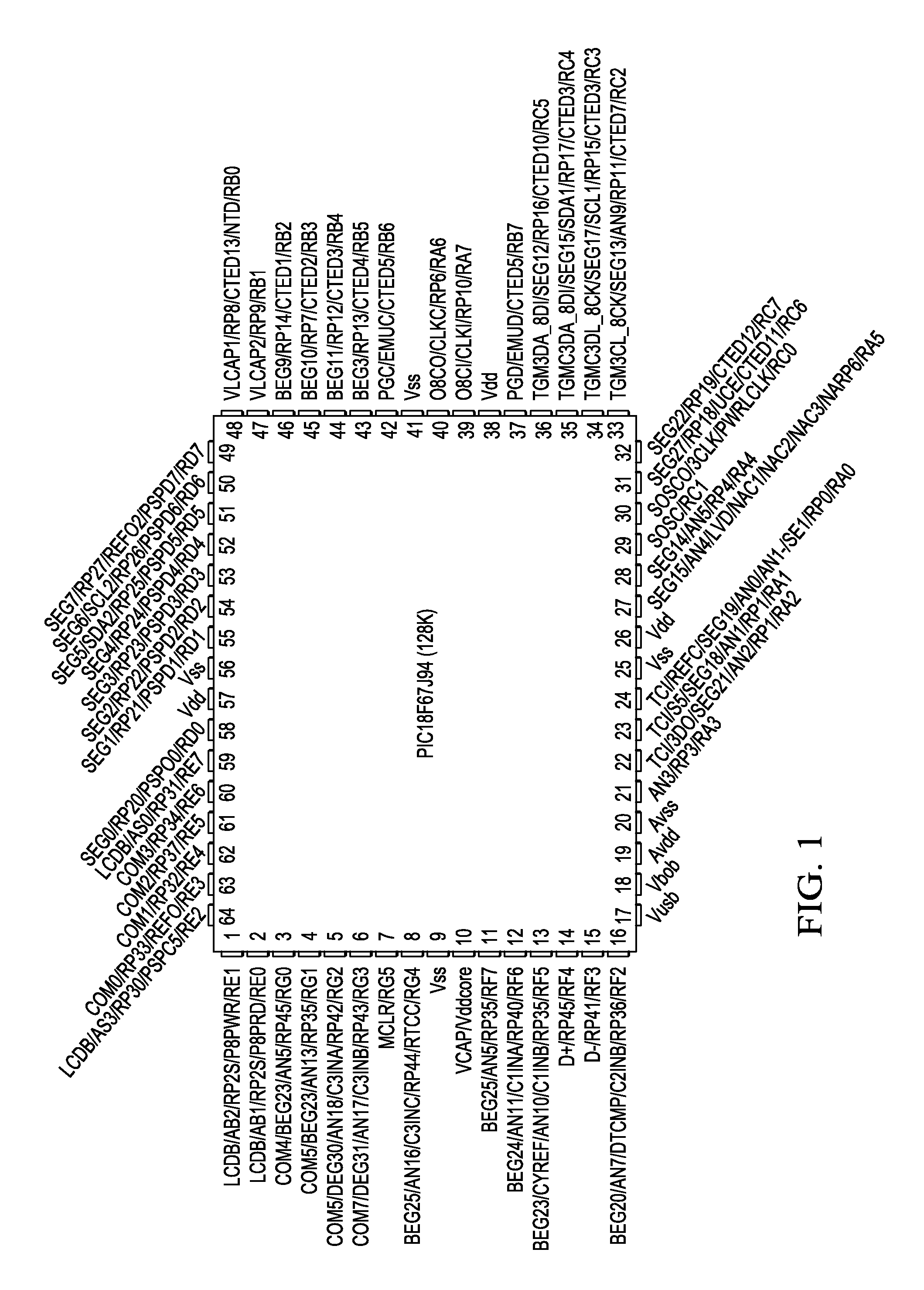

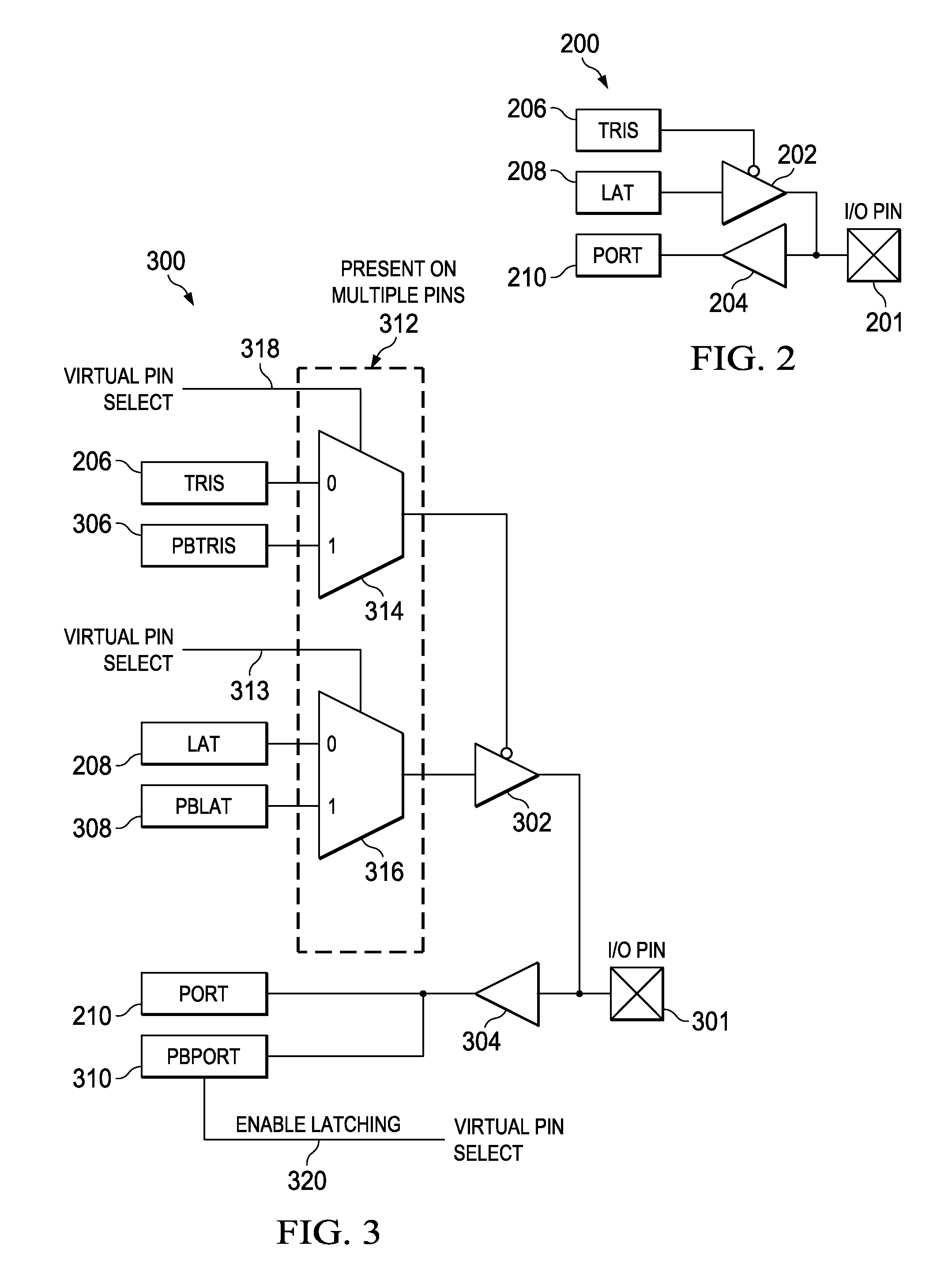

Virtual General Purpose Input/Output for a Microcontroller

ActiveUS20130080677A1Overcomes drawbackElectric digital data processingMicrocontrollerProcessor register

A microcontroller includes a general purpose input / output (GPIO) port having a plurality of bits coupled to a plurality of external pins; a first set of registers for providing at least one of first control and data input / output functionality of the GPIO port; a second set of registers for providing at least one of second control and data input / output functionality of the GPIO port; and a multiplexer and associated select register for controlling the multiplexer to control said GPIO port through either said first or second register set.

Owner:MICROCHIP TECH INC

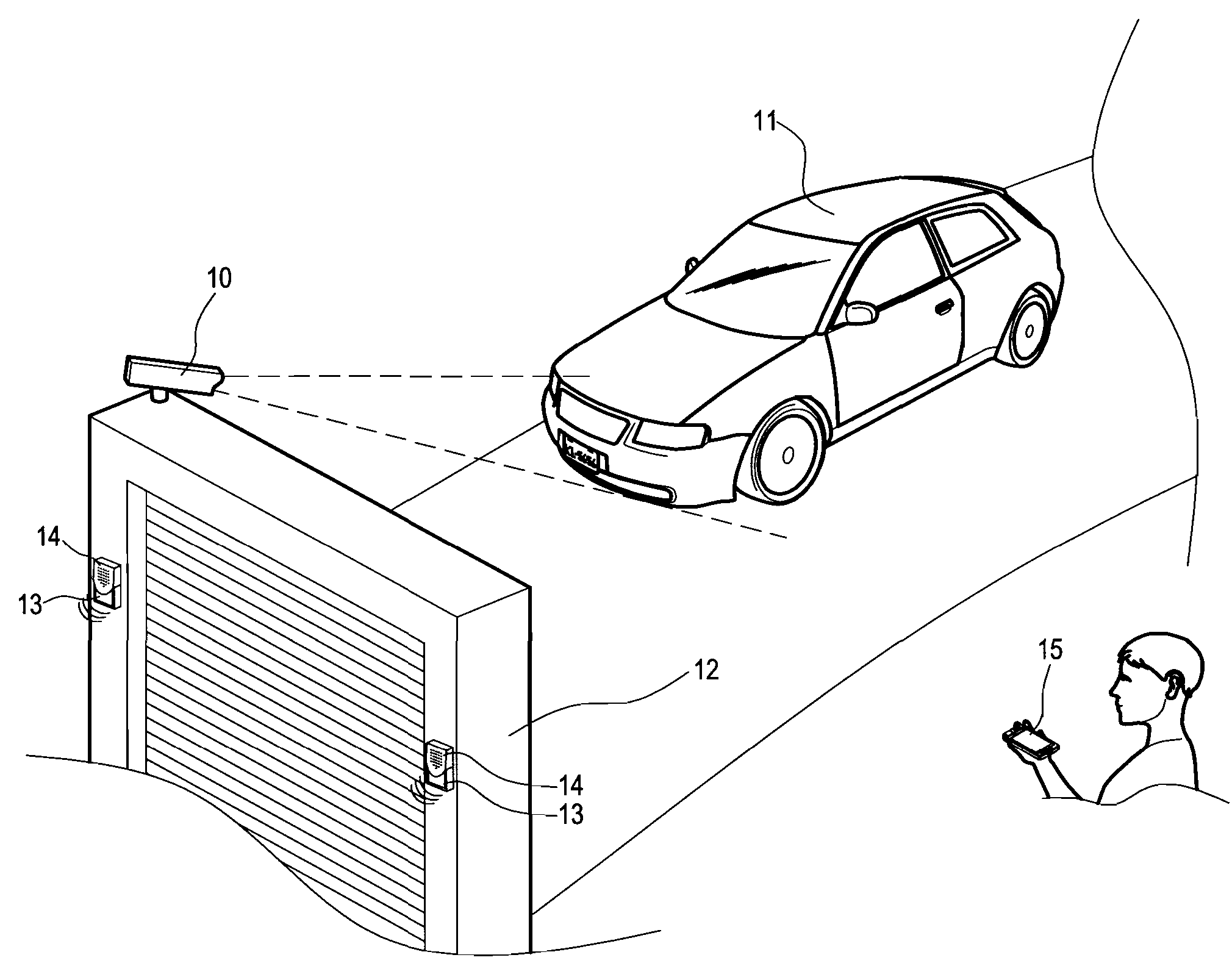

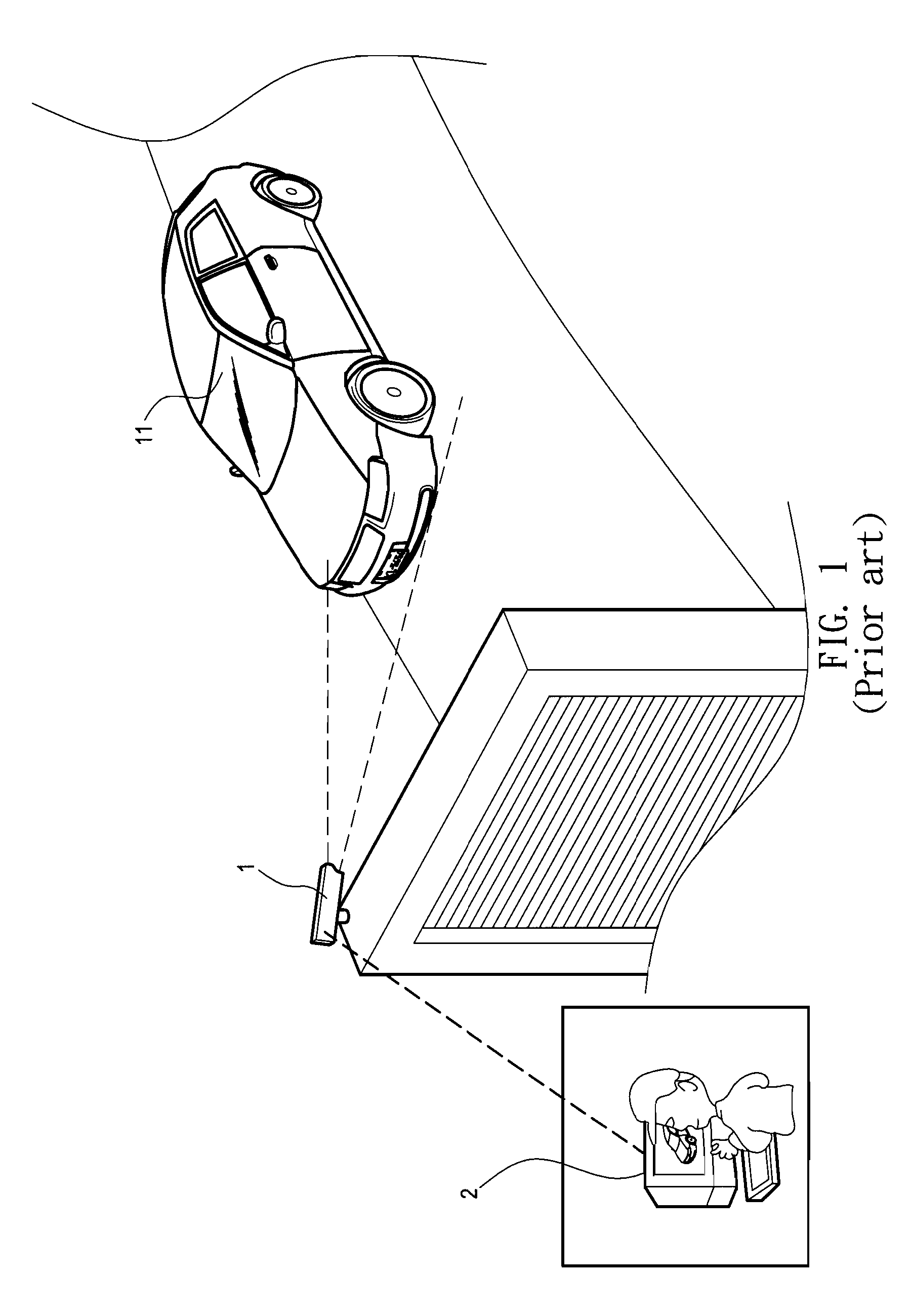

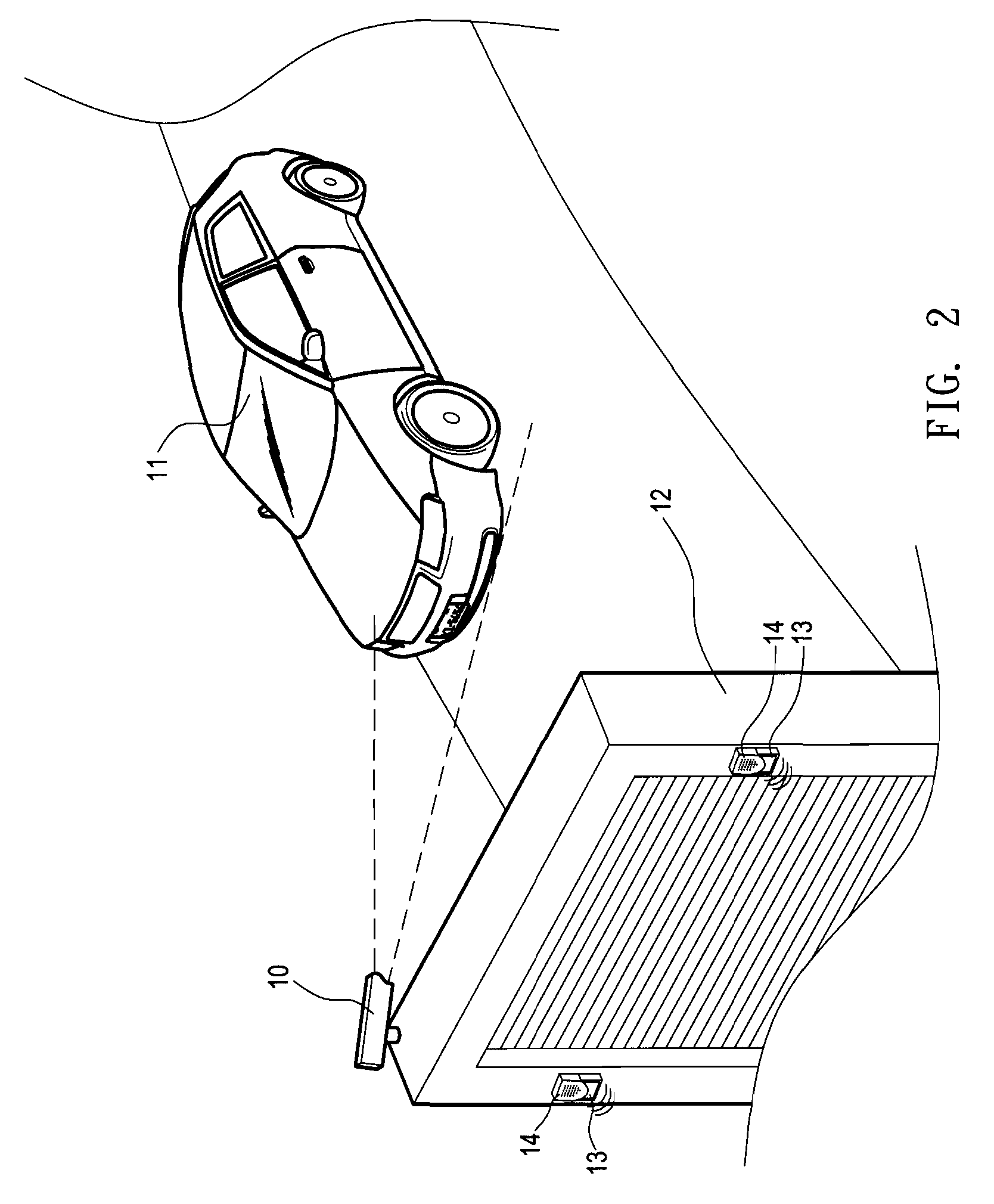

Camera with built-in license plate recognition function

InactiveUS20100052947A1Automatic detectionReduce the burden onIndication of parksing free spacesOptical signallingInformation repositoryImaging processing

A camera with a built-in license plate recognition function includes a license plate information base, a general purpose input / output (GPIO) port, an image-capturing module, a license plate image processor, a communication module, an audio-capturing module, and a processor. In the camera, the image-capturing module captures a license plate image when determining a vehicle enters / exits from a vehicle access control site; next, the license plate image processor segments and recognizes the image with a conventional image processing technique and compares the image with that in the license plate information base; and then the GPIO port controls the entrance / exit of the vehicle through a collapsible door, a sensor, and an alarm. Furthermore, remote control software may be installed on an external equipment, and the external equipment is connected to the communication module in a wired / wireless manner for achieving remote monitoring.

Owner:FARSIGHT INVESTMENT +1

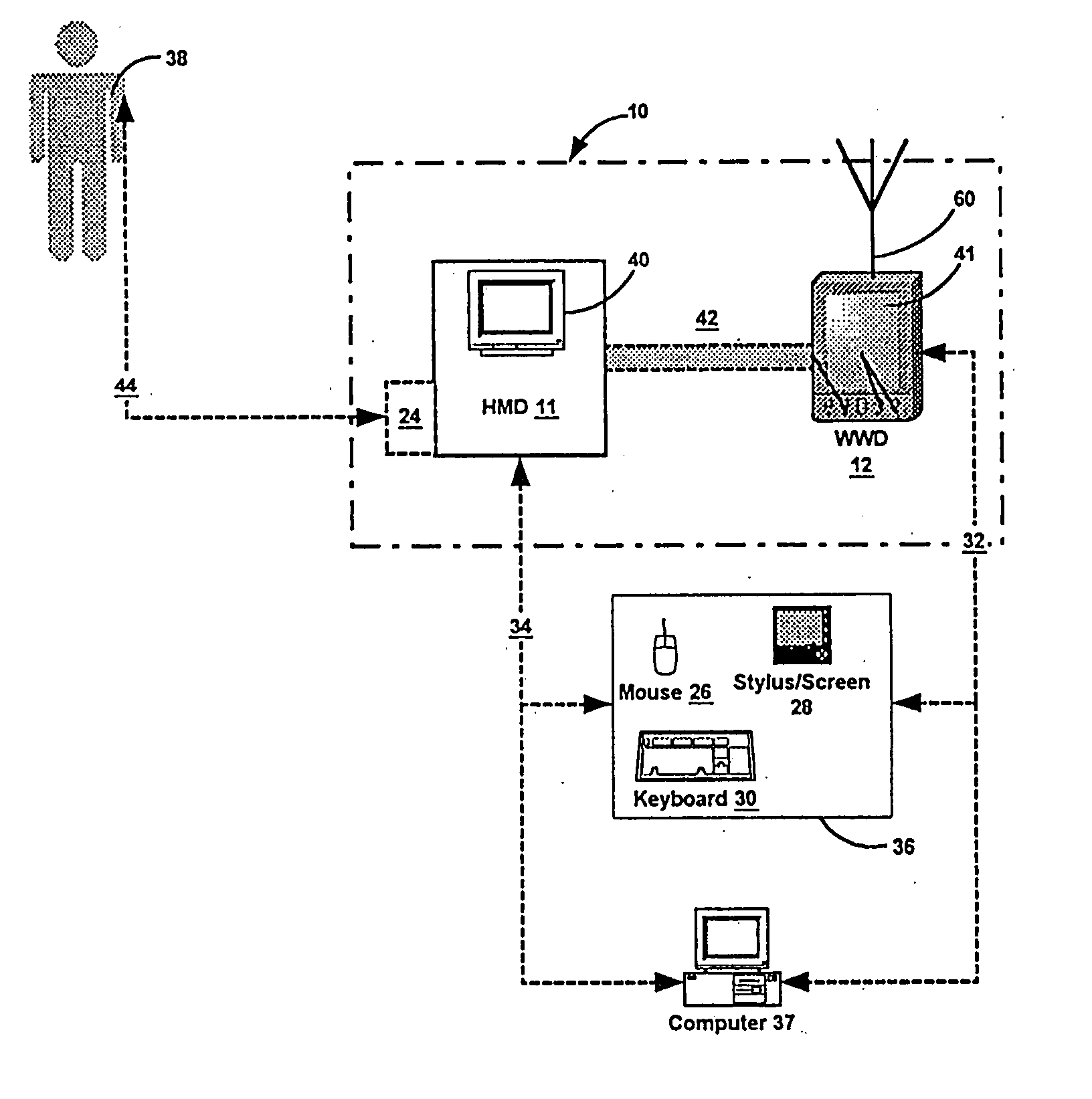

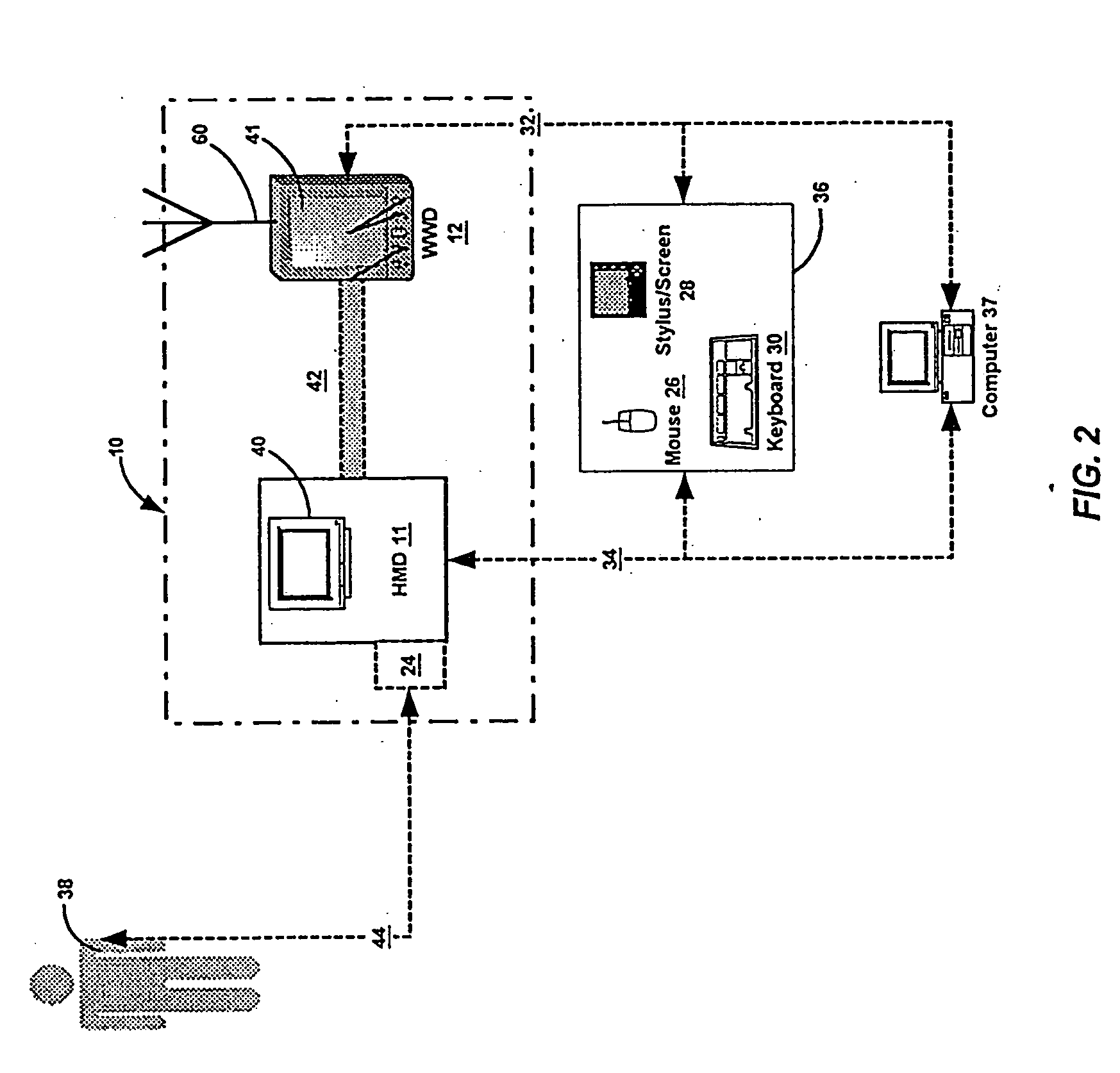

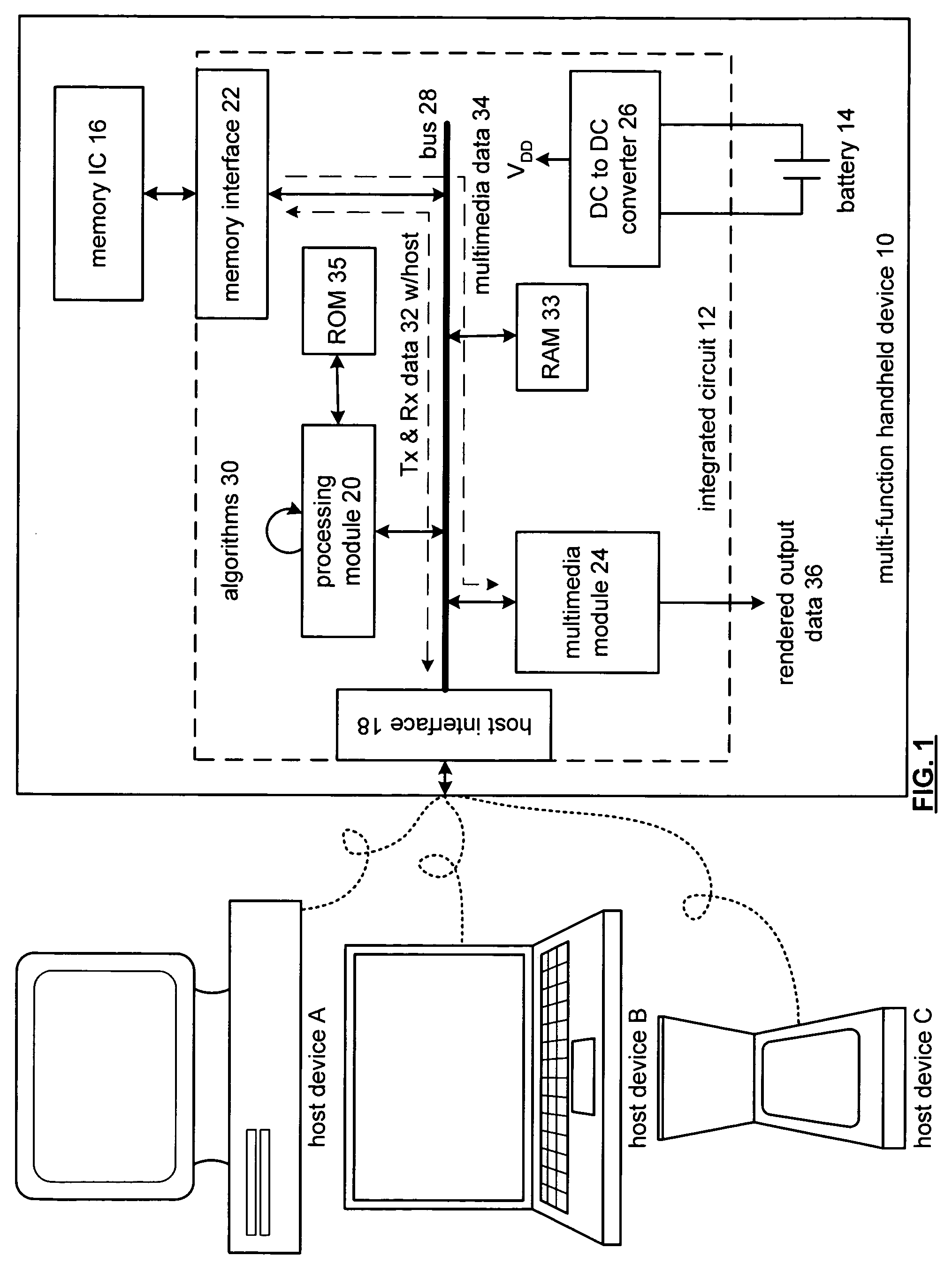

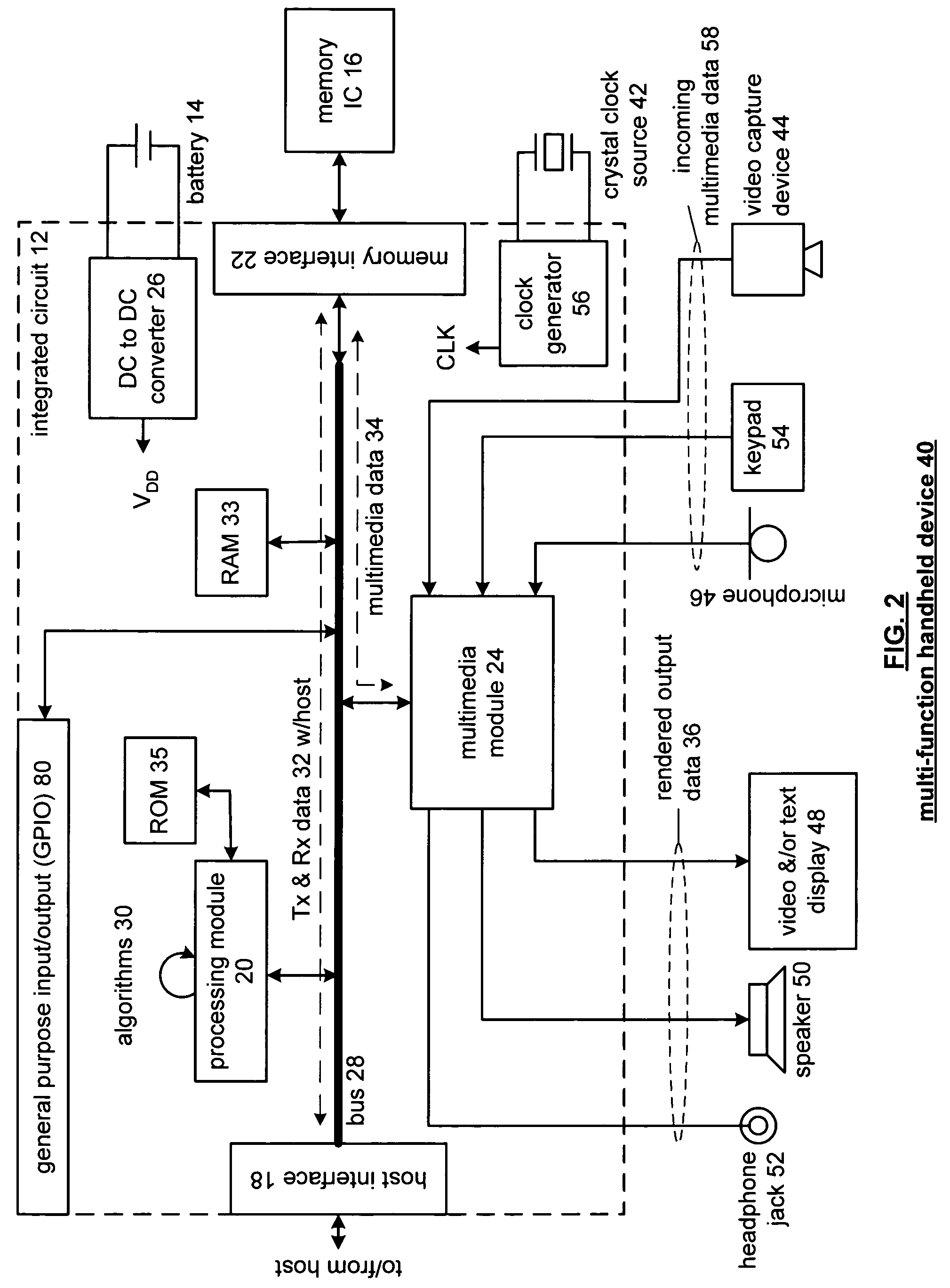

Method and apparatus for health and disease management combining patient data monitoring with wireless Internet connectivity

InactiveUS20050250995A1Maintain abilityReduced functionalityPhysical therapies and activitiesSurgeryDiseasePatient data

Embodiments of the invention provide a method and apparatus for a wireless health monitoring system for interactively monitoring a disease or health condition of a patient by connecting an internet-enabled wireless web device (“WWD”) to a health monitoring device which may be a medical device or other health related device such as an exercise machine. The WWD may be connected to the health monitoring device directly by a wired connection to a generic input / output port of the WWD using an optional adaptor if necessary. Alternatively, the WWD may be wirelessly connected to the health monitoring device, such as via an infrared or radio frequency connection, including using protocols such as Bluetooth or 802.11. The wireless connection may also employ an adaptor if necessary. The user may also input data to the WWD manually, such as by a keypad, keyboard, stylus, or optionally by voice command. The health related data is transmitted from the WWD to a server using standard internet protocols. The server calculates a response using a software program which may include an algorithm or artificial intelligence system, and may further provide for review by a physician or health specialist. The user may interact with the server. For example, the server transmits a response to the WWD, and the user may answer the response or provide other information.

Owner:KONINKLJIJKE PHILIPS NV

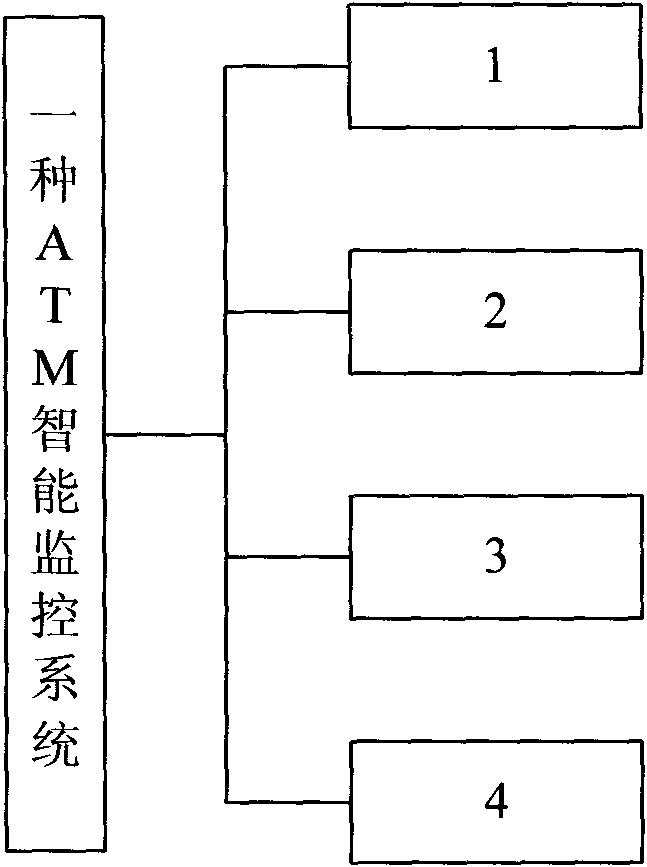

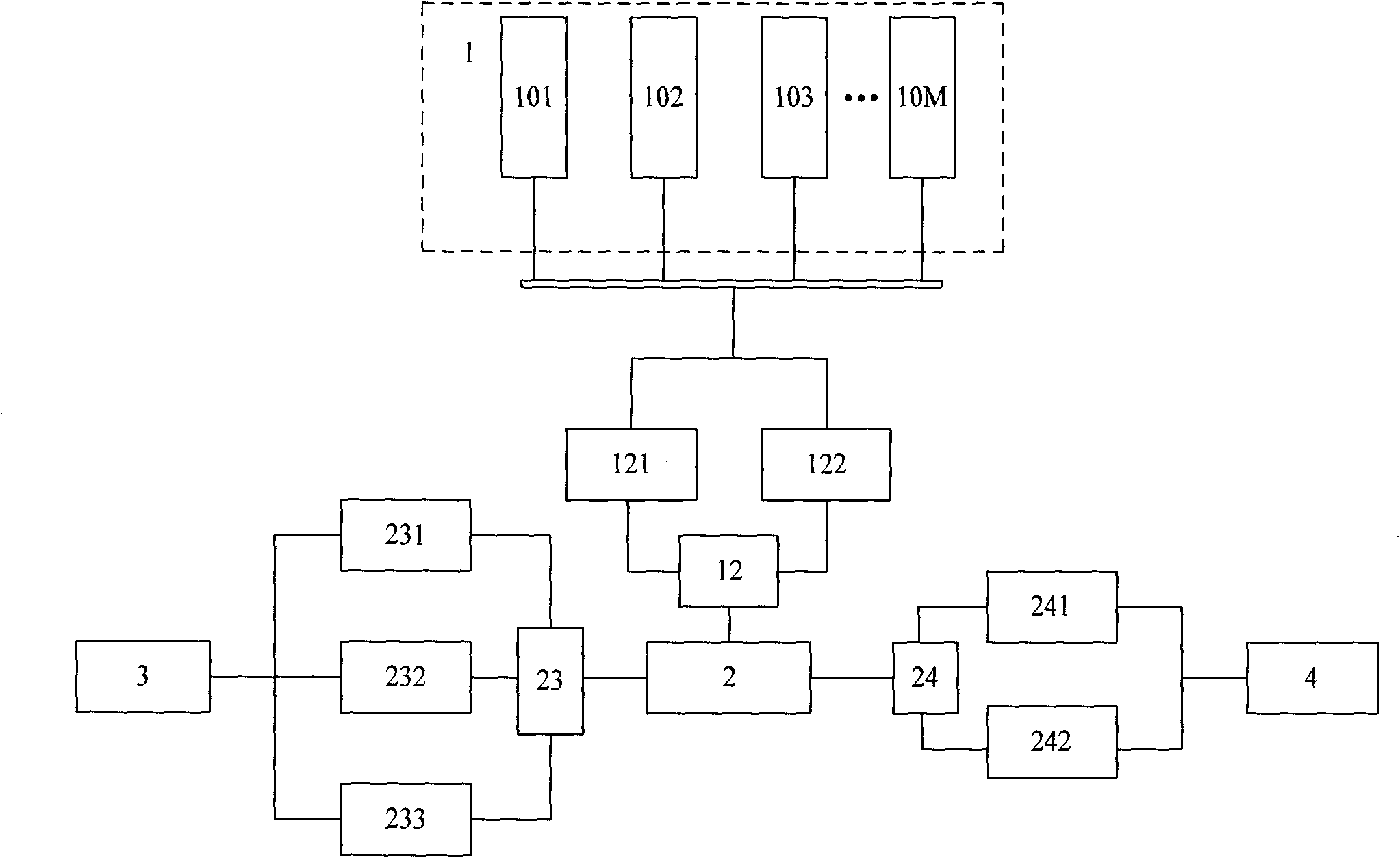

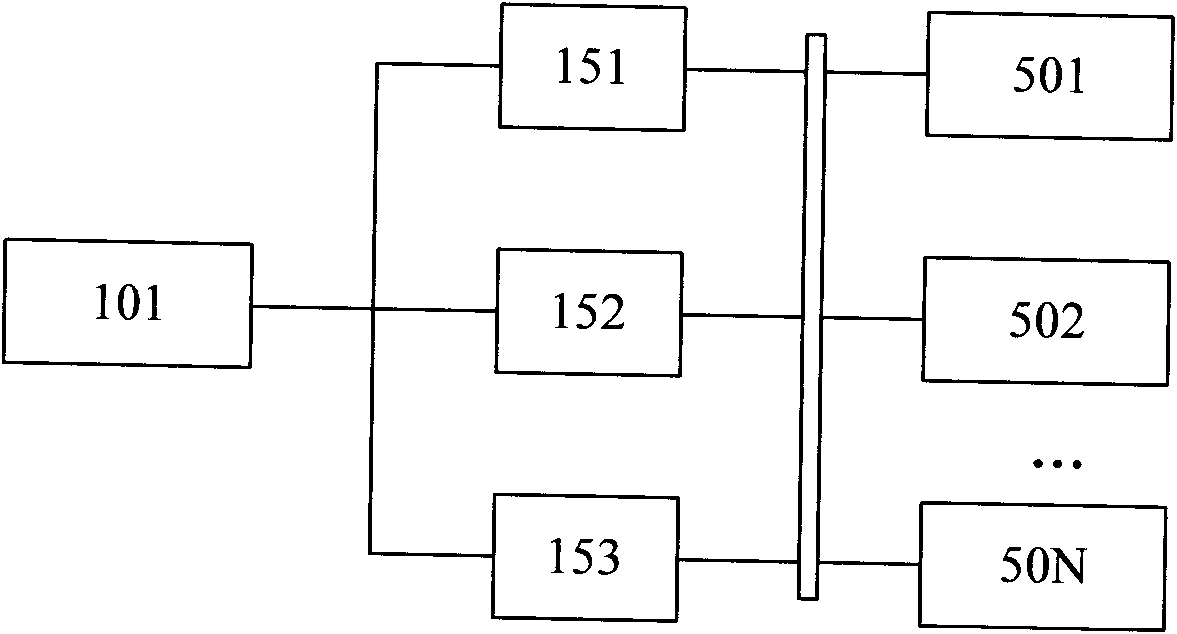

ATM (Automated Teller Machine) intelligent monitoring system

ActiveCN101894428AComplete banking machinesClosed circuit television systemsPrivate networkVideo transmission

The invention discloses an ATM (automated teller machine) intelligent monitoring system which comprises ATM intelligent video analysis devices, a central server, a database, monitoring terminals, and the like. In a self-service bank, a plurality of ATM intelligent video analysis devices are connected with the central server through a bank private network or the Internet, the database is connected with the central server through the bank private network or the Internet or connected with the central server through a direct communication mode, the monitoring terminals are connected with the central server through the bank private network or the Internet, and the ATM intelligent video analysis devices is connected with one ATM through two analog video paths and a GPIO (General Purpose Input Output). The central server also comprises an alarm receiving server module, a video transmission service module, a face comparison service module, an alarm retrieval service module and a device management service module, and the database also comprises a device parameter information sub-database, an alarm information sub-database, a blacklist information sub-database, a monitoring terminal connection information sub-database and a user right information sub-database. The invention is suitable for a high-intelligence monitoring system of bank ATMs.

Owner:BEIJING HISIGN TECH

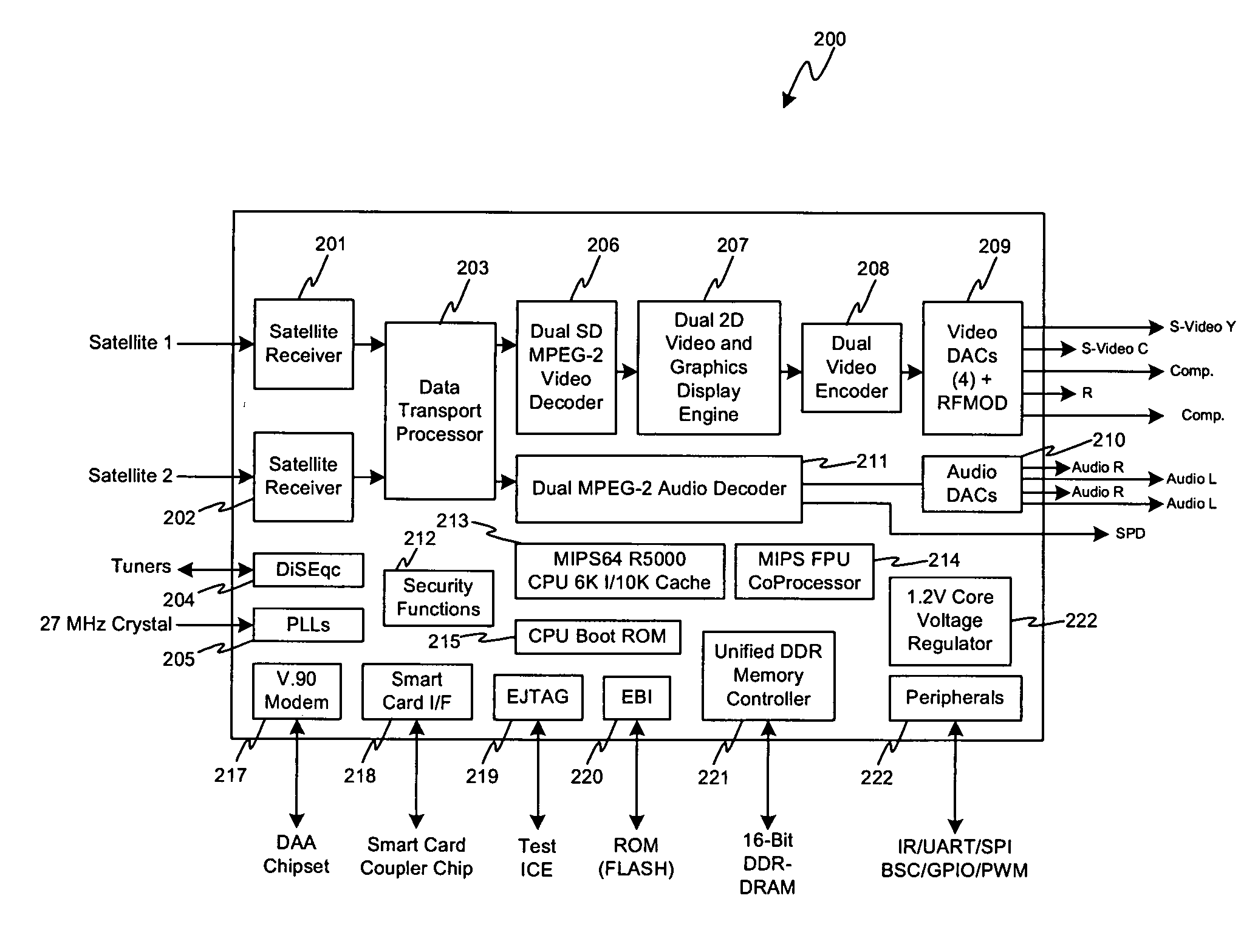

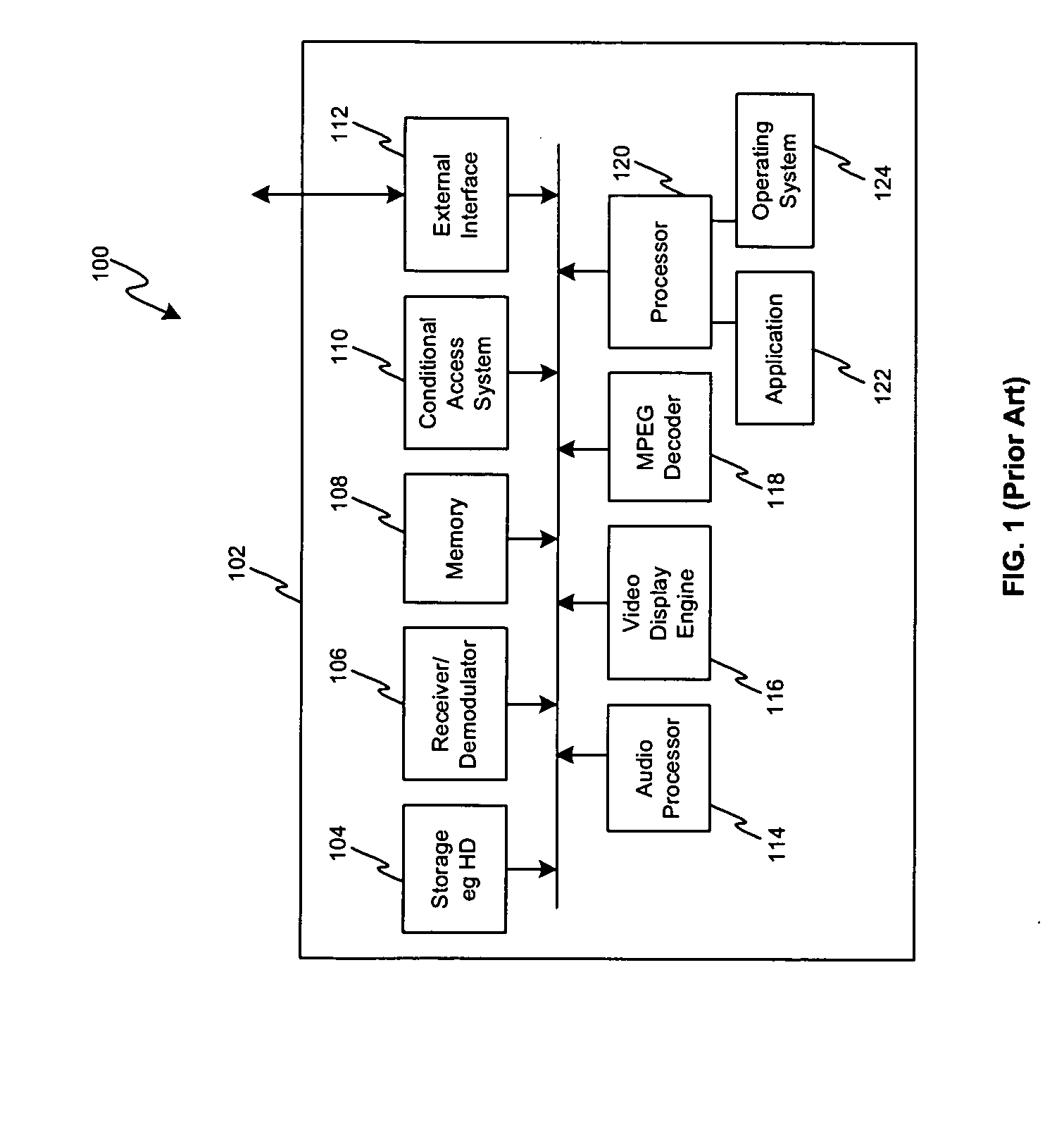

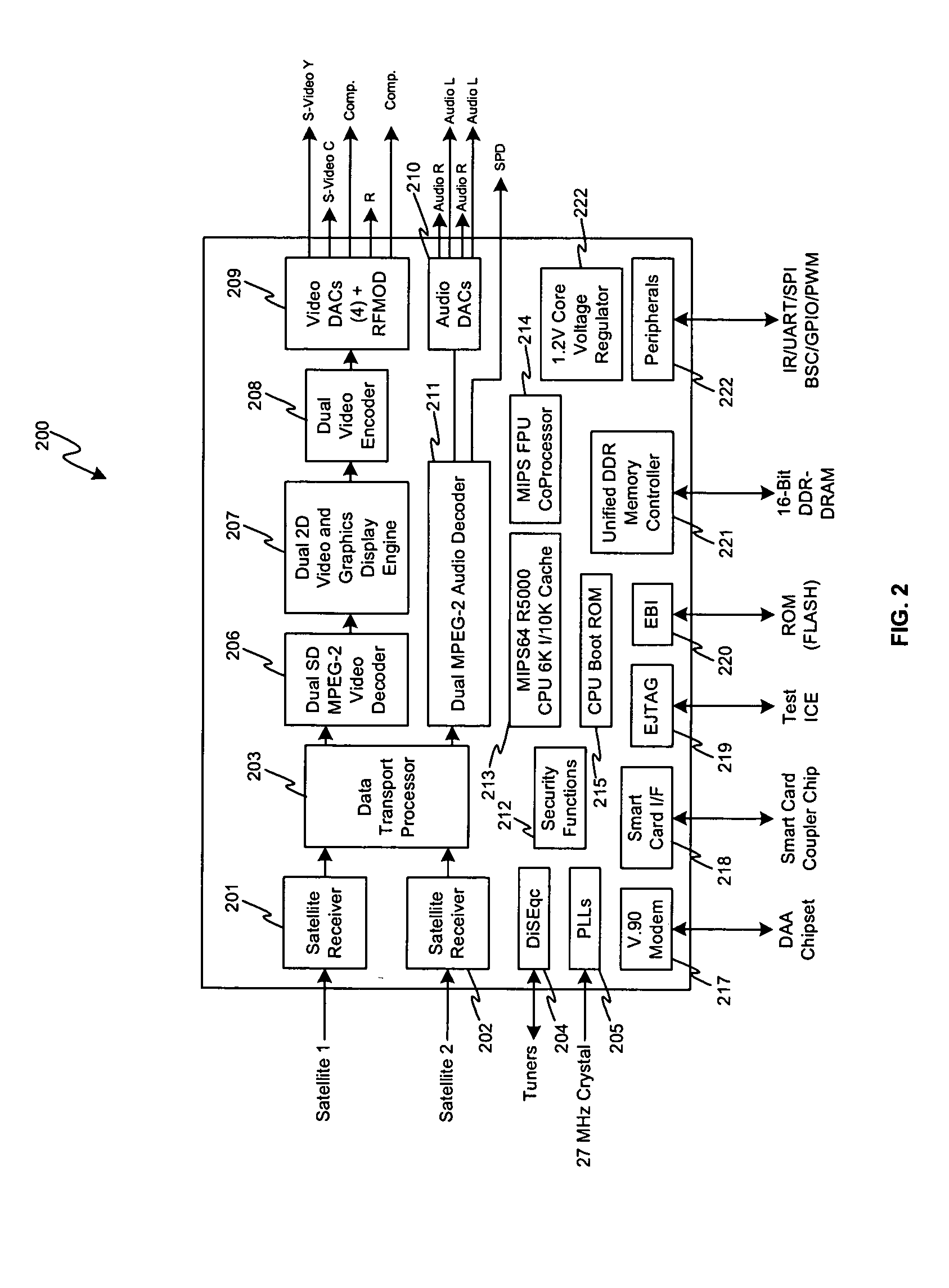

Method and system for single chip satellite set-top box system

Certain embodiments of the invention may be found in an single chip satellite set-top box solution that comprises demodulation, decoding and audio / video display functions integrated within a single chip. The single chip solution for the satellite set-top box is adapted to provide demodulation, display, and other related set-top box functions for a system that may be adapted to handle two incoming data streams modulated using an 8PSK, 8PSK-turbo or QPSK scheme, for example. Accordingly, the single chip satellite set-top box solution comprise dual 8 PSK / 8 PSK-turbo / QPSK demodulators, a MIPS CPU, a 16-bit DDR-SDRAM, graphics display capability for handling two channels, and audio / video decoders and DACs for handling two incoming channels. The single chip satellite set-top box solution may also comprise integrated peripheral support for major set top box functions including a smart card interface, IR receivers, and general purpose input / output (GP / IO) pins.

Owner:BROADCOM CORP

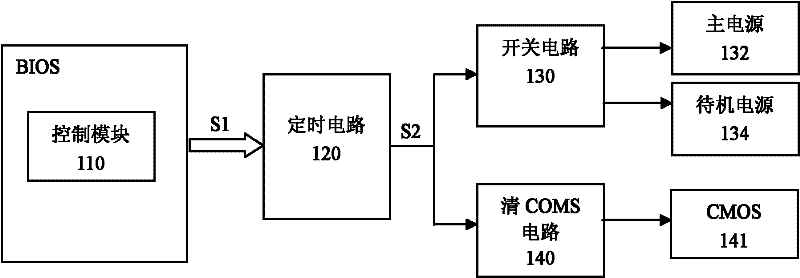

Computer, and computer startup management system and method thereof

ActiveCN102221864AEasy to useReduce maintenance costsDetecting faulty computer hardwareData resettingCMOSReal-time clock

The invention relates to a computer, and a computer startup management system and method thereof. The computer startup management system comprises a control module, a timing circuit, a switching circuit and a complementary metal oxide semiconductor (CMOS) clearing circuit, wherein the control circuit is in a basic input / output system (BIOS) and outputs a first control signal through a general purpose input / output (GPIO) interface, and the first control signal is at a first level in startup and triggered into a second level when the BIOS definitely can normally finish running is determined by the setting of the first control signal; the timing circuit is used for receiving the first control signal, timing and outputting a second control signal when the first control signal is still kept at the first level till the first predetermined time TH; the switching circuit is used for immediately switching off a main board power supply when the second control signal is received; and the CMOS clearing circuit is used for constantly lowering real time clock reset (RTC RST) signals at a third predetermined time TJCC period when the second control signal is received and after a second predetermined time TD is delayed so as to clear CMOS. By implementing the system and the method, the CMOS setting of the last normal startup can be automatically recovered without any manual operation or intervention, and the system is restarted.

Owner:EVOC SMART IOT TECH CO LTD

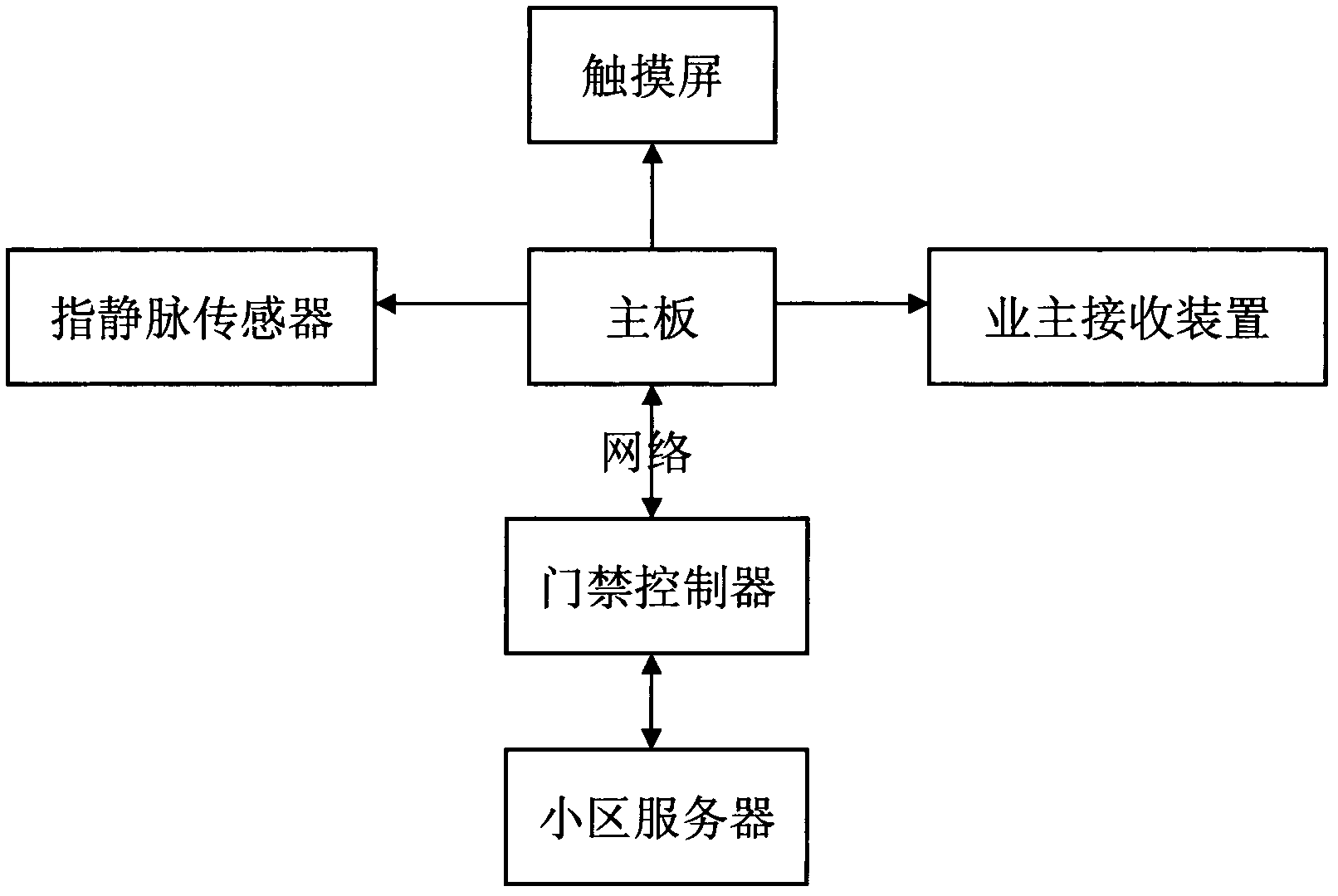

Finger vein villa management system

InactiveCN103136821AImprove performanceImprove reliabilityIndividual entry/exit registersHuman bodyInternal memory

The invention provides a finger vein villa management system which utilizes a finger vein recognition technology and comprises a high-performance ARM board, a non-contact sensor which utilizes infrared to collect deoxidized hemachrome in a finger of human body, a display screen with a touch screen, a terminal which is composed of wireless transmission devices, a entrance guard control system and relevant personal computer (PC) servers. The high-performance ARM board is an ARM high performance board with a central processing unit (CPU) which is at least above ARM Cortex-A8 and possesses a floating point arithmetic function and an internal memory which is more than 512 mega byte. The high-performance ARM board comprises a universal serial bus (USB) interface, a general purpose input / output (GPIO) interface, a general serial port RS 232, a general serial port RS 485 and a network interface and is connected with the finger vein entrance guard through the USB interface. A card issuer is a PC computer which is connected with an entrance guard controller through the recommend standard (RS) 232 and is connected to a villa management server. The finger vein villa management system utilizes the finger vein recognition technology, possesses a non-contact identity to conduct verification, is high in safety performance and is convenient to use.

Owner:CHANGSHU ANZHI BIOLOGICAL IDENTIFICATION TECH

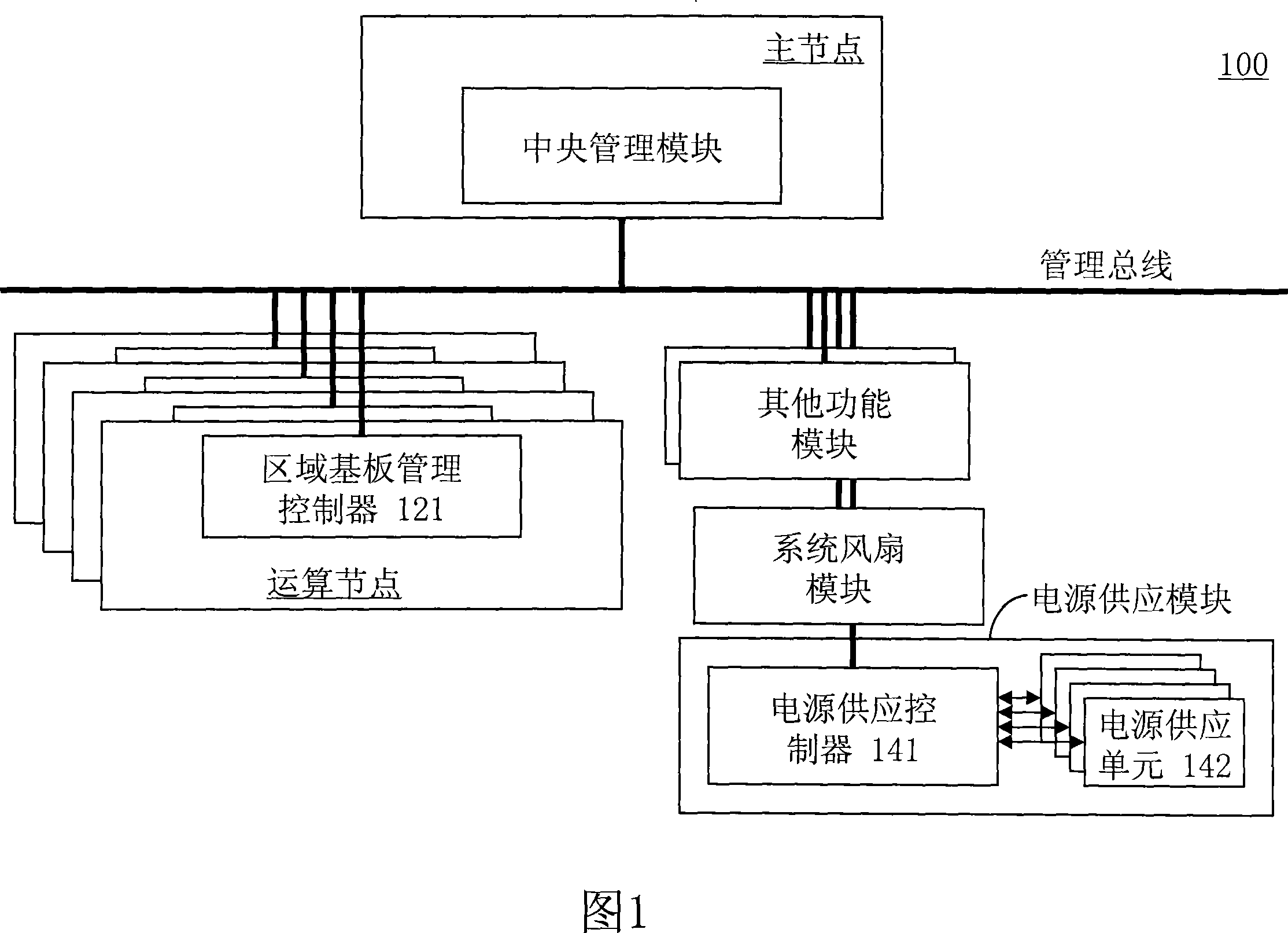

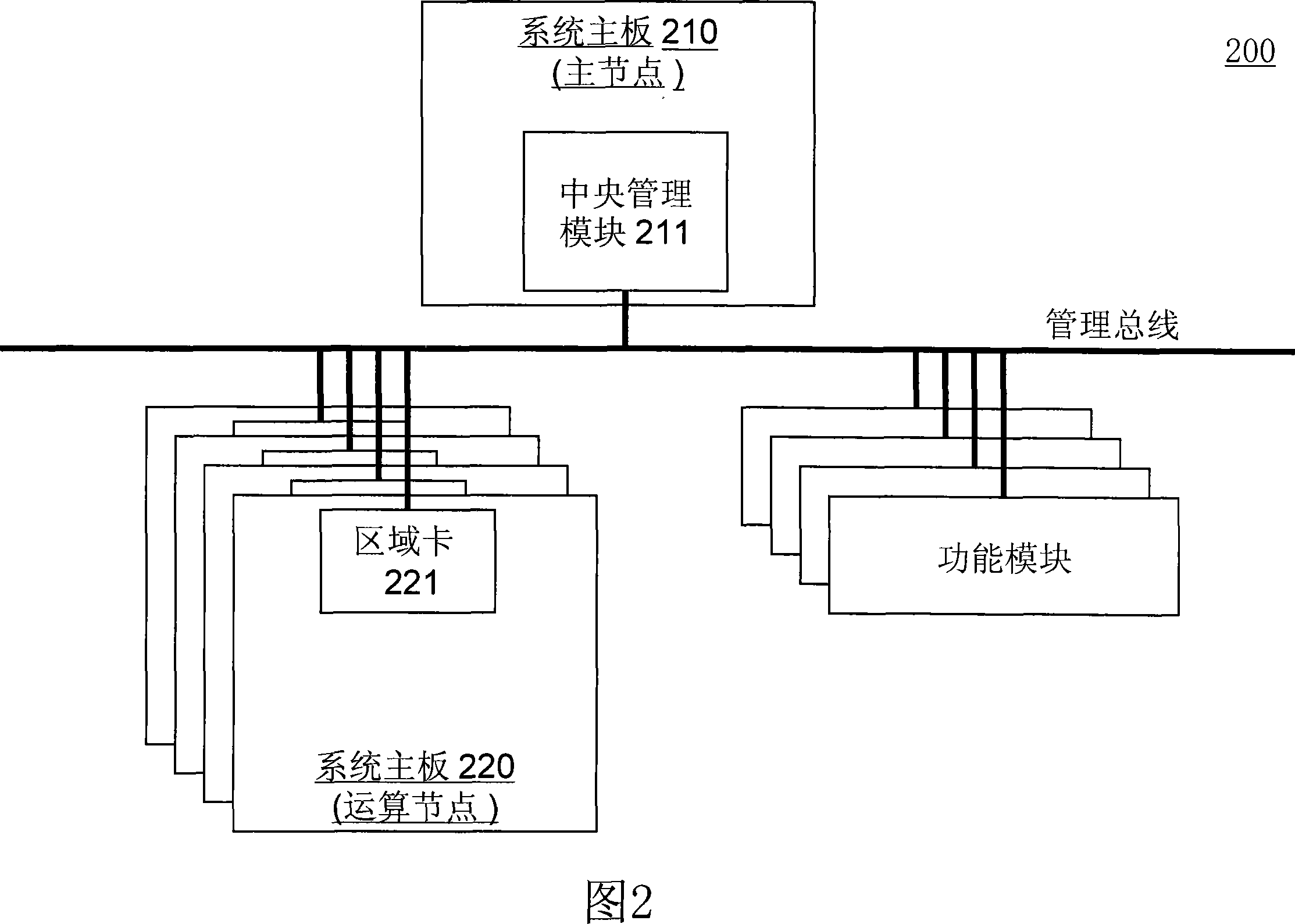

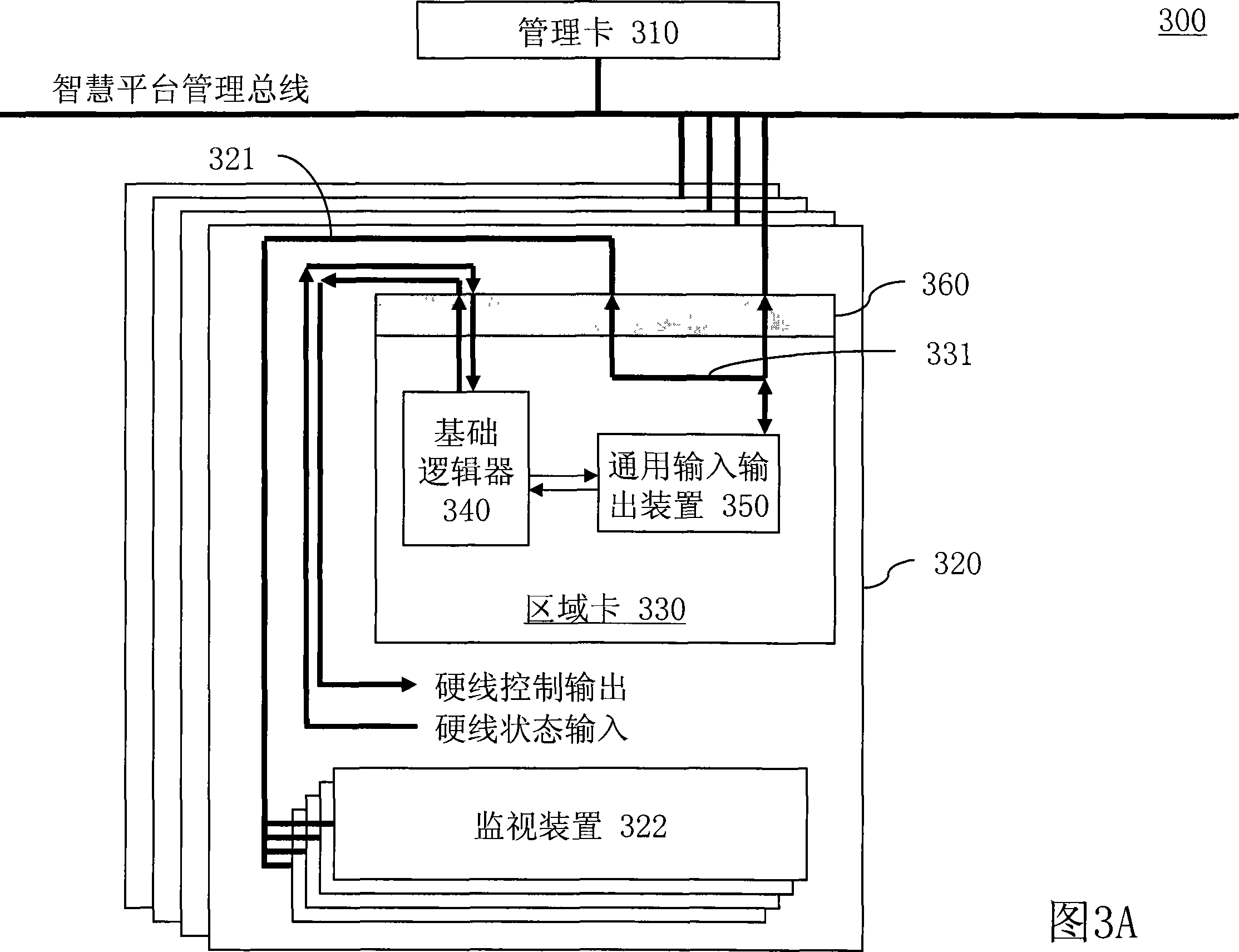

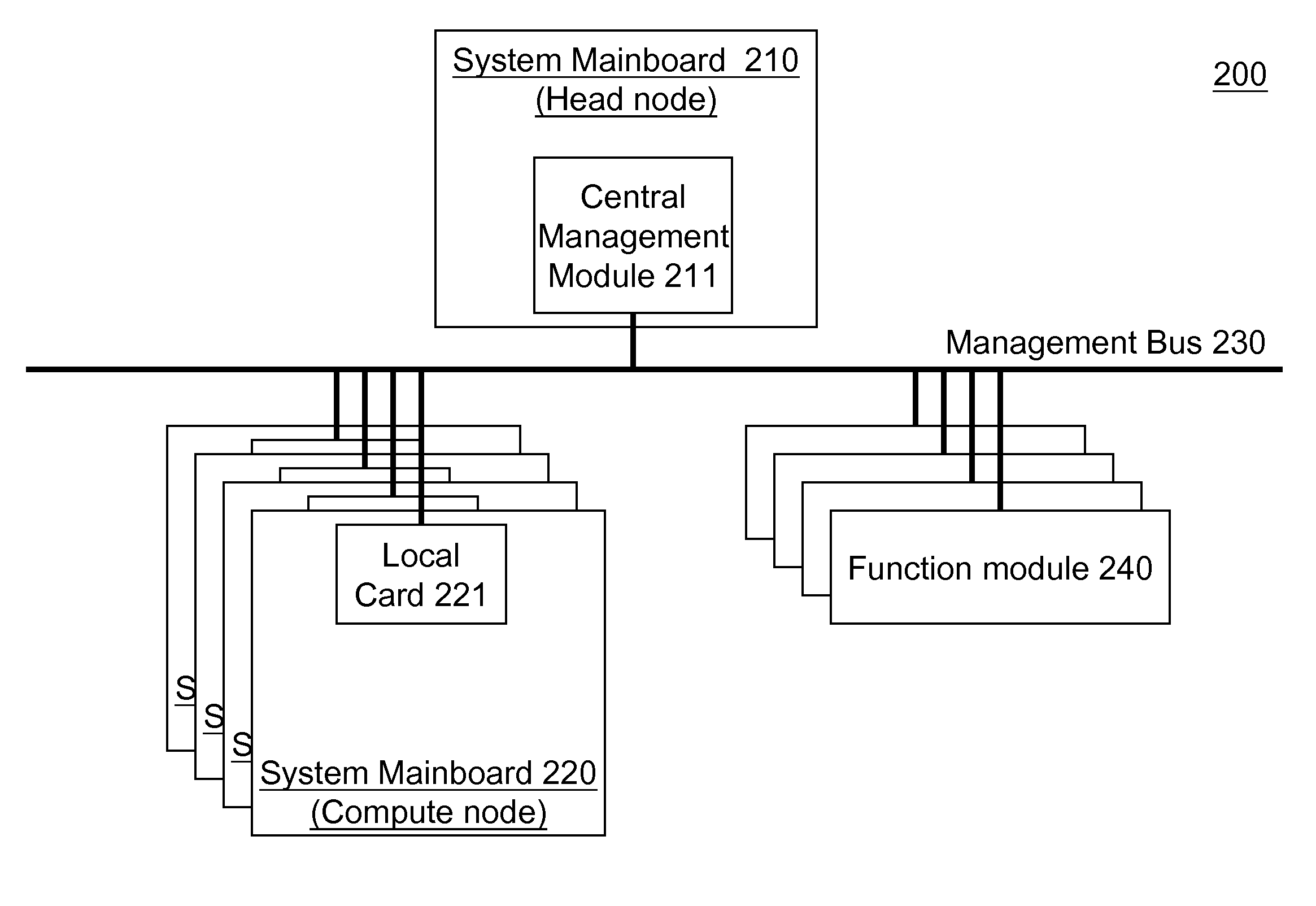

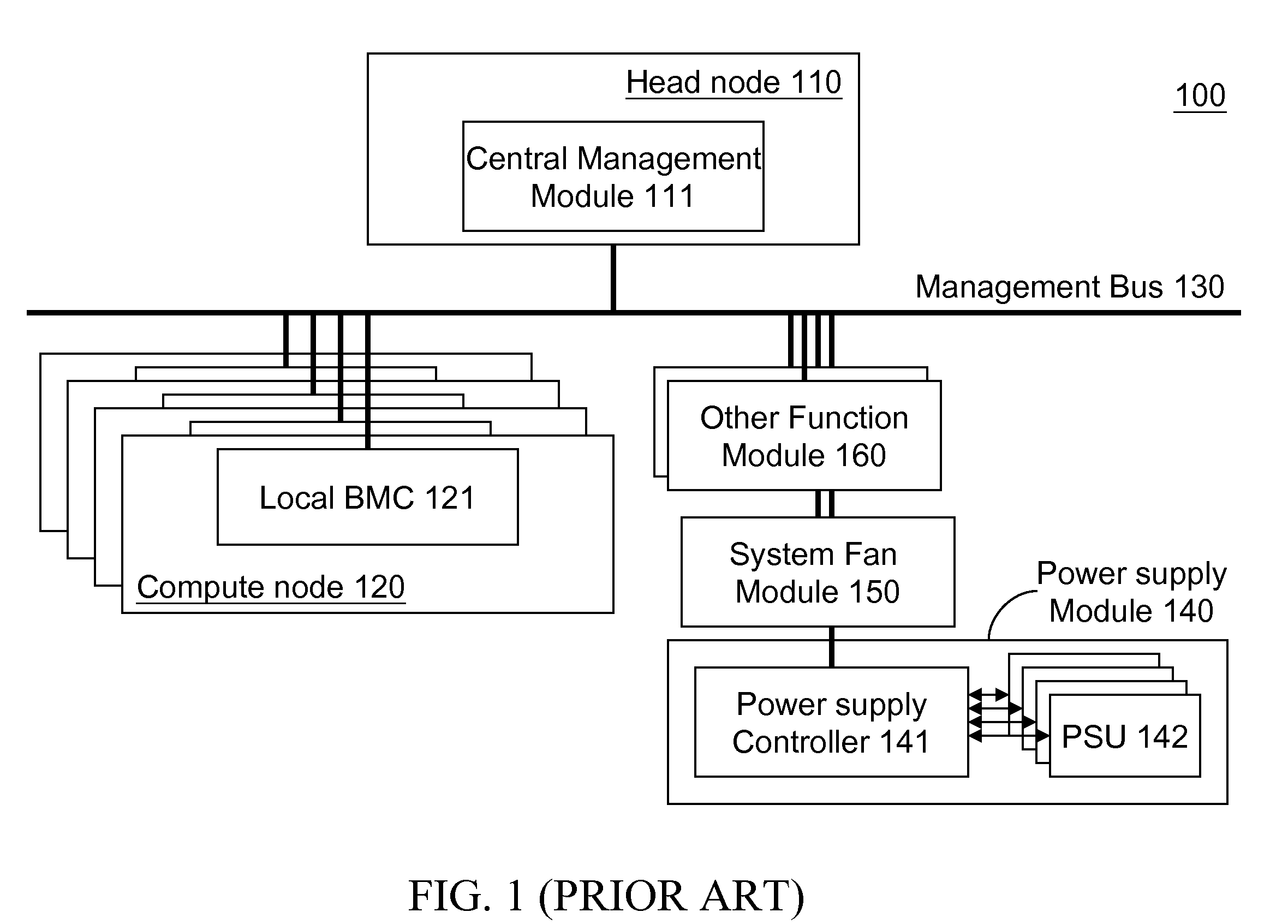

System management configuration of multiple main board system

The invention discloses a system administration rack for monitoring and controlling multi-mainboard system with complex number system mainboard. The system administration rack comprises area card for selectively replace a manage card based on substrate management controller on system mainboard. The area card mainly comprises general purpose input output device (GPIO device) basic logic device. A central management module also is used for system administration rack, the system mainboard is monitored and controlled by management bus and management card or area card. The area card monitors state signal on the mainboard of the monitoring system based on the order signal from the central management module, at the same time the customized monitoring function is provided. Thus the area card can promote the resilience performed by the system administration rack and the cost required by a lot of management cards based on the substrate management controller and maintenance support is reduced.

Owner:HUANDA COMPUTER (SHANGHAI) CO LTD

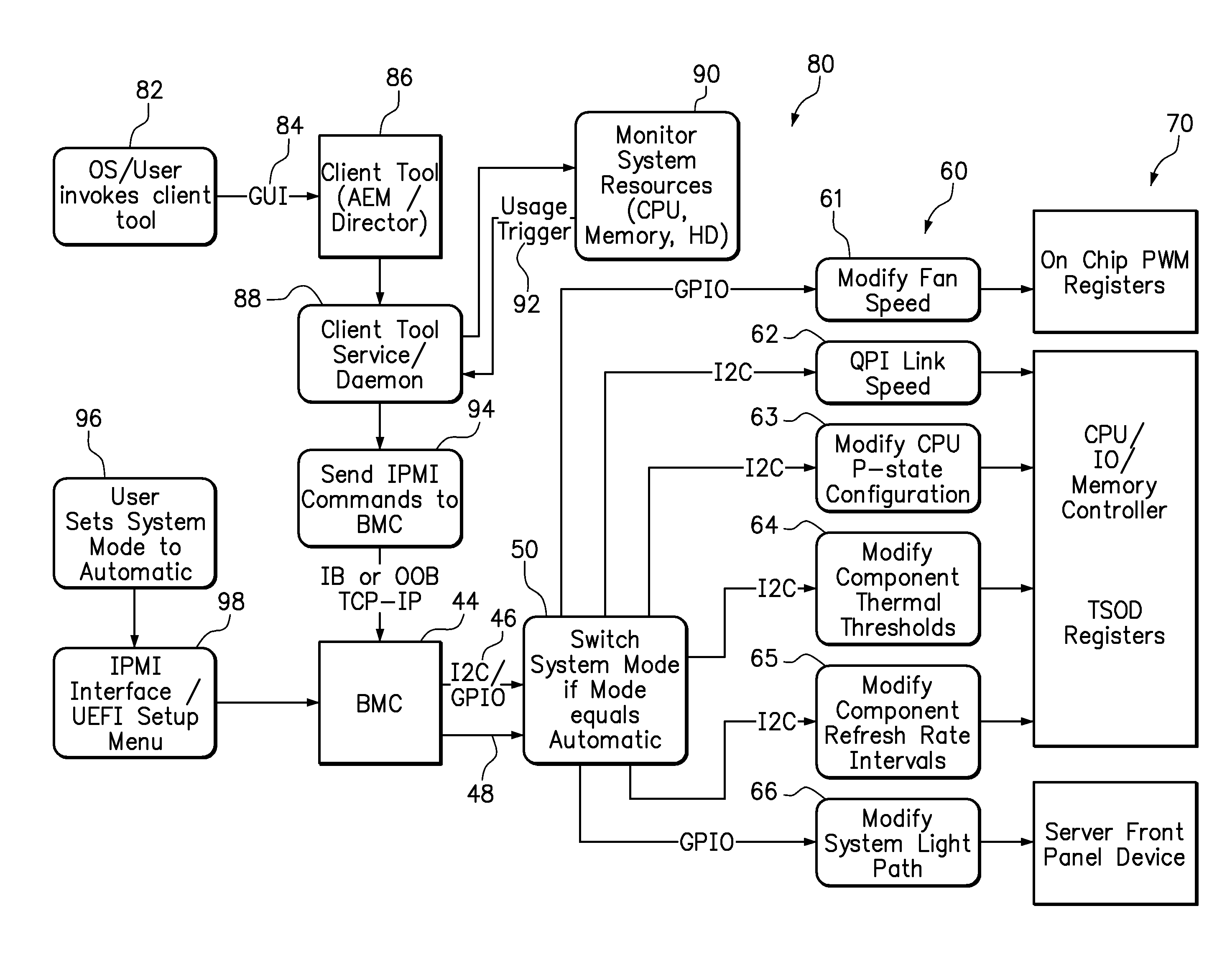

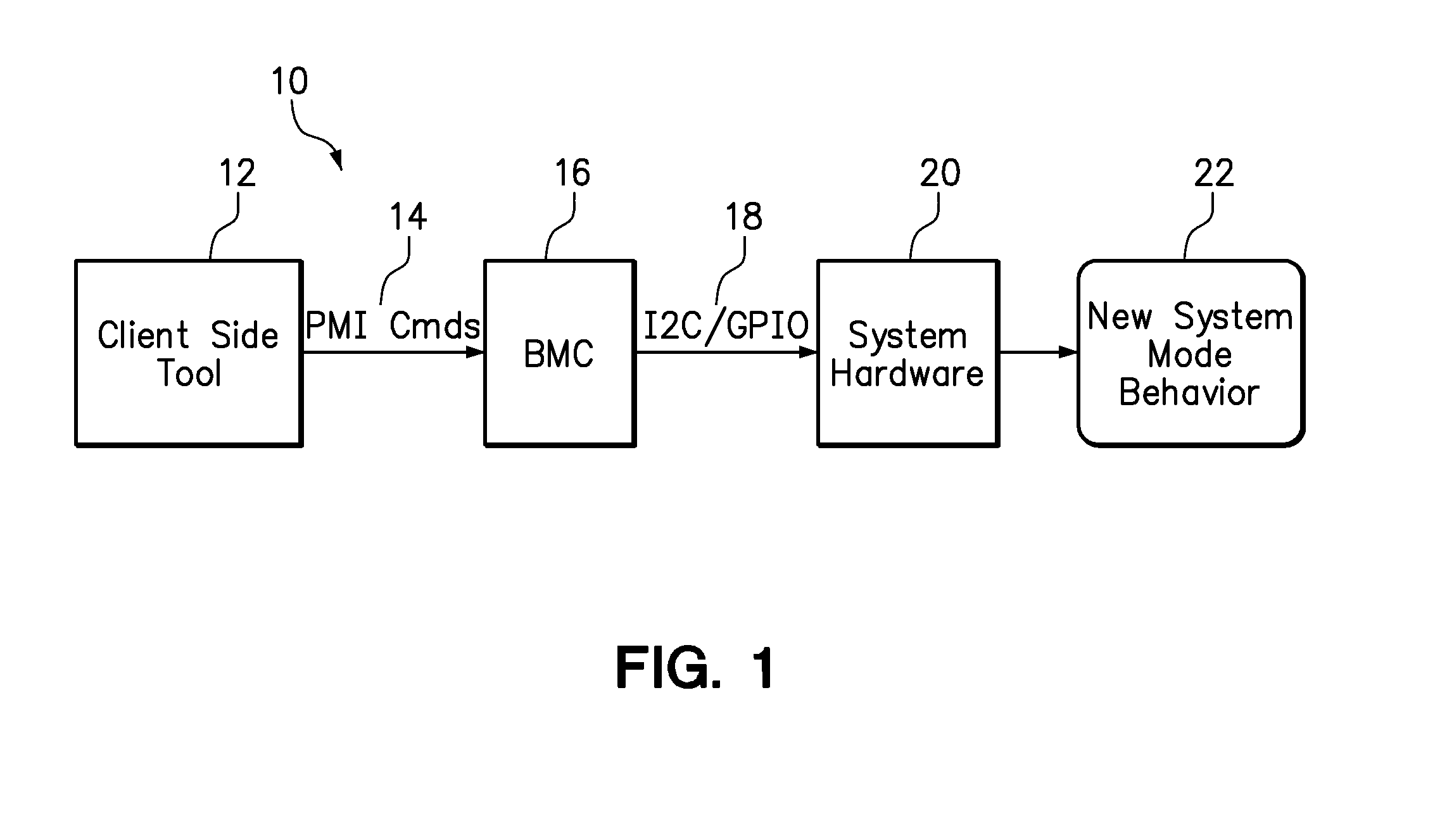

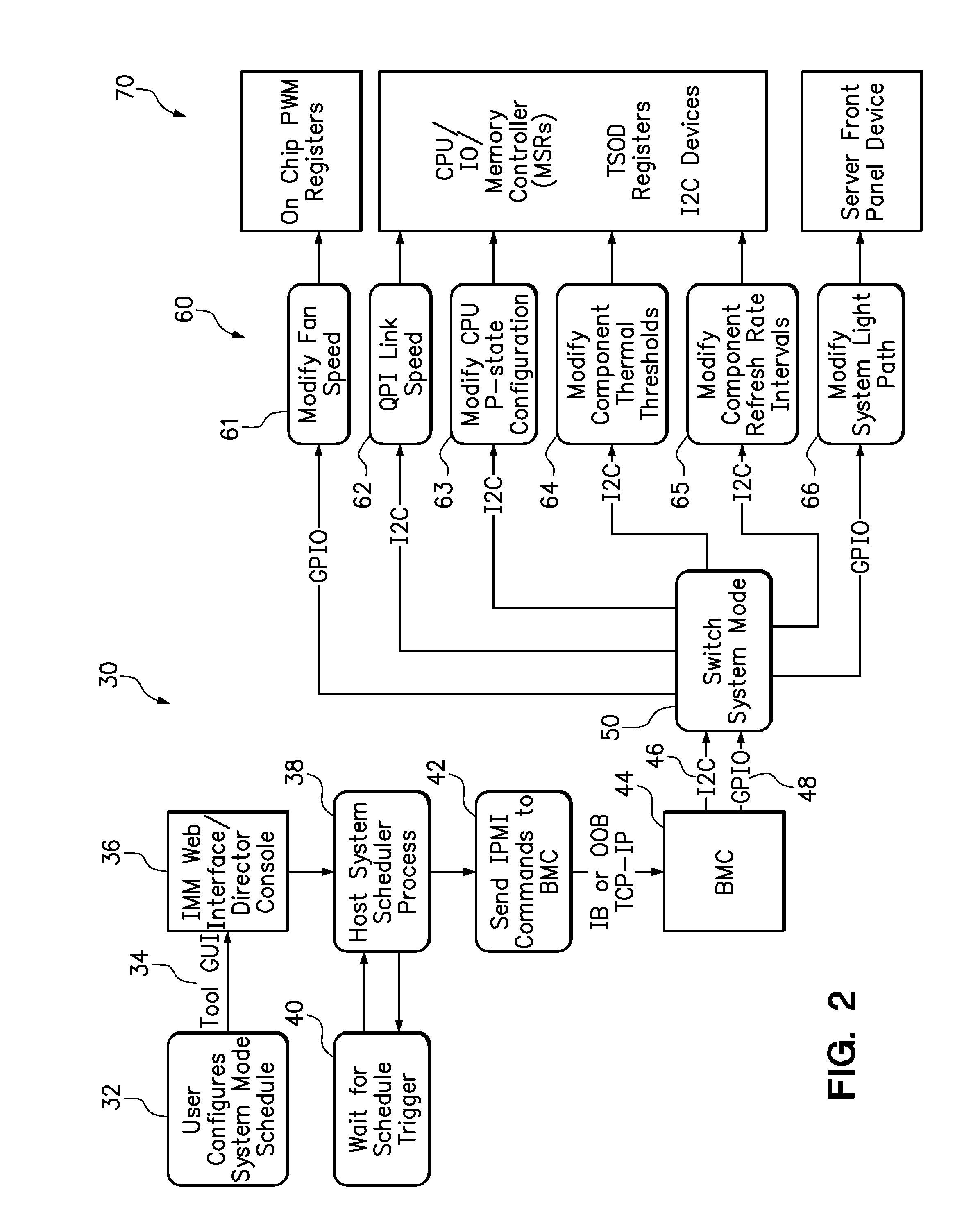

Dynamic system mode switching

InactiveUS20120017074A1Resource allocationData resettingOperational systemIntelligent Platform Management Interface

A system and method of controlling the system mode of a computer. The method comprises sending an Intelligent Platform Management Interface (IPMI) command to a baseboard management controller (BMC), wherein the IPMI command provides a system mode instruction to the BMC. The BMC then sends an operating parameter instruction to a plurality of hardware devices within the computer in response to receiving the IPMI command, wherein the operating parameter instruction sent to the plurality of hardware devices is associated with the system mode. Accordingly, each of the hardware devices operates according to the operating parameter instruction received from the BMC. Preferably, such a method allows the system mode to be changed without shutting down an operating system or rebooting the computer system. Optionally, the BMC may communicate with the hardware devices over an Inter Integrated Circuit (I2C) bus, a General Purpose Input Output (GPIO) pin of the BMC, or a combination thereof.

Owner:IBM CORP

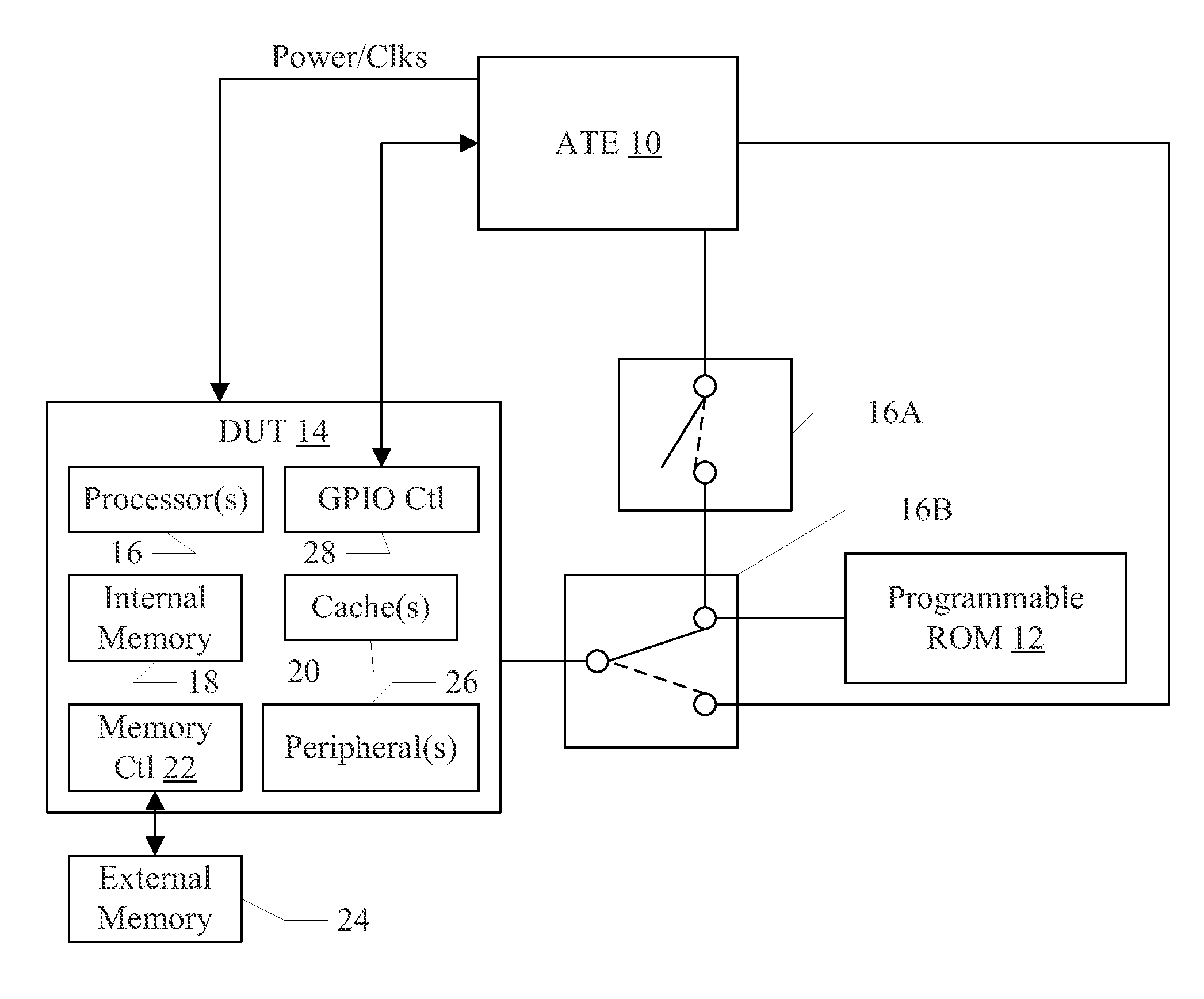

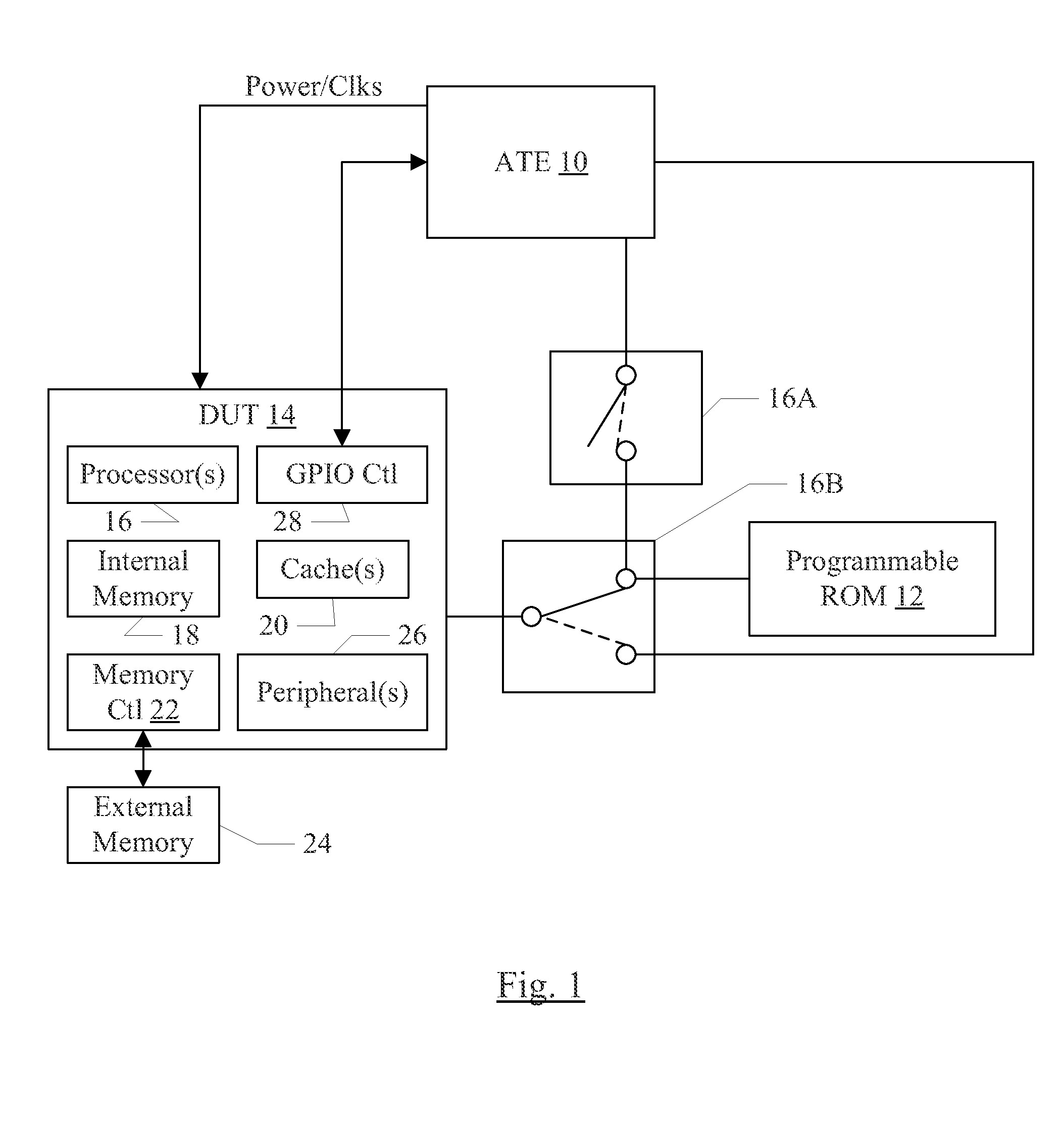

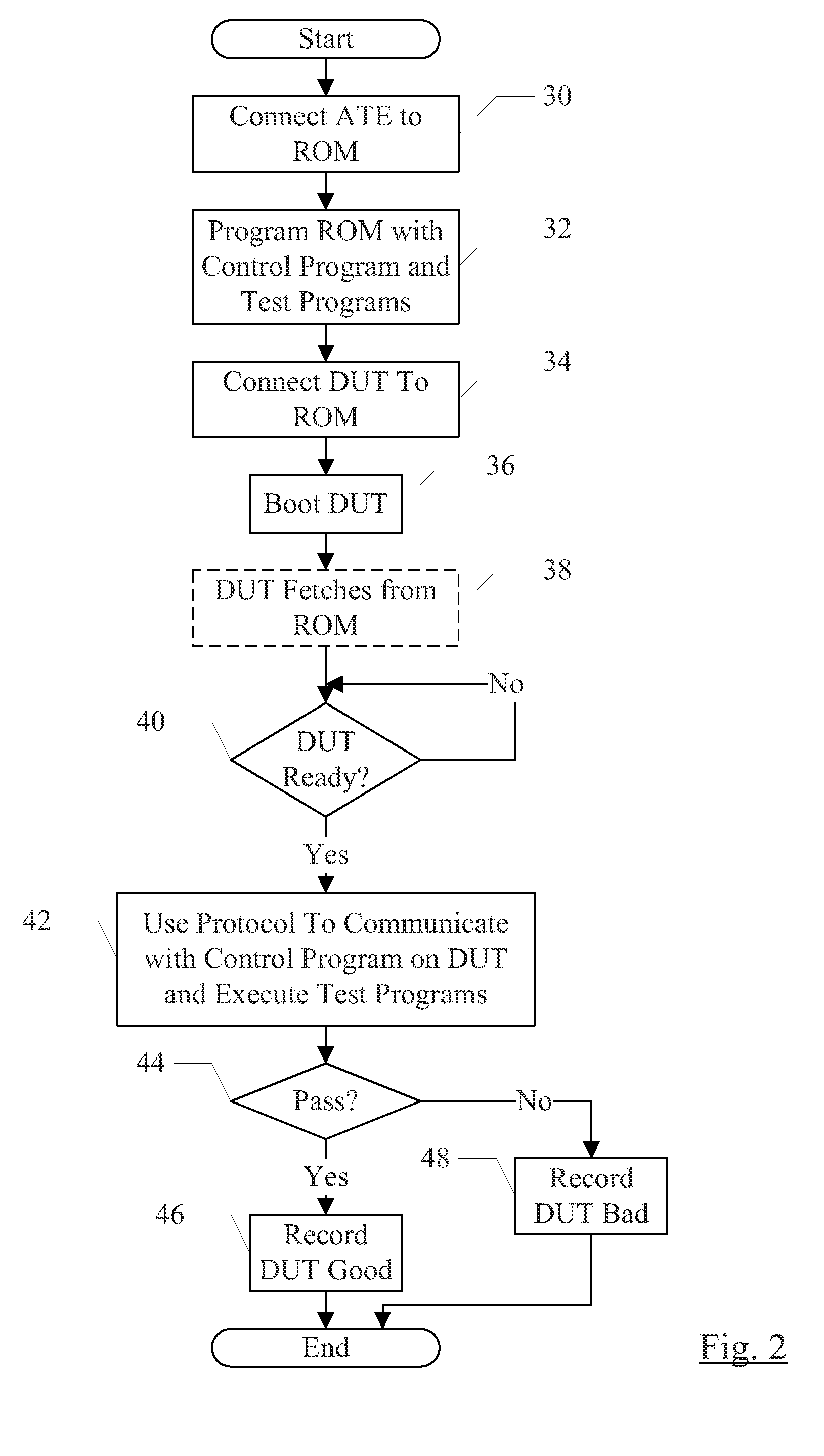

Test Method Using Memory Programmed with Tests and Protocol To Communicate between Device Under Test and Tester

InactiveUS20100312517A1Test accurateEfficient testingResistance/reactance/impedenceSpecial data processing applicationsEquipment under testTest vector

In an embodiment, a test method is implemented to test an integrated circuit that includes at least one processor. The method may include programming a memory to which the integrated circuit is coupled during testing with one or more test programs. The integrated circuit may be booted, and the processor may execute the test programs from the memory. In one embodiment, the memory may also store a control program that may manage the execution of the tests. In an embodiment, the control program may also implement a protocol to communicate with the ATE to perform the testing. The protocol may be implemented over a set of general purpose input / output (I / O) pins, for example. Using the protocol and test vectors on the ATE, the tests may be selected and executed, and test results may be reported.

Owner:APPLE INC

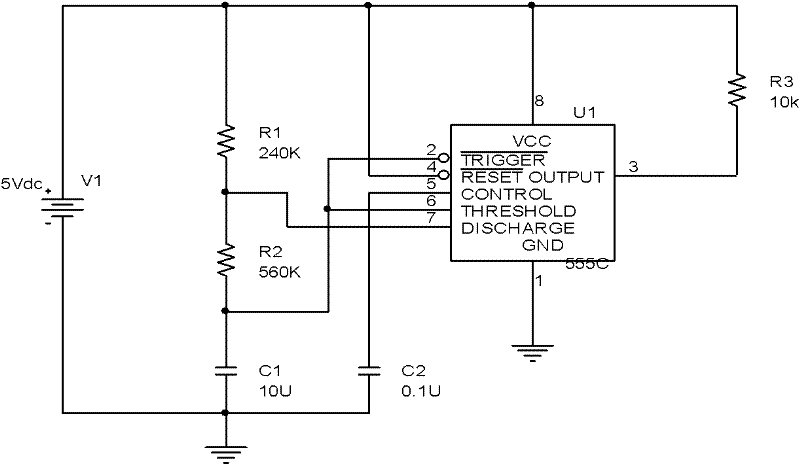

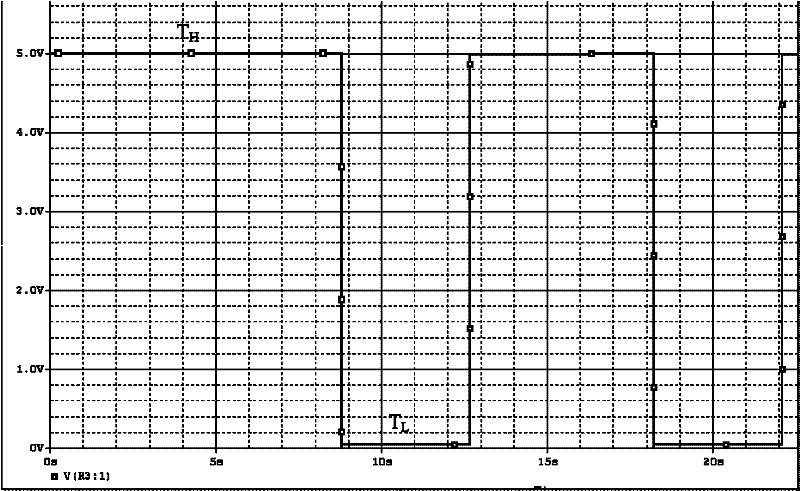

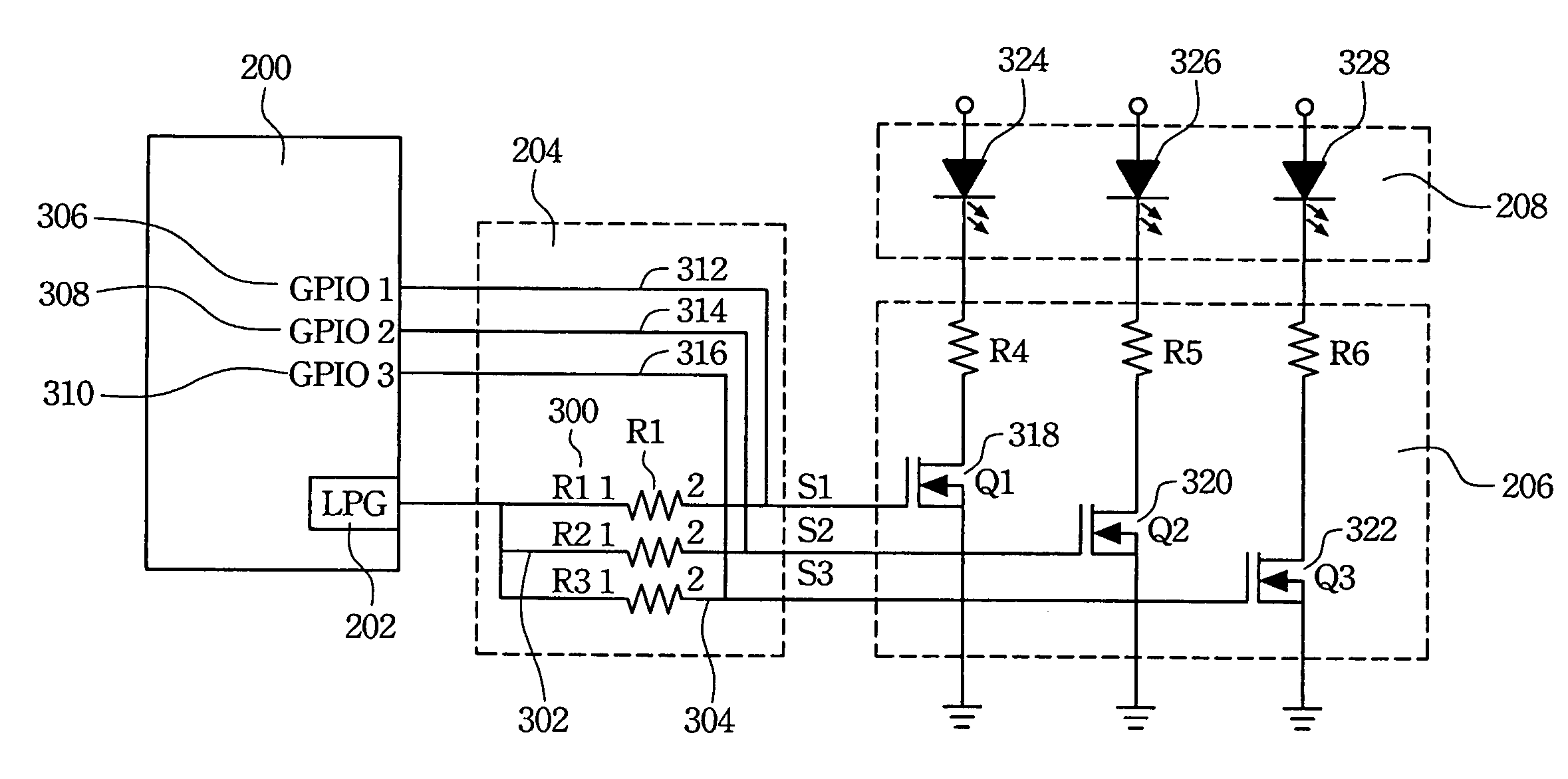

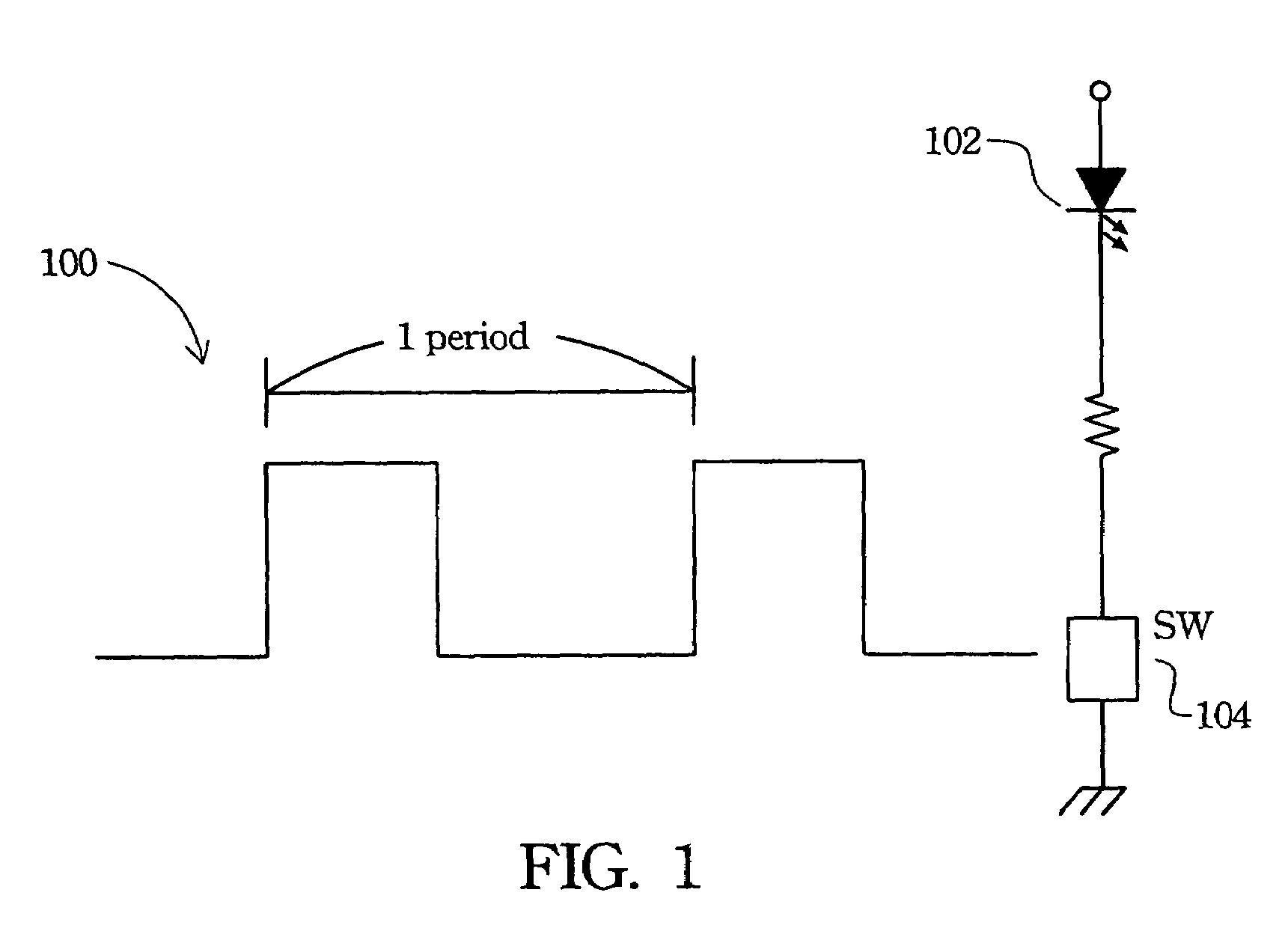

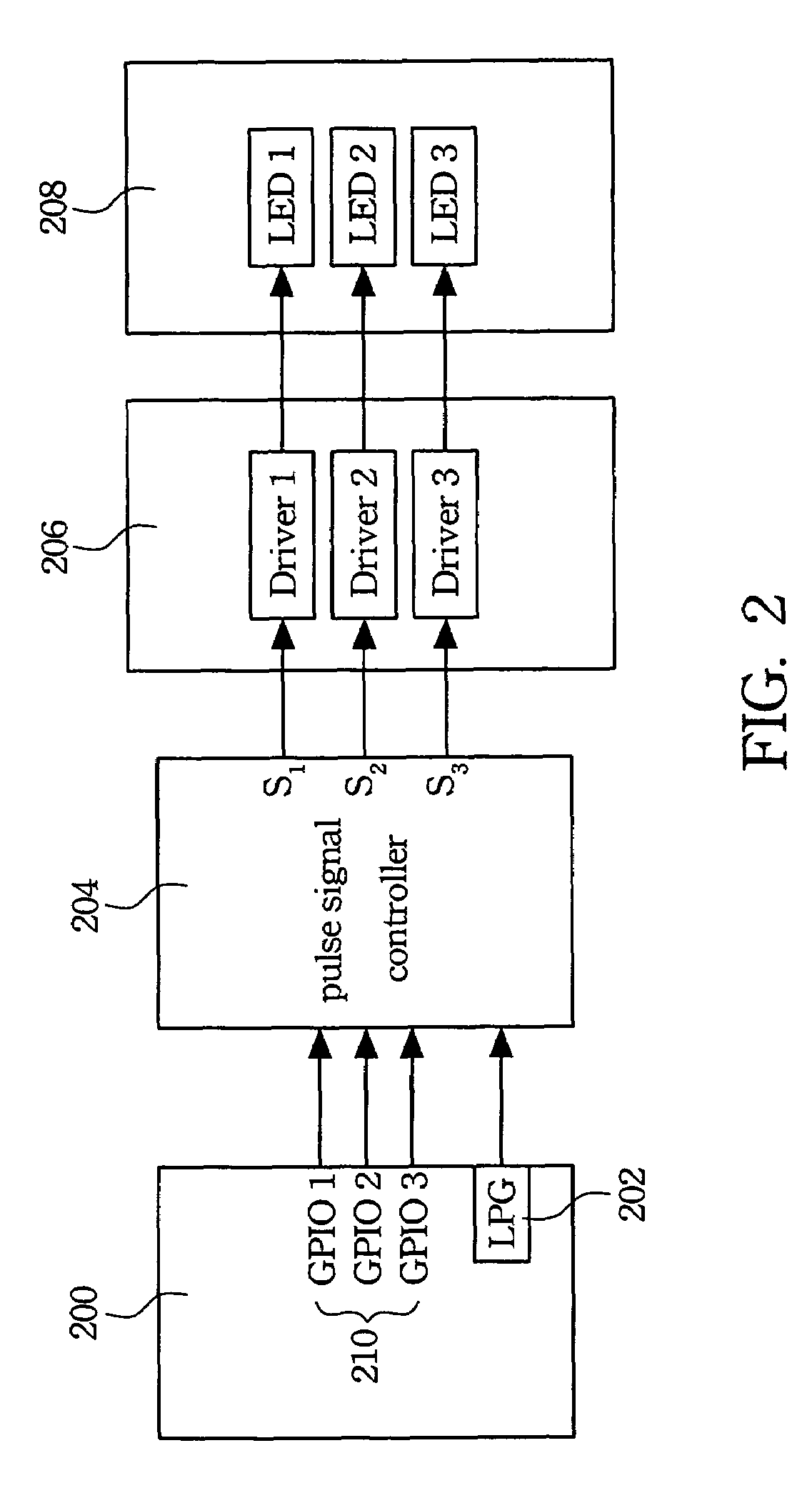

Flashing light control apparatus and method thereof

ActiveUS7129654B2Reduce power consumptionReduce volumeElectrical apparatusElectroluminescent light sourcesEngineeringSignal generator

The present invention describes a flashing light apparatus and method for operating the same. A pulse signal generated by a pulse signal generator and the states of the general purpose Input / Output pins of a CPU are used to control the lights to flash.

Owner:HTC CORP

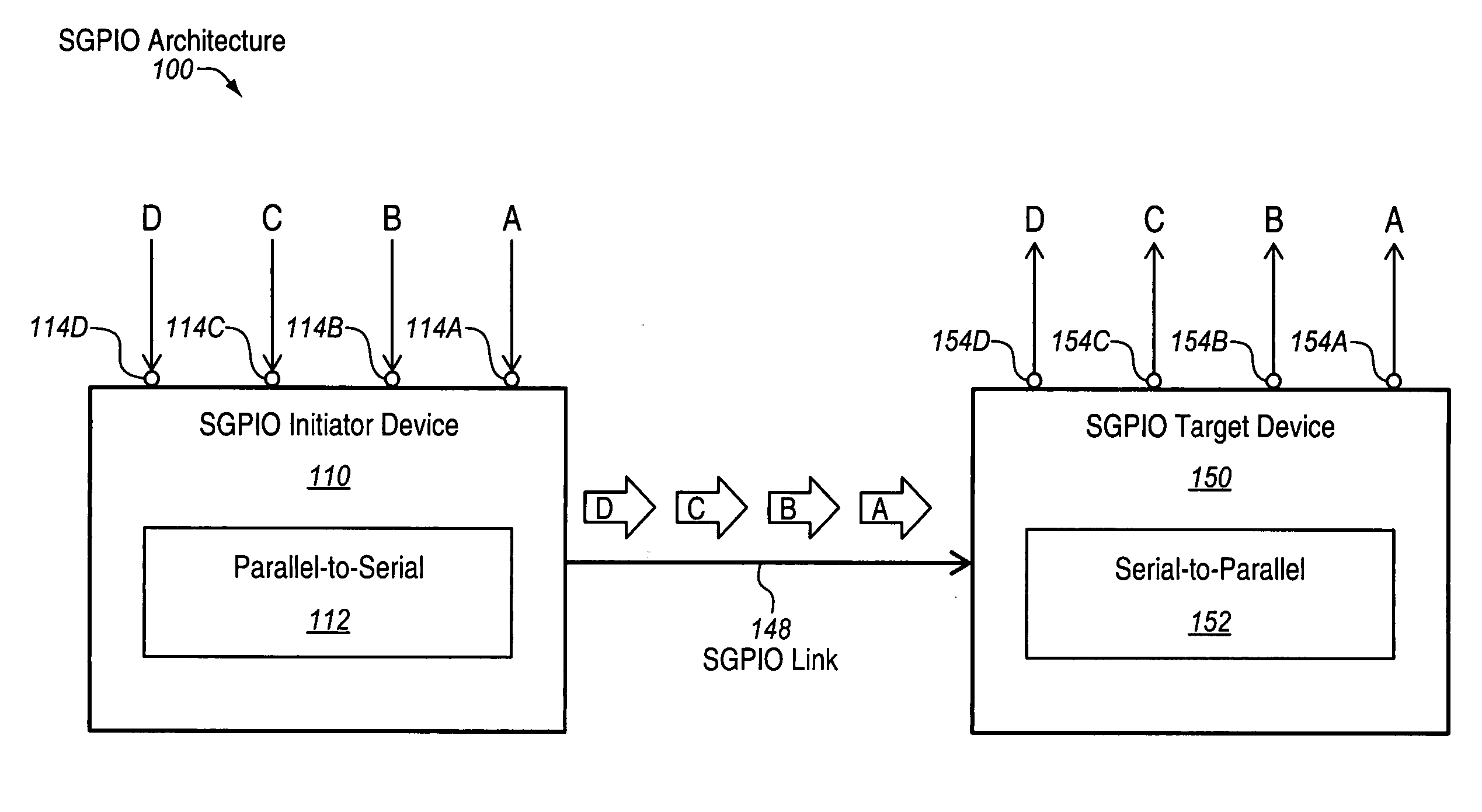

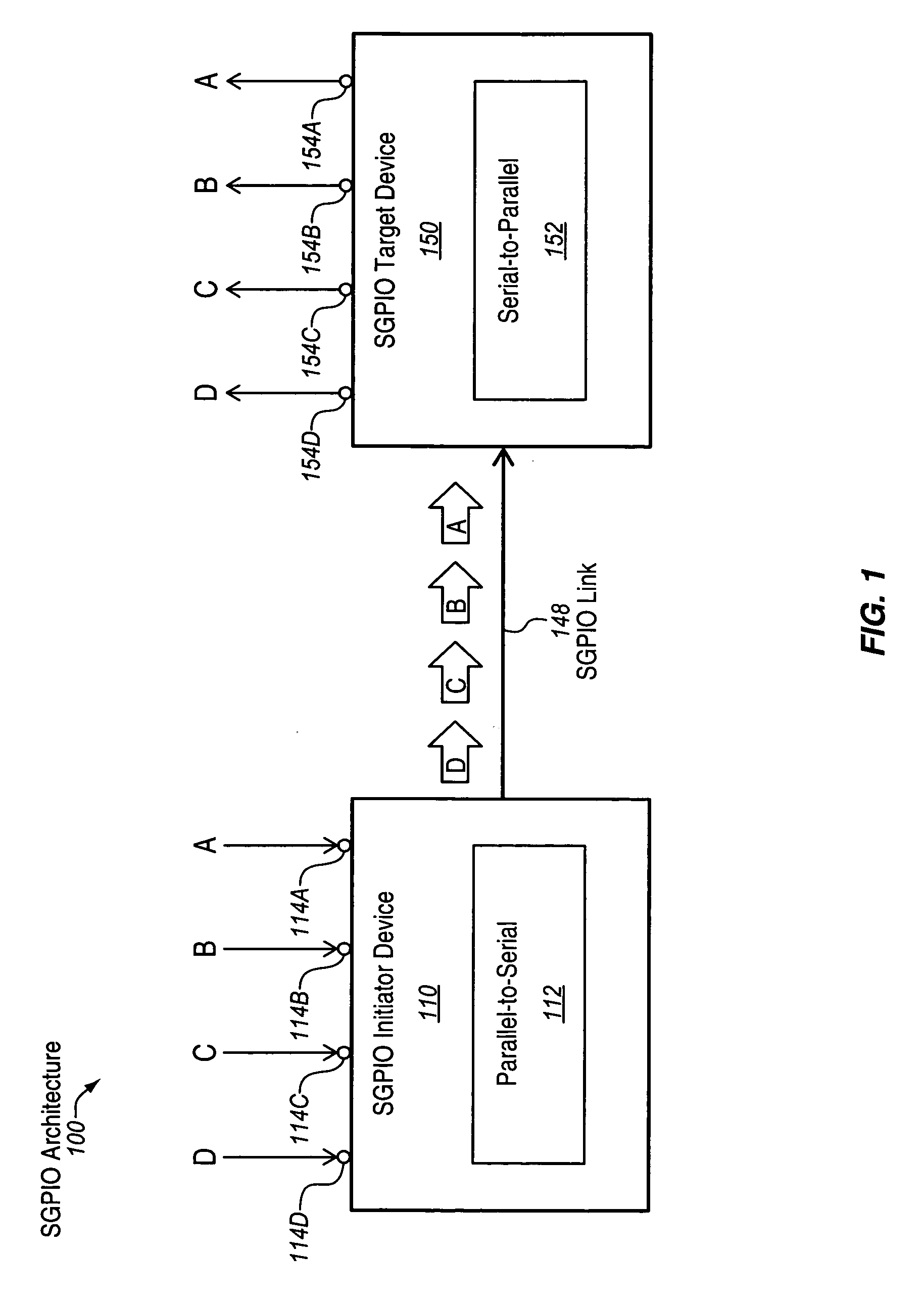

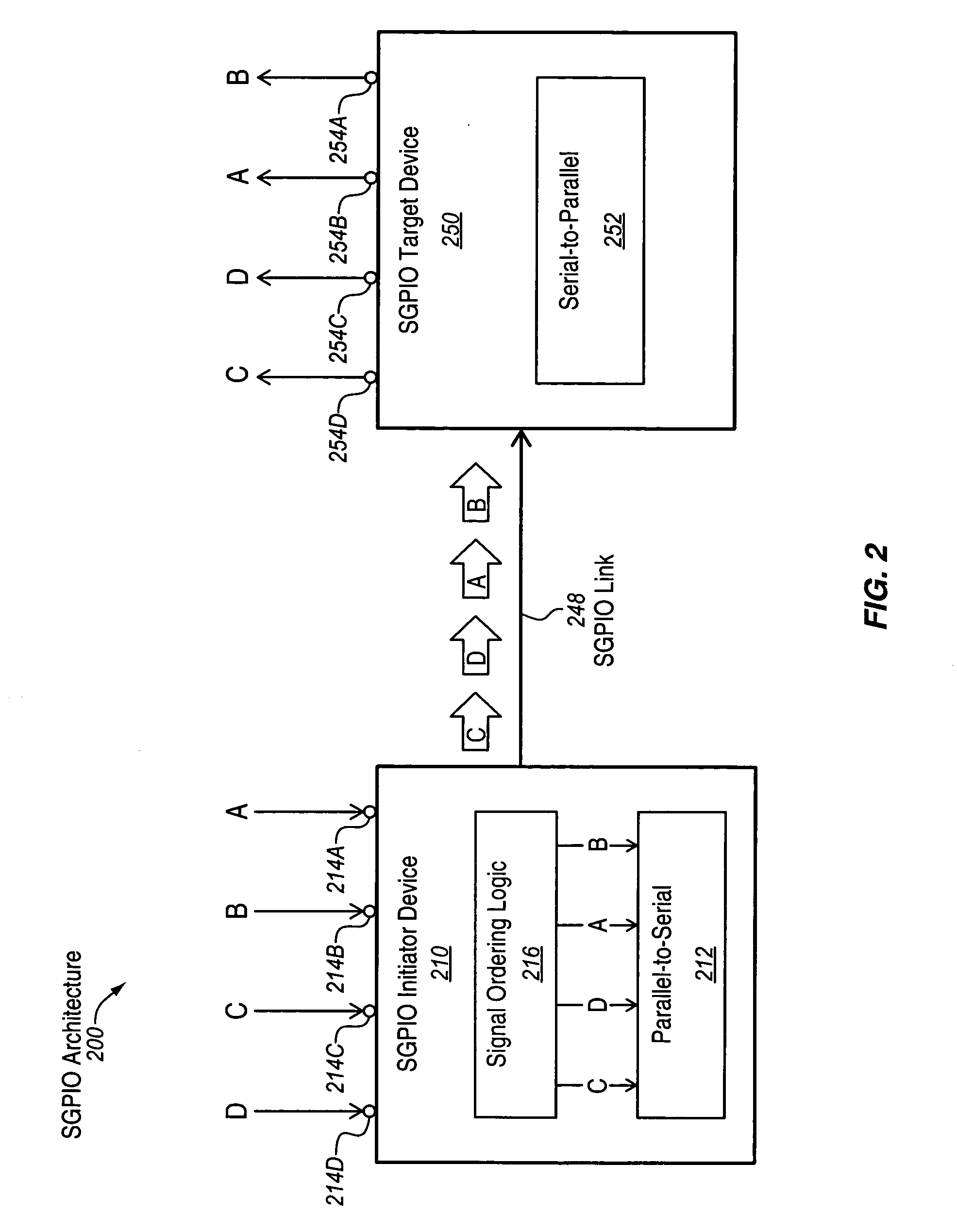

Serial signal ordering in serial general purpose input output (SGPIO)

An apparatus may include a Serial General Purpose Input Output (SGPIO) initiator device. The SGPIO initiator device may have terminals to receive parallel input signals. The device may also have parallel-to-serial conversion logic to convert the parallel input signals to a serial stream. The device may further have signal ordering logic. The signal ordering logic may be in communication with the terminals and may be in communication with the parallel-to-serial conversion logic. The signal ordering logic may determine an order in which the parallel input signals are provided in the serial stream. Methods of ordering signals within an SGPIO initiator device and systems having SGPIO initiator devices are also disclosed.

Owner:INTEL CORP

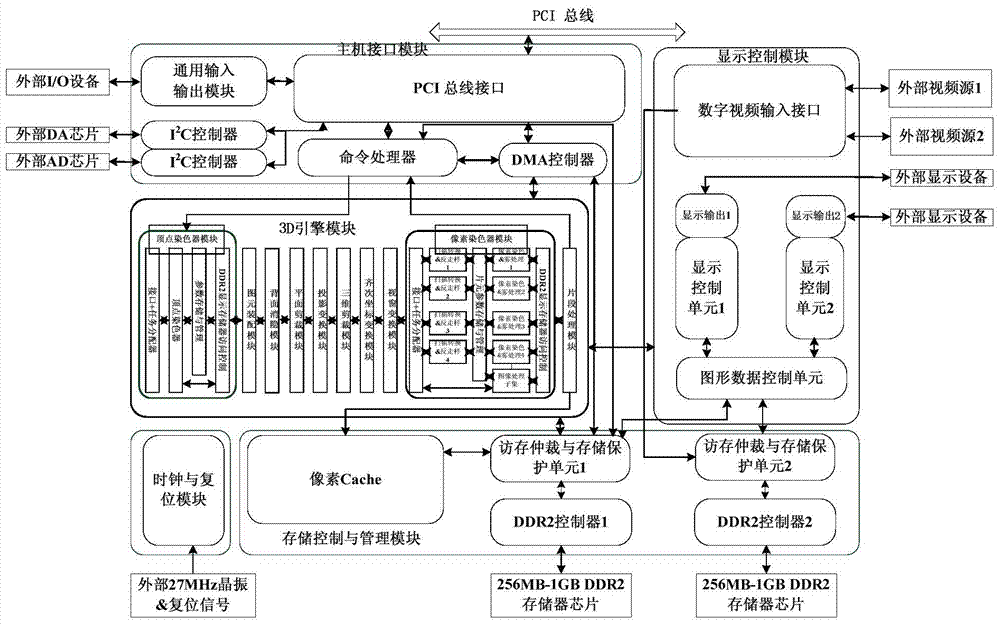

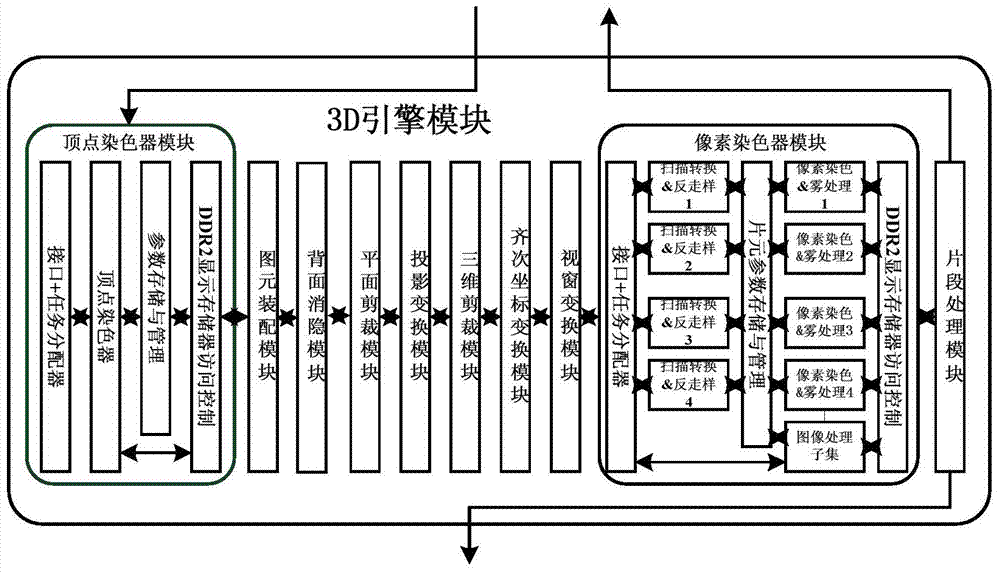

OpenGL (open graphic library) API (application program interface)-oriented graphic processor

ActiveCN104503950AProgrammableRapid build capabilityArchitecture with single central processing unitElectric digital data processingGraphicsManagement unit

The invention relates to an OpenGL (open graphic library) API (application program interface)-oriented graphic processor, and belongs to a multifunctional general small-sized GPU (graphic processing unit) chip. A hardware 3D (three-dimensional) acceleration engine is integrated at the inside, the compatibility with an OpenGL 3D graphic processing API is realized, and the acceleration processing capability for building 3D graphics is provided. A 3D graphic acceleration processing-oriented storage sub system is realized on the chip, and comprises a pixel cache, a storage control and management unit and a high-speed two-channel DDR2 controller. In addition, the GPU is integrated with a display control module, and comprises a VIP (video input module) for providing a video source to realize a superposition function, and two paths of independent display controllers for providing digital display output interfaces. An I<2>C bus interface, a GPIO (general purpose input output) unit and a bus interface module conforming to PCI2.2 standards are also integrated in the GPU, and the graphic acceleration processing function can be provided for a computer system providing a PCI (peripheral component interconnect) host interface.

Owner:AVIC NO 631 RES INST

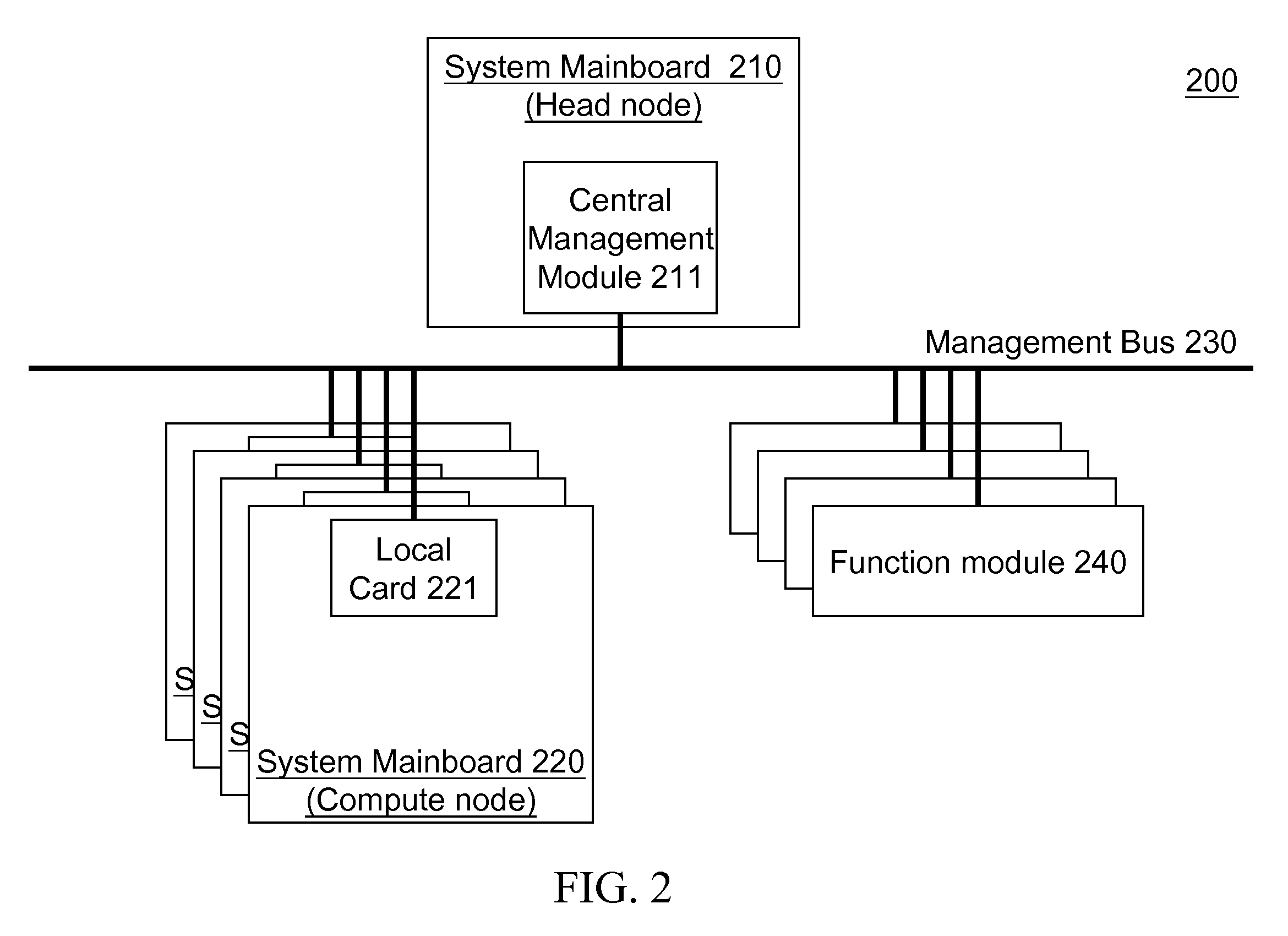

Alternative Local Card, Central Management Module and System Management Architecture For Multi-Mainboard System

InactiveUS20080126597A1Increase implementation flexibilityLow costInput/output processes for data processingMonitoring statusBaseboard

A system management architecture is provided to monitor and control a multi-mainboard system with plural system mainboards. The system management architecture includes a local card for alternatively replacing a BMC (Baseboard Management Controller)-based management card on the system mainboard. The local card mainly includes a GPIO (General Purpose Input / Output) device and a basic logic. A central management module is also used in the system management architecture to monitor and control the system mainboard through a management bus and the management or local card. The local card monitors status signals on the system mainboard according to the command signals from the central management module, and additionally, provides customized monitoring capability. Accordingly, the local card facilitates the implementation flexibility for the system management architecture and reduces the cost and maintenance supports required by numerous BMC-based management cards.

Owner:MITAC INT CORP

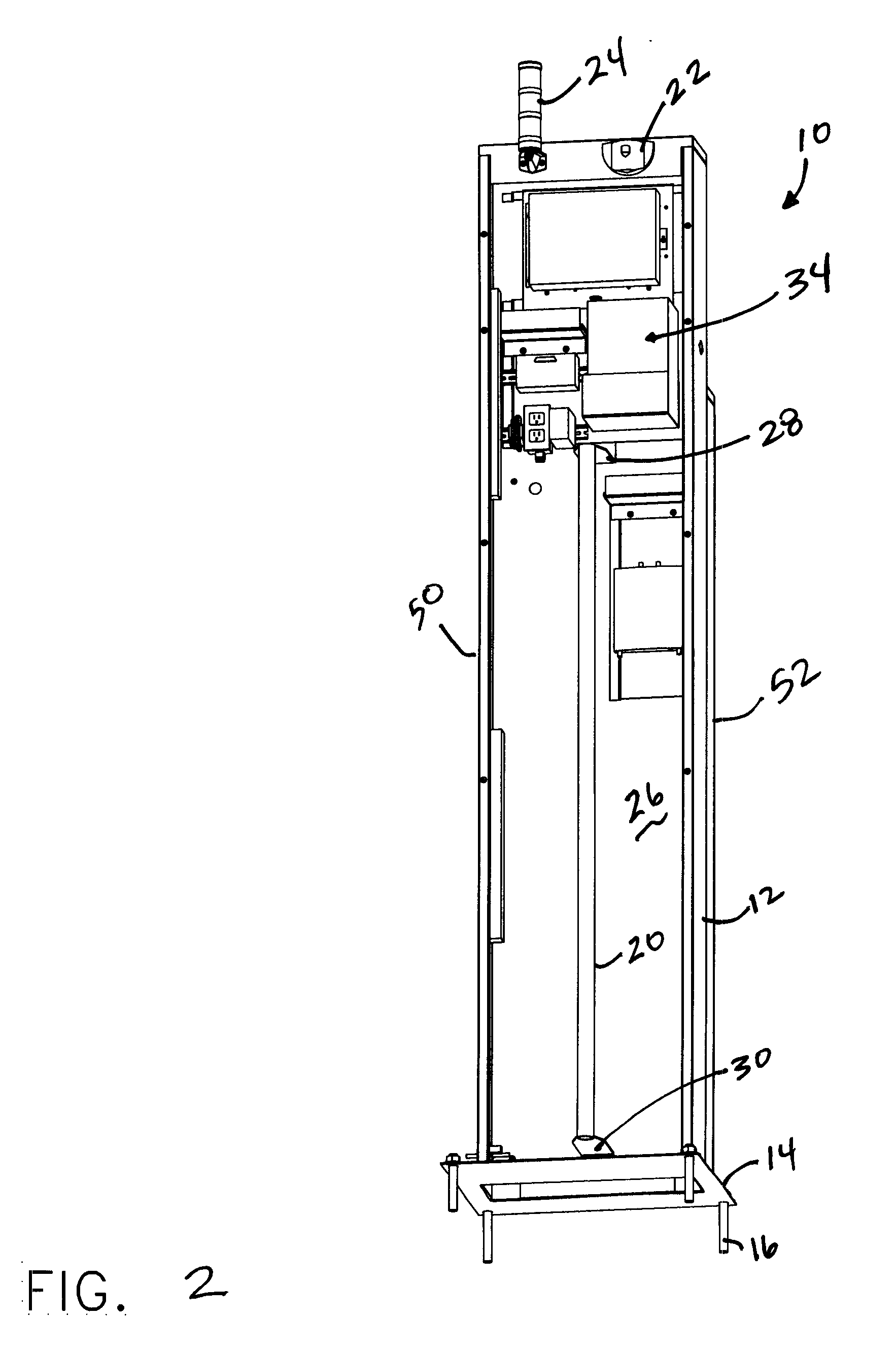

Radio frequency identification (RFID) portal antenna mounting frame

InactiveUS20070252701A1Easy to engageAvoid accidental damageAntenna supports/mountingsRadiating element housingsMotion detectorEngineering

A radio frequency identification (RFID) portal easily installs and integrates any RFID hardware / software systems. The RFID portal may match the size of a traditional dock or be custom sized. The portal takes advantage of a variety of unique features including an antenna bracket that provides for three-dimensional vertical and horizontal movements and a hardware independent reader bracket. The antenna movement capabilities allow for excellent RFID signal coverage. A General Purpose Input / Output (GPIO) bridge enables rapid integration and functionality to other RFID inputs such as Motion Detectors / Photo Eyes, Uninterrupted Power Supply (UPS), Wireless Networking, floor loops, mass detectors, and output signals, such as to light stacks and RFID readers.

Owner:JAMISON DOOR

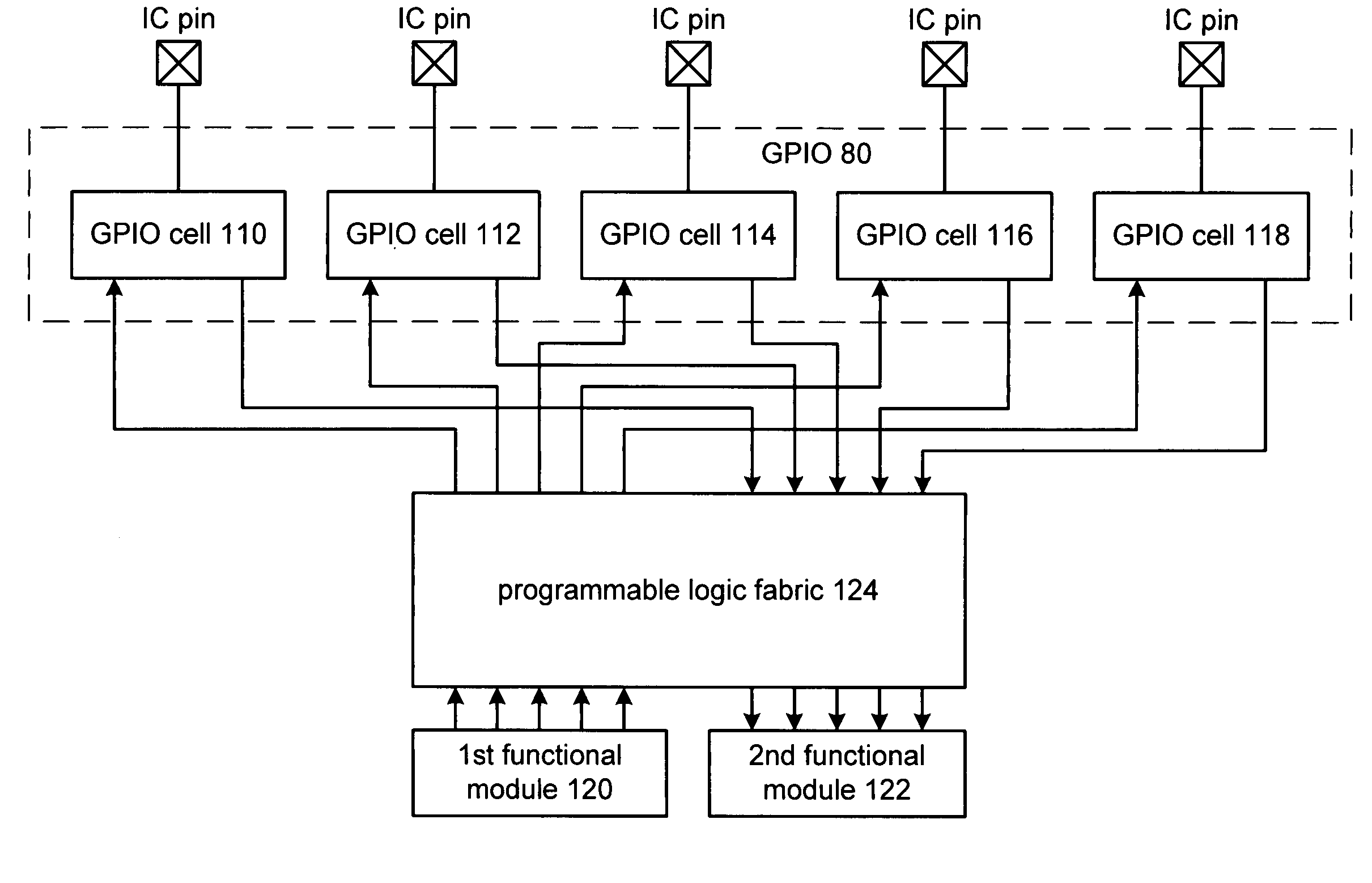

Configurable integrated circuit for use in a multi-function handheld device

A configurable integrated circuit includes at least one general purpose input / output (GPIO) interface module, a first functional module, and a second functional module. The GPIO interface module includes a plurality of GPIO cells, wherein each of the GPIO cells is operably coupled to a corresponding pin of the configurable integrated circuit. When the configurable integrated circuit is in a first functional mode, at least one of the GPIO cells is operably coupled to its corresponding pin such that the corresponding pin functions as a digital input pin for the first functional module. When the configurable integrated circuit is in a second functional mode, at least one of the GPIO cells is operably coupled to its corresponding pin such that the corresponding pin functions as a digital output pin for the second functional module.

Owner:APPLE INC

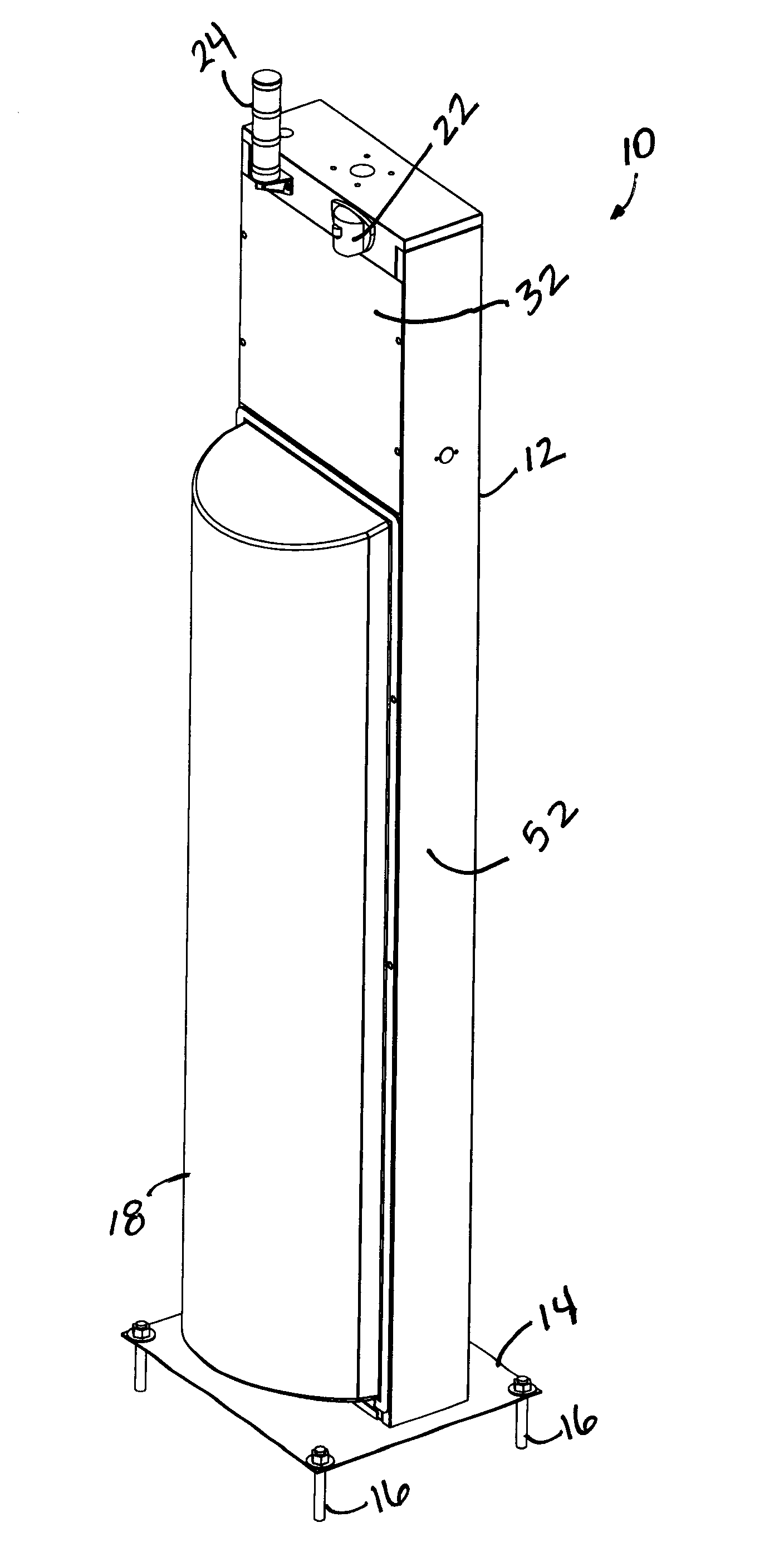

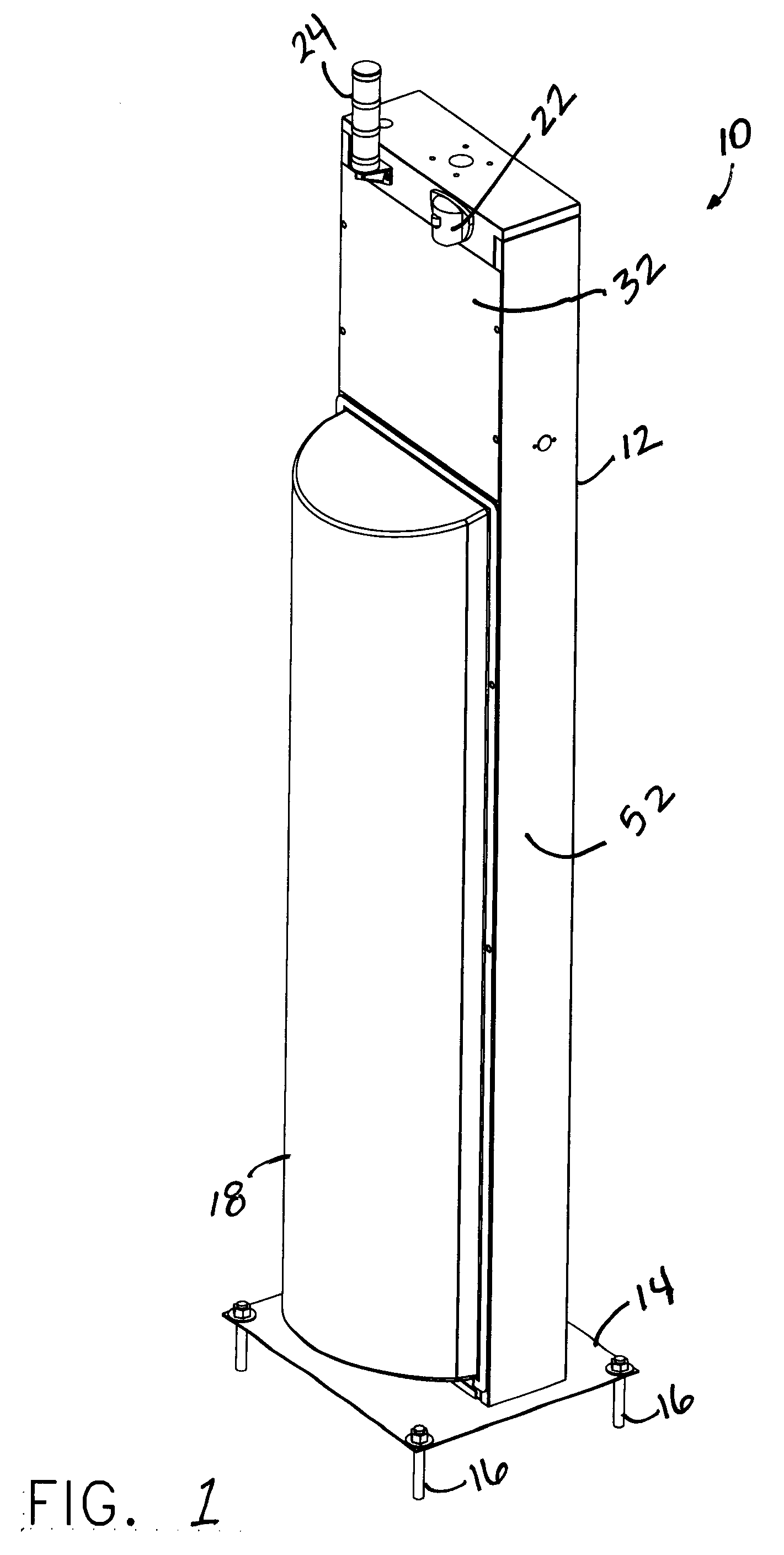

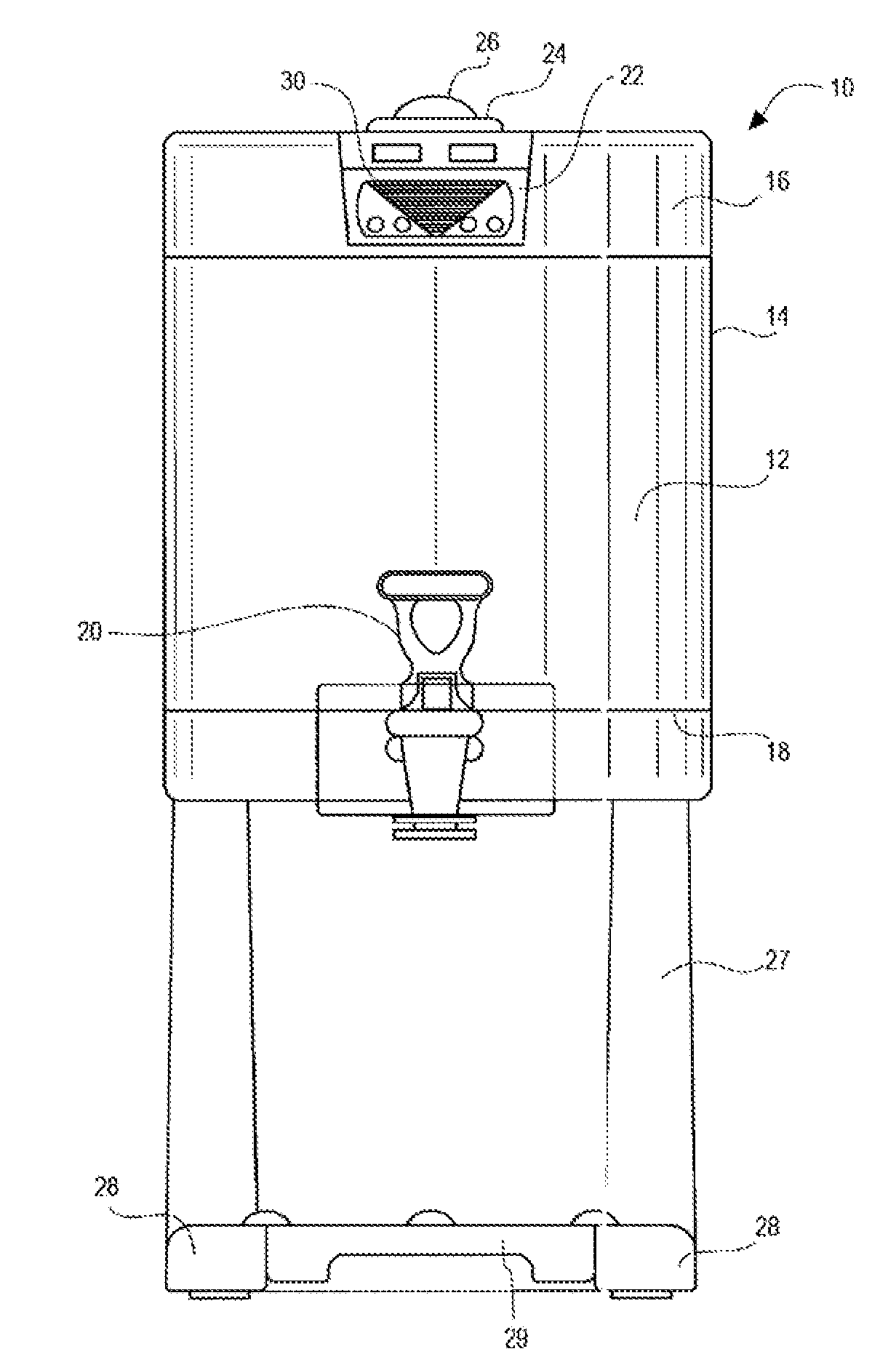

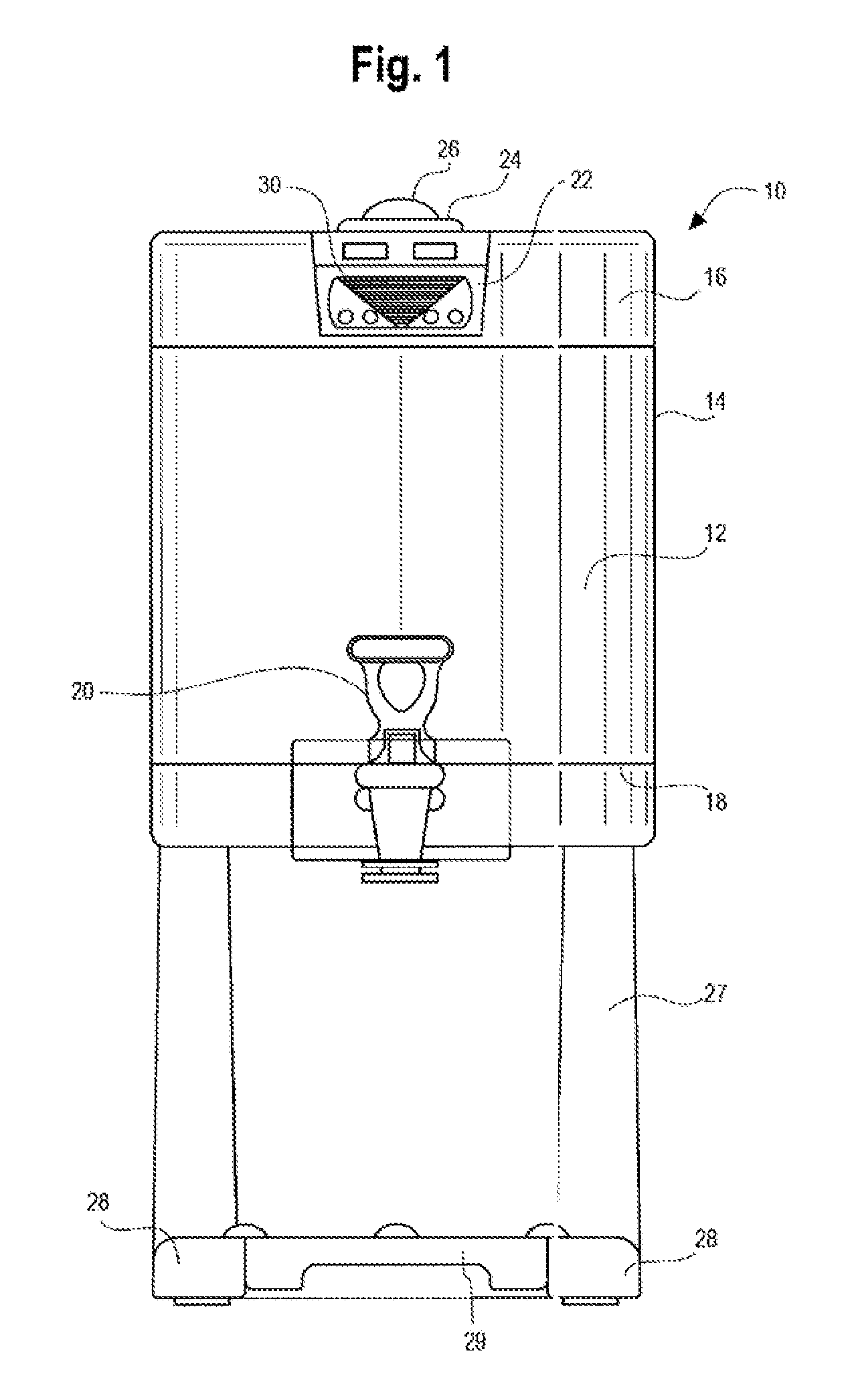

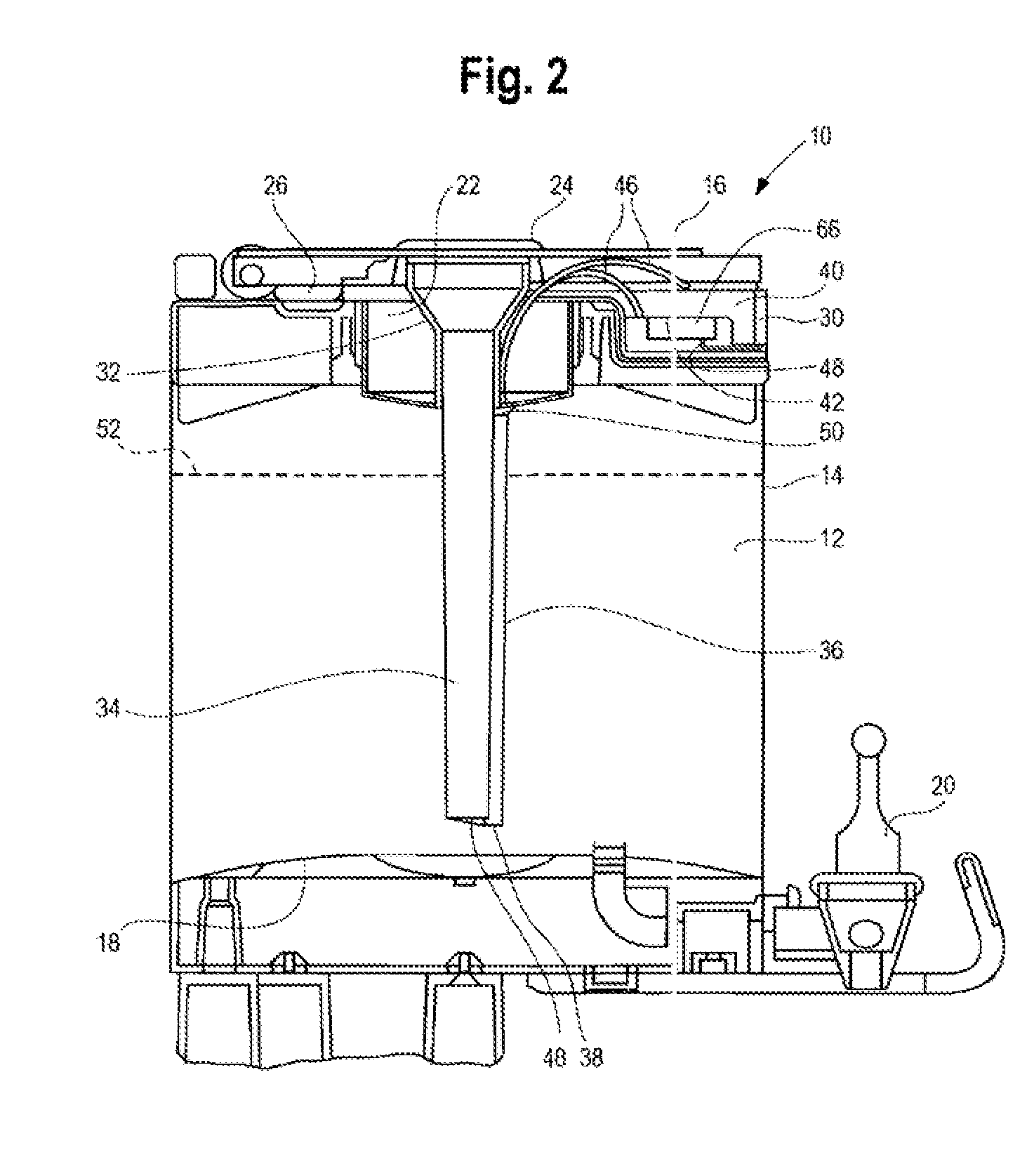

Beverage dispenser with capacitive level sensor and display and method

ActiveUS8387455B1Reduce power consumptionLow power stateMachines/enginesLubrication indication devicesCapacitanceGeneral purpose

A beverage dispenser (10) with a beverage quantity indicating display (30) controlled by a microprocessor (66) in response to variations in capacitance of a plurality of sensing capacitors (72) detected by a capacitive sensing circuit (70) including one of a general purpose input / output integrated capacitive touch-key sensor, and a general purpose, integrated, input / output port expander with an integrated capacitive touch-key for reduced power consumption, sensitivity and reliability. A reference capacitor (C8) is located above the maximum height (52) of the beverage (74) to keep it spaced from the beverage (74) in air is used to compensate for changes in capacitance of the sensing capacitors (72) due to variations in temperature. All the capacitors (72, C8) are formed from pairs of planer conductive plates (54, 56) respectively mounted to opposed parallel interior surfaces (58, 60) of a sensing tube (36) attached to a down tube (34).

Owner:FOOD EQUIP TECH

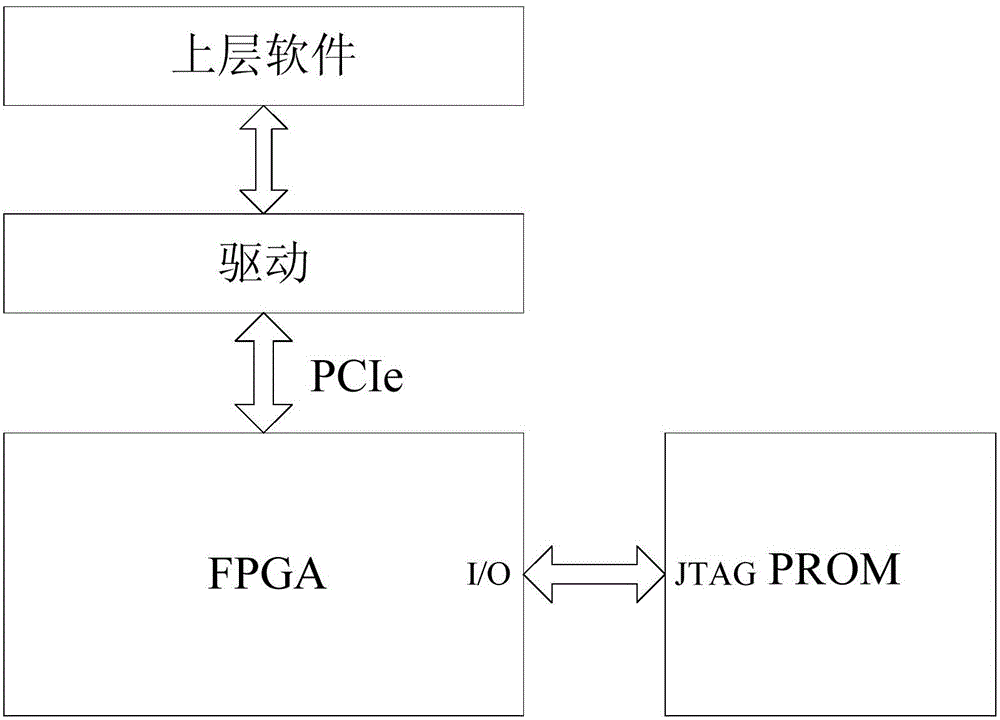

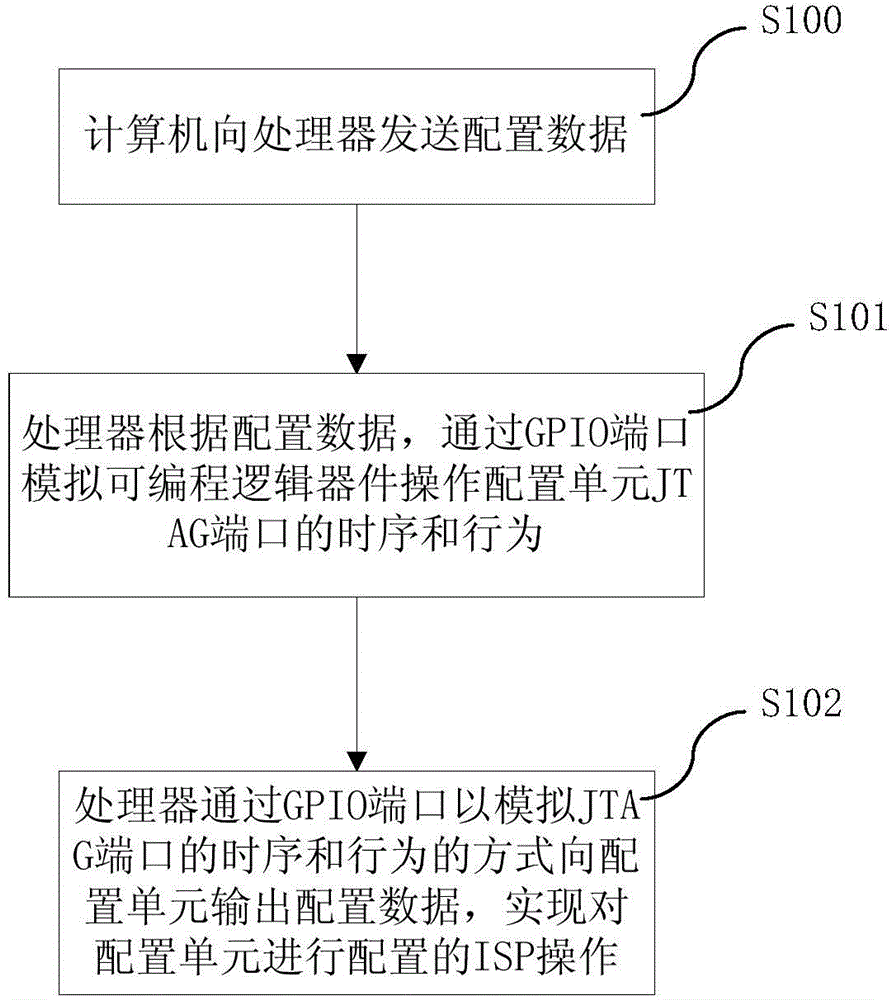

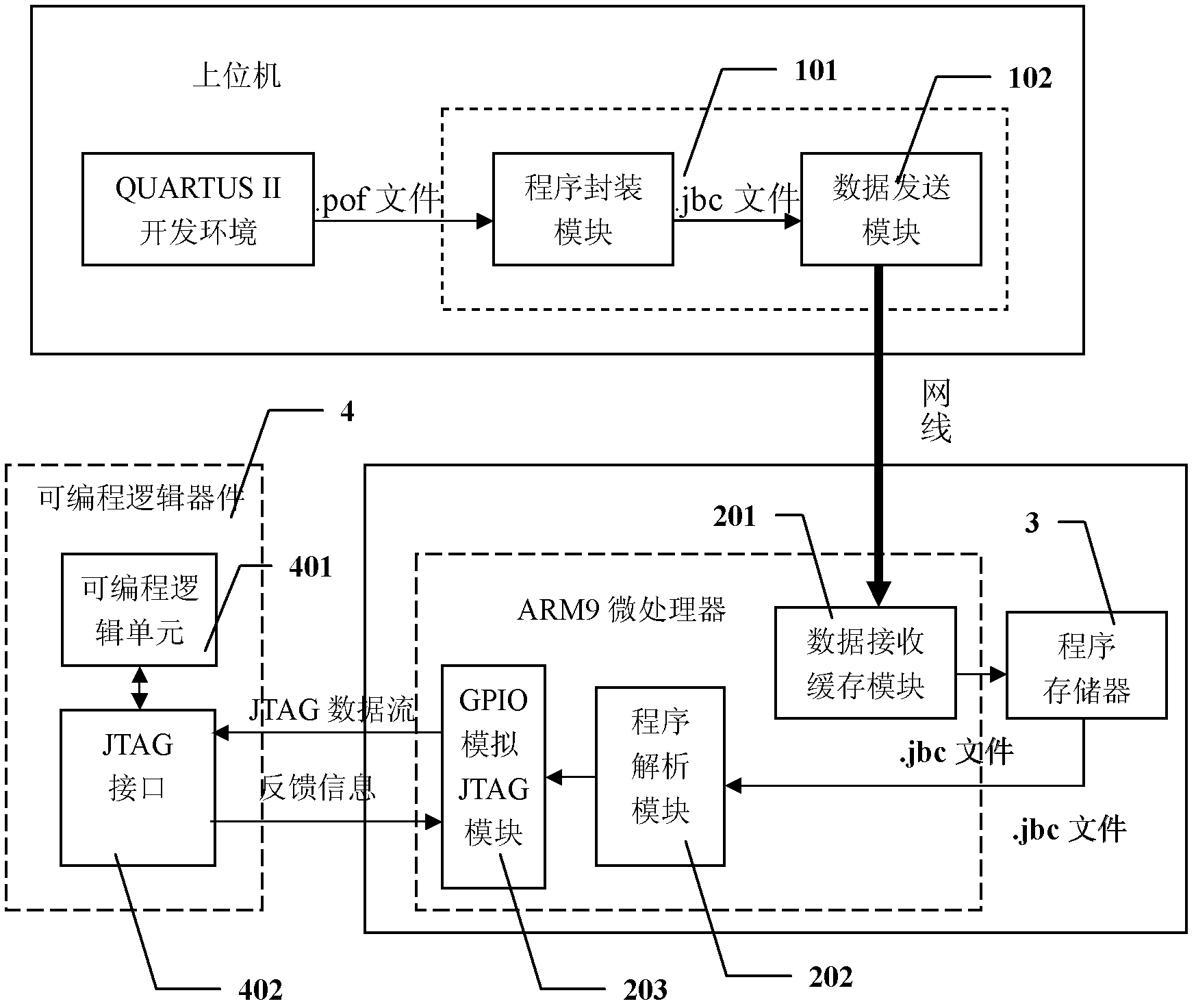

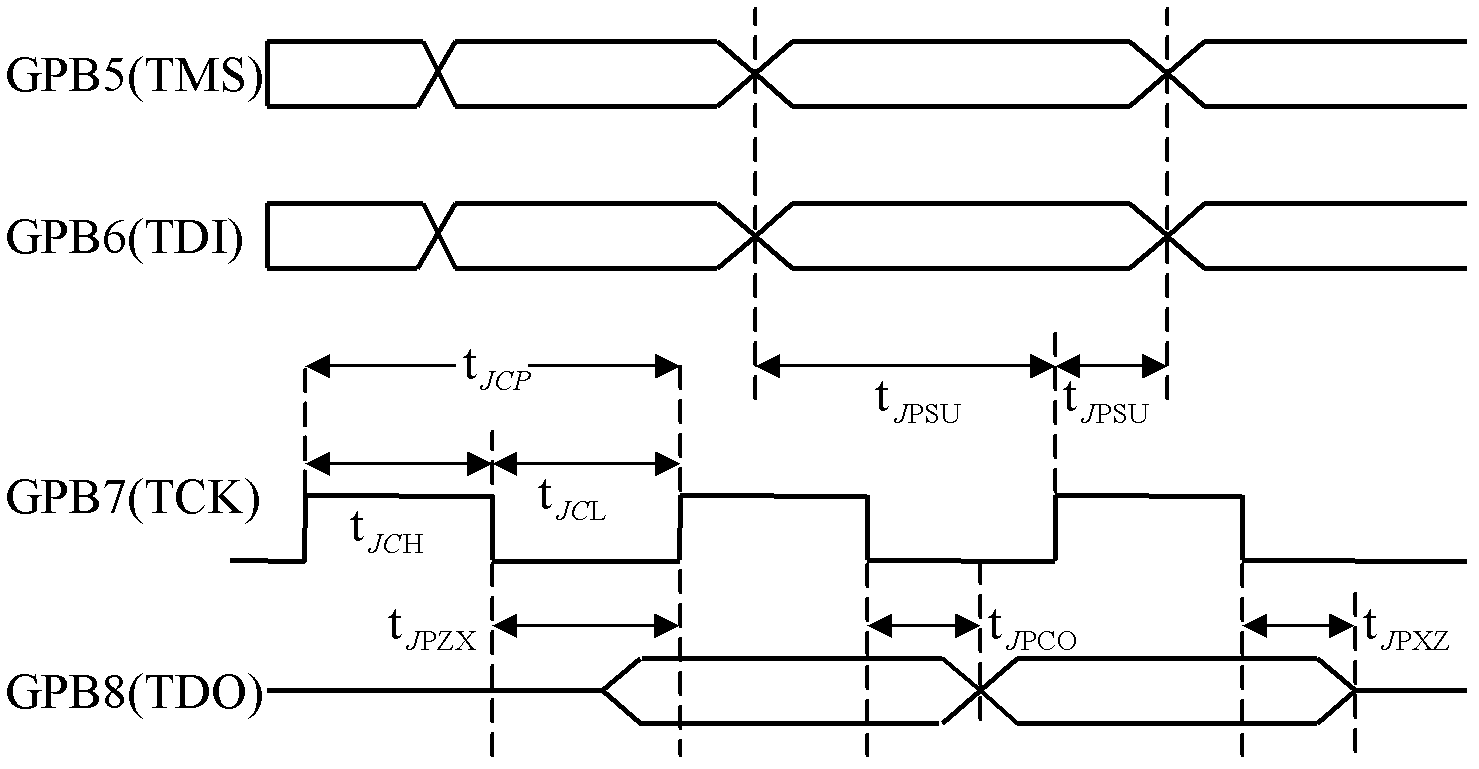

Remote update system and method for programmable logic device

ActiveCN105224345ASolve technical problems that cannot meet the requirementsSolve technical problems that are difficult to executeProgram loading/initiatingIn-system programmingConfidentiality

The invention discloses a remote update system and method for a programmable logic device. The system comprises a computer, a processor, a programmable logic device and a configuration unit, wherein the processor, the programmable logic device and the configuration unit are mutually connected; the computer sends configuration file data to the processor; and the processor simulates the programmable logic device to configure the time sequence and the behavior of a JTAG (Joint Test Action Group) port of the configuration unit through a GPIO (General Purpose Input / Output) port according to the configuration file data so as to realize an ISP (In System Programming) operation that the processor configures the configuration unit. The technical problem that a traditional dedicated simulator programming loading way cannot meet requirements since on-site logic programming is not suitable for workers under complex application conditions, especially under the environment with high confidentiality requirements, can be solved.

Owner:ZHUZHOU NAT ENG RES CENT OF CONVERTERS

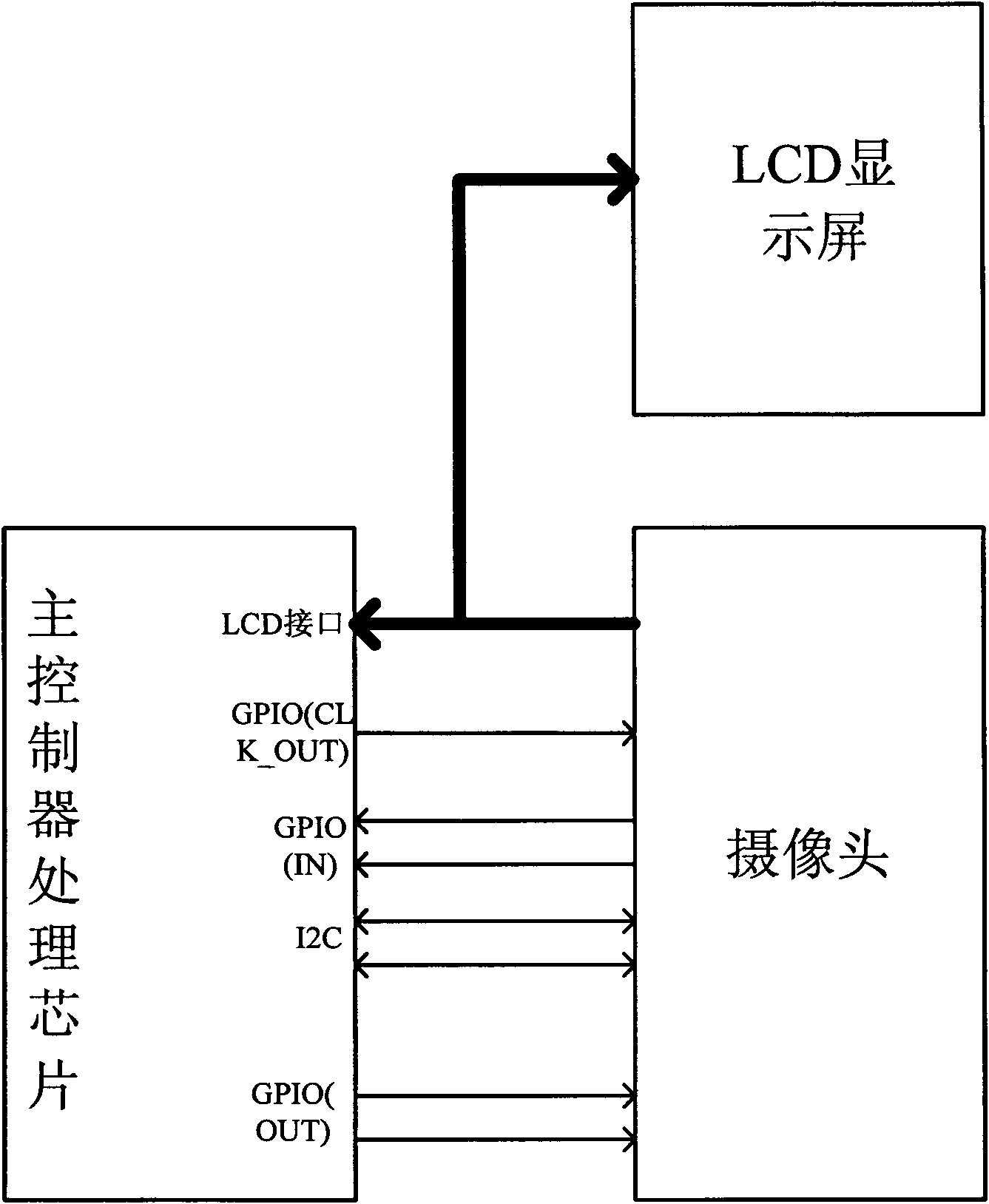

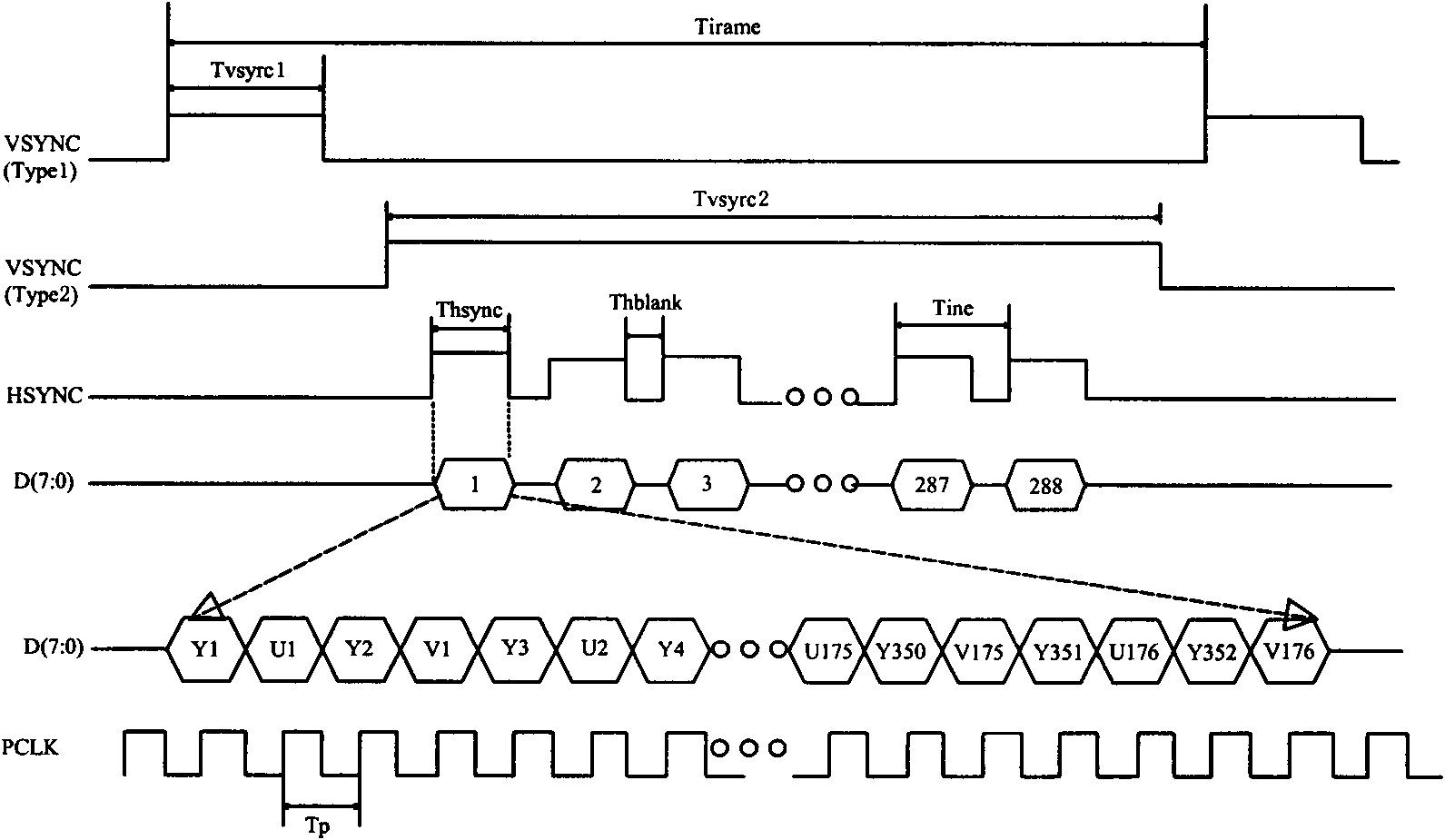

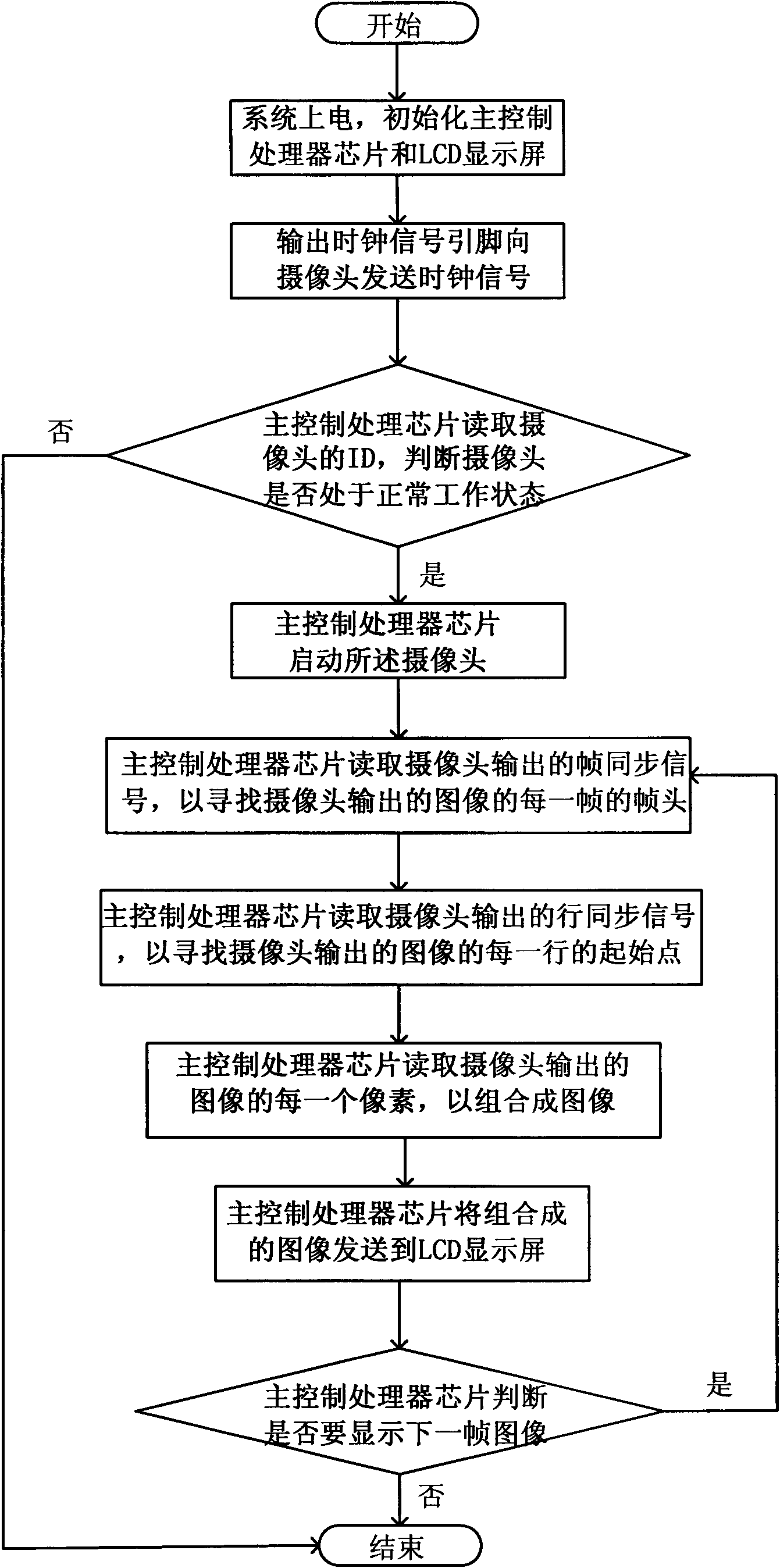

Camera system and method thereof

InactiveCN101674400AEnhanced camera functionLow costTelevision system detailsColor television detailsVideo recordBus interface

The invention relates to a camera system and a control method thereof. The system comprises a main control processor chip, an LCD display screen and a camera, wherein the LCD display screen and the camera are directly connected with an interface of the LCD display screen of the main control processor chip by a shared data line, and the camera is respectively connected with a clock signal output pin, a synchronous signal detection pin, a general-purpose input / output pin and an I2C bus interface. The camera system and the control method thereof are implemented by adding the camera and video record functions of a product with the camera system, such as a cellphone, a digital camera, and the like with the minimum cost by omitting a special control processor used for the camera. In addition, the invention adopts the technology as follows: multiplexing pins with the general-purpose input / output and clock output functions are adopted to simulate a clock signal and control the operation of thecamera so that the camera and the main control processor chip can synchronously work and image information output by the camera can be read by a data bus of the main control processor chip.

Owner:深圳市经纬科技有限公司

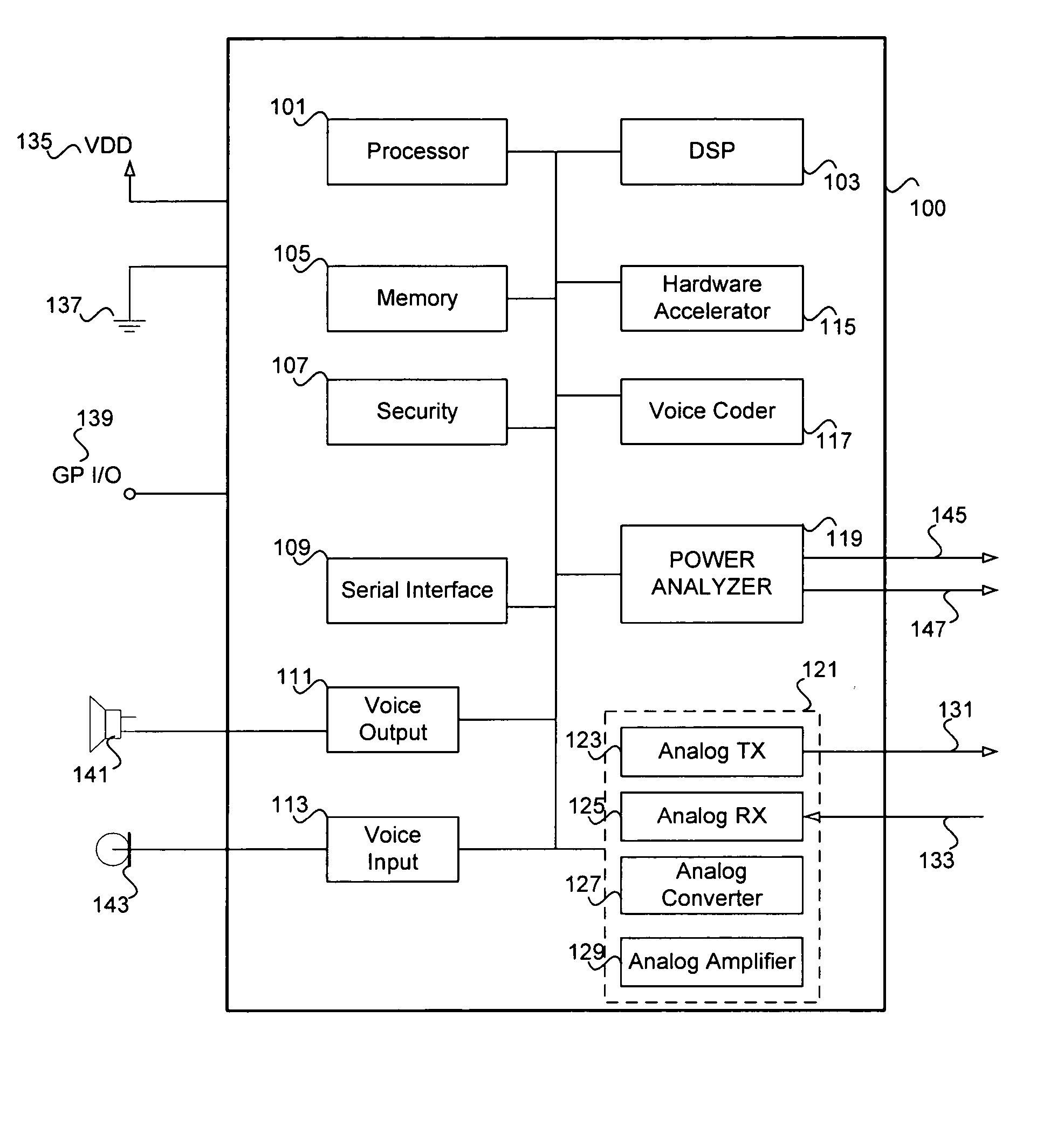

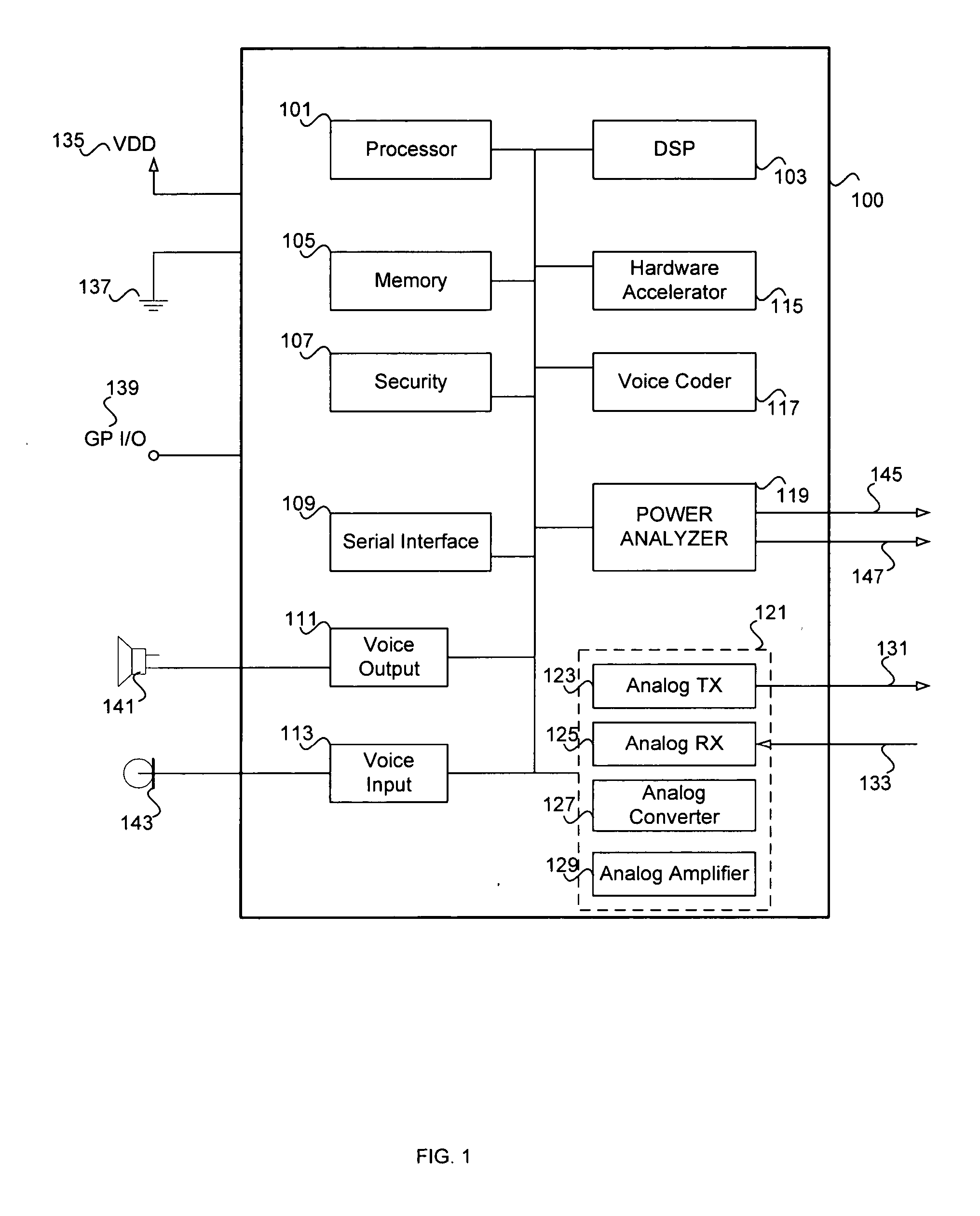

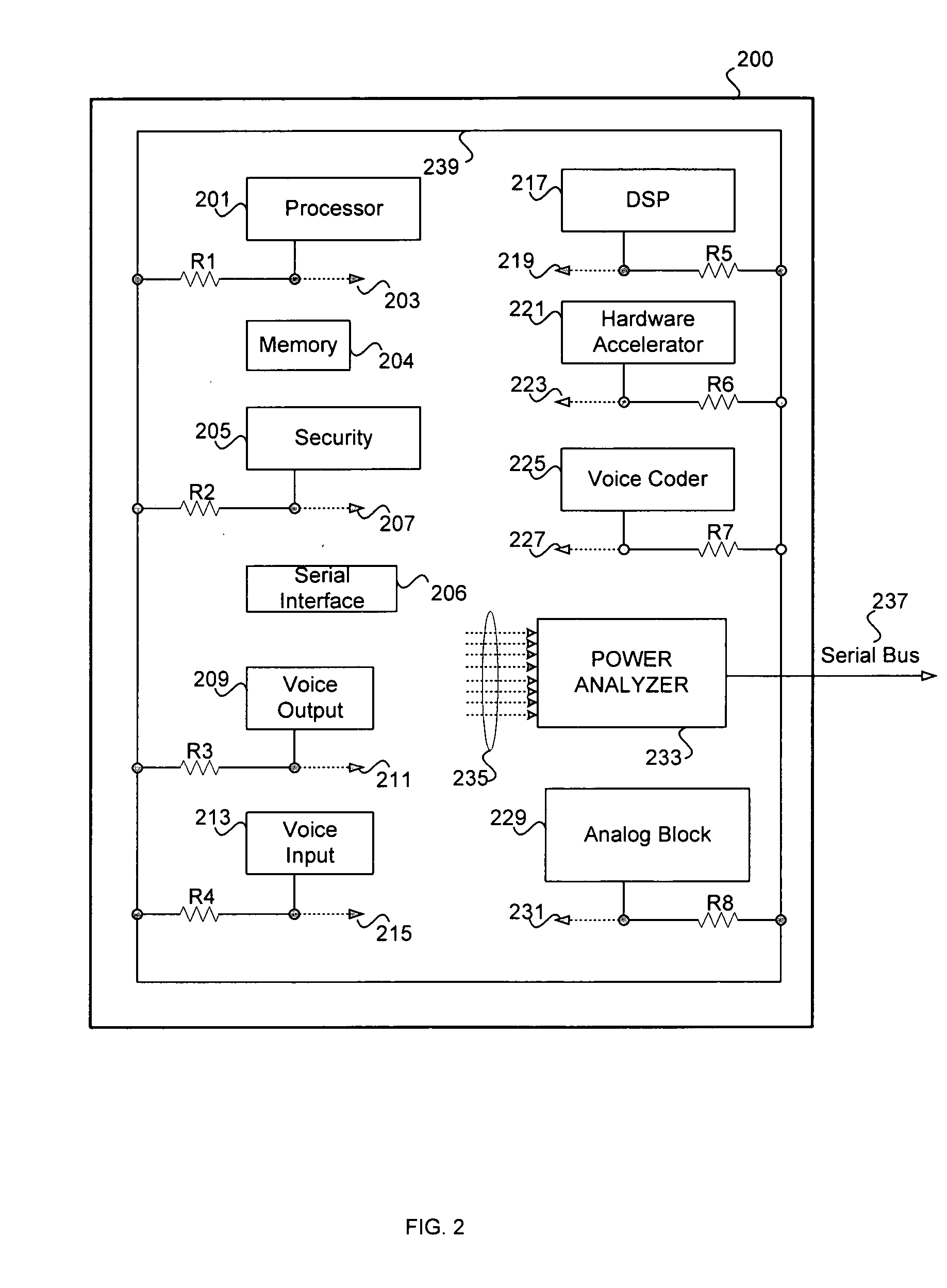

Method and system for monitoring module power status in a communication device

Methods and systems for monitoring operating status of a device are provided. Aspects of the method may include receiving within a chip, a signal indicative of a power status of an on-chip device. An output signal indicative of the power status may be generated from within the chip, while the chip is operating. The generated output signal may be communicated outside the chip via a serial bus, a plurality of pin connections on said chip, and / or a general purpose input / output connection. The generated output signal may be multiplexed on at least one pin on the chip and it may comprise a clock signal and / or a data signal. The data signal may comprise sequential power status information for a plurality of on-chip devices.

Owner:AVAGO TECH WIRELESS IP SINGAPORE PTE

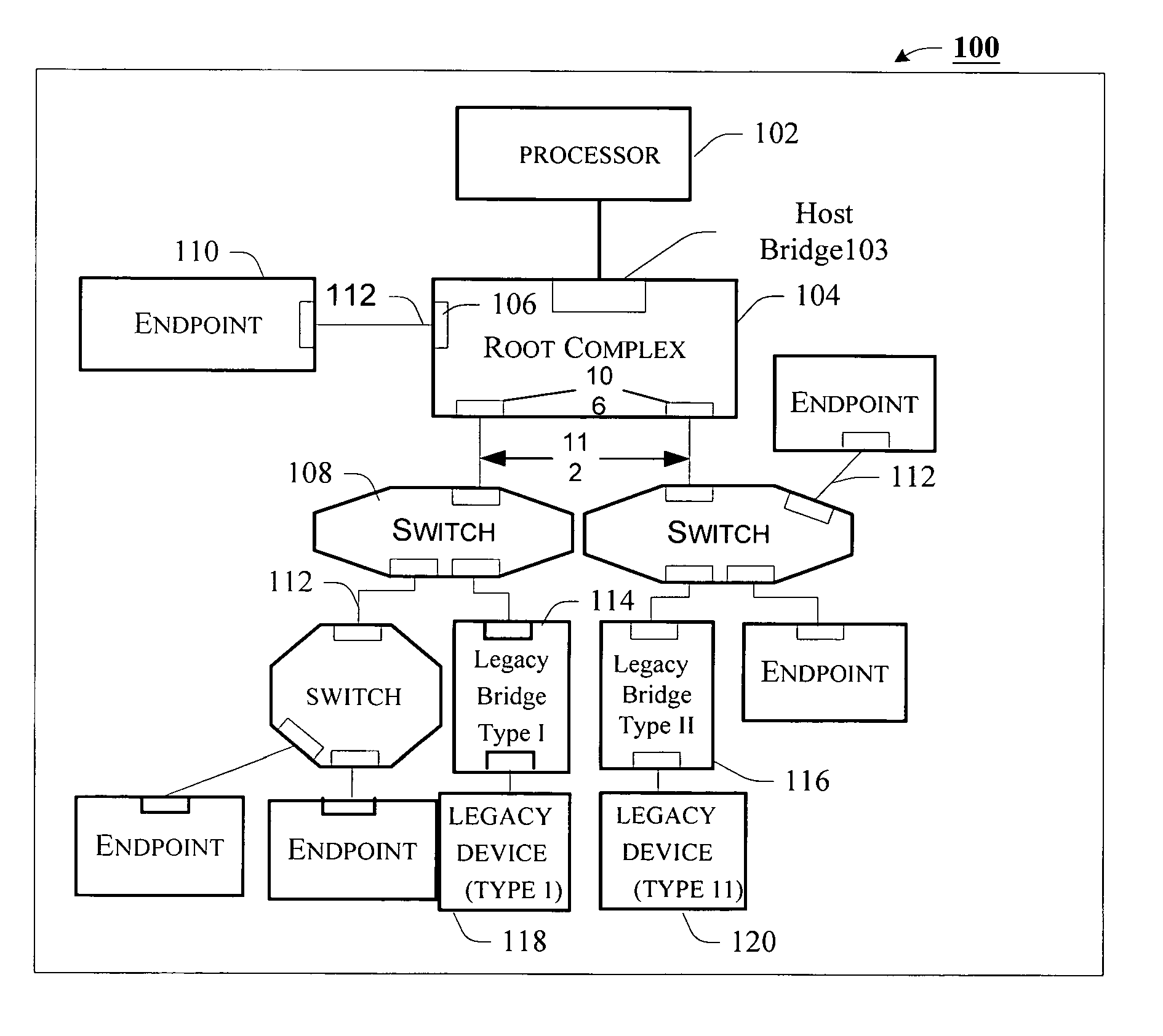

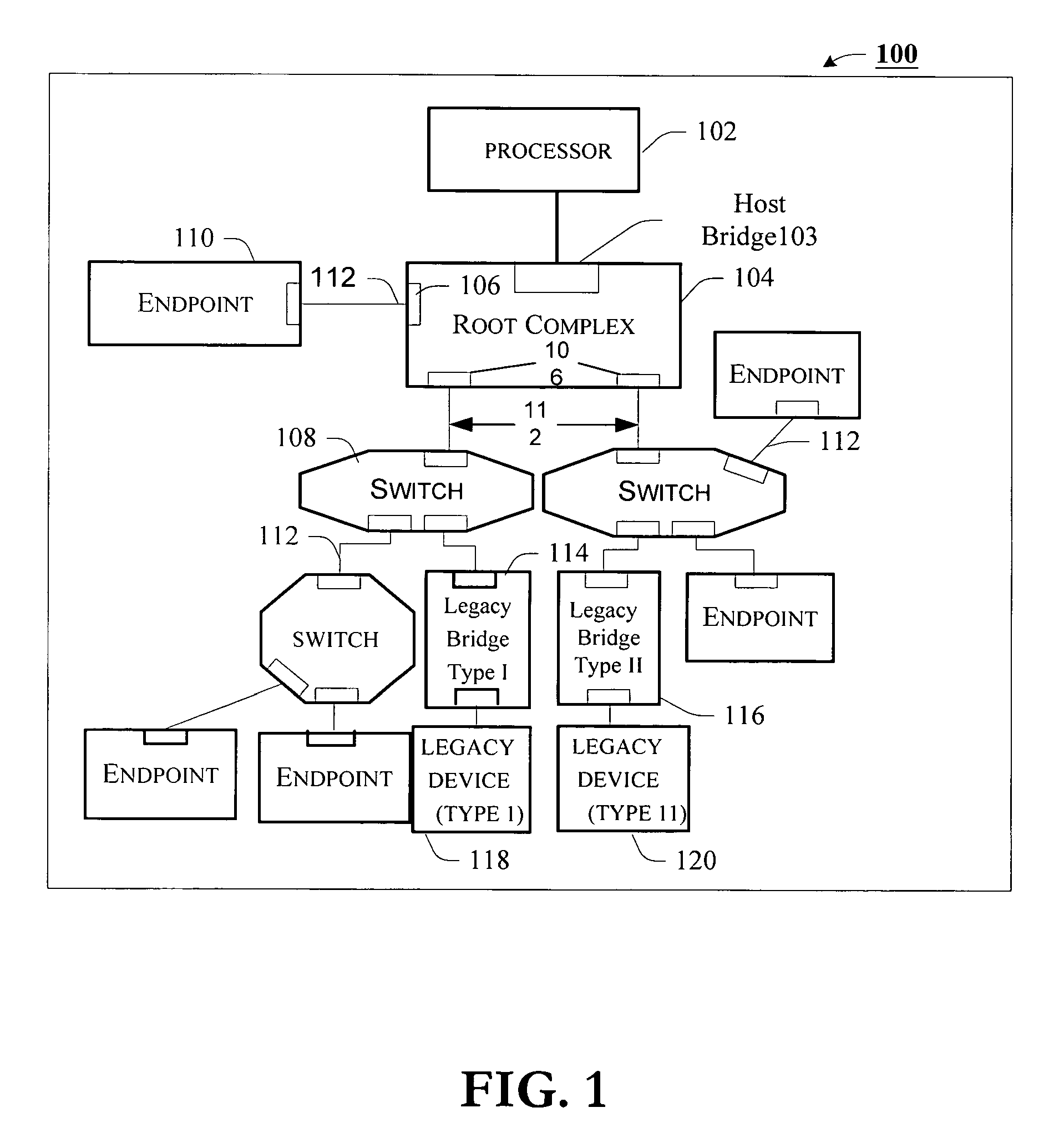

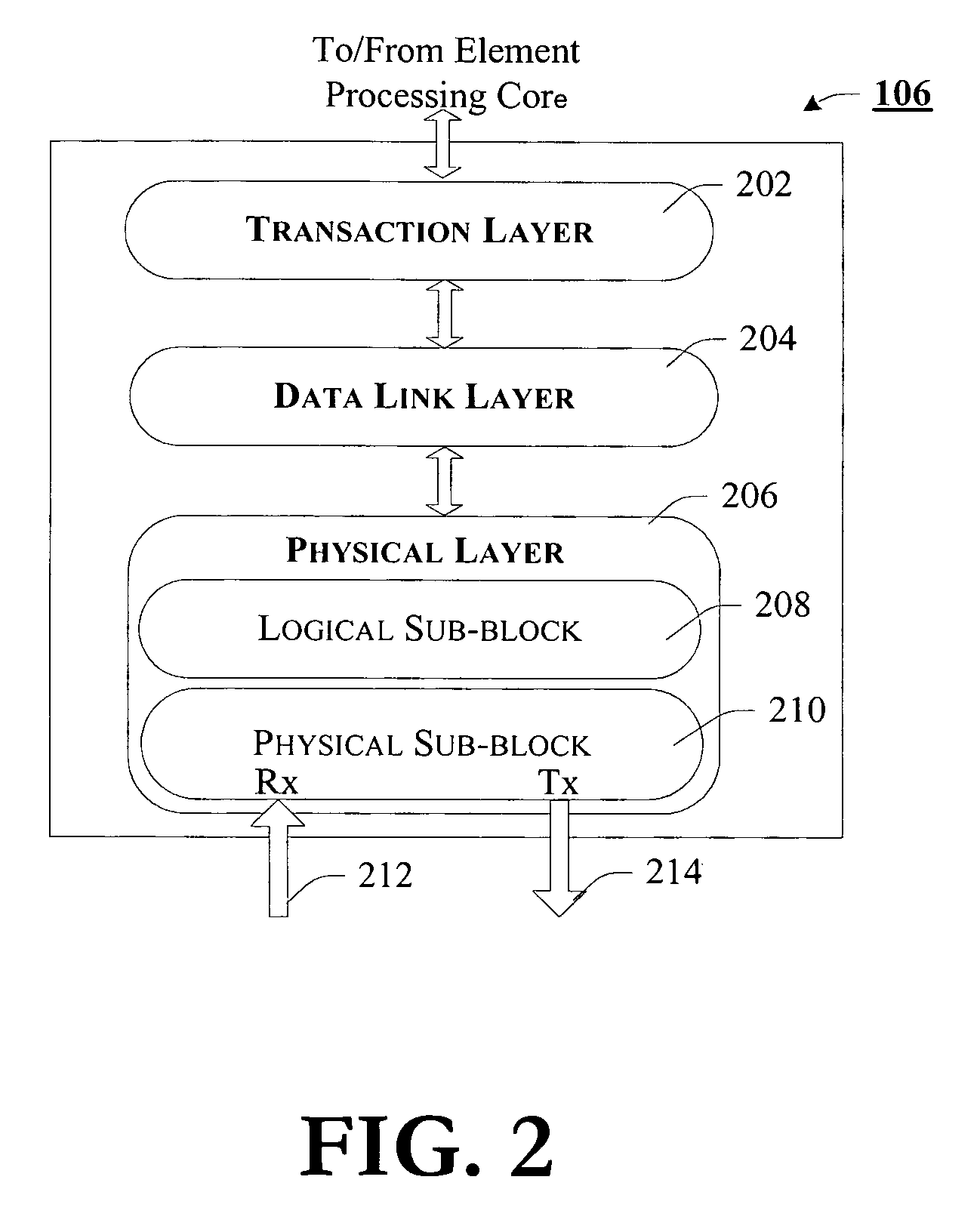

Communicating message request transaction types between agents in a computer system using multiple message groups

InactiveUS7769883B2Error detection/correctionTime-division multiplexComputerized systemData link layer

A general input / output communication port implements a communication stack that includes a physical layer, a data link layer and a transaction layer. The transaction layer includes assembling a packet header for a message request transaction to one or more logical devices. The packet header includes a format field to indicate the length of the packet header and to further specify whether the packet header includes a data payload, a subset of a type field to indicate the packet header relates to the message request transaction and a message field. The message field includes a message to implement the message request transaction. The message includes at least one message that is selected from a group of messages. The group of messages to include a message to unlock a logical device, a message to reset a logical device, a message to indicate a correctable error condition, a message to indicate an uncorrectable error condition, a message to indicate a fatal error condition, a message to report a bad request packet, a message to indicate power management and a message to emulate an interrupt signal.

Owner:INTEL CORP

Online updating device for configuration files of programmable logic device

InactiveCN102436385ALow costVersatilityProgram loading/initiatingProgramme control in sequence/logic controllersData streamProgrammable logic device

The invention discloses an online updating device for configuration files of a programmable logic device. In an upper computer, a program package module extracts and updates the configuration files and converts the updated configuration files into standard test and programming language (STAPL) standard input files required by a Jam STAPL Byte-Code Player analysis program. A data transmitting module converts the STAPL standard input files into internet signals and transmits the internet signals to cables, and then a data receiving buffer module receives jbc files from the cables, verifies the files and preserves the files in a program storage. A program analysis module extracts configuration information of the programmable logic device from the jbc files in a data storage, the configuration information of the programmable logic device can be converted into joint test action group (JTAG) data stream through the Jam STAPL Byte-Code Player program in the program analysis module and transmits the JTAG data stream to a general purpose input / output (GPIO) simulation JTAG module. A GPIO of a microprocessor is used as a standard JTAG interface, configuration time sequence of a standard JTAG is simulated through a driving program, only four GPIOs of the microprocessor are used, and a hardware circuit is very simple. Compared with a traditional configuration method of the programmable logic device, cost is reduced greatly.

Owner:UNIV OF ELECTRONIC SCI & TECH OF CHINA