High Dynamic Range Subsampling Architecture

A high dynamic range and state-of-the-art technology, applied in TV, color TV parts, TV system parts, etc., can solve problems such as full well

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment approach

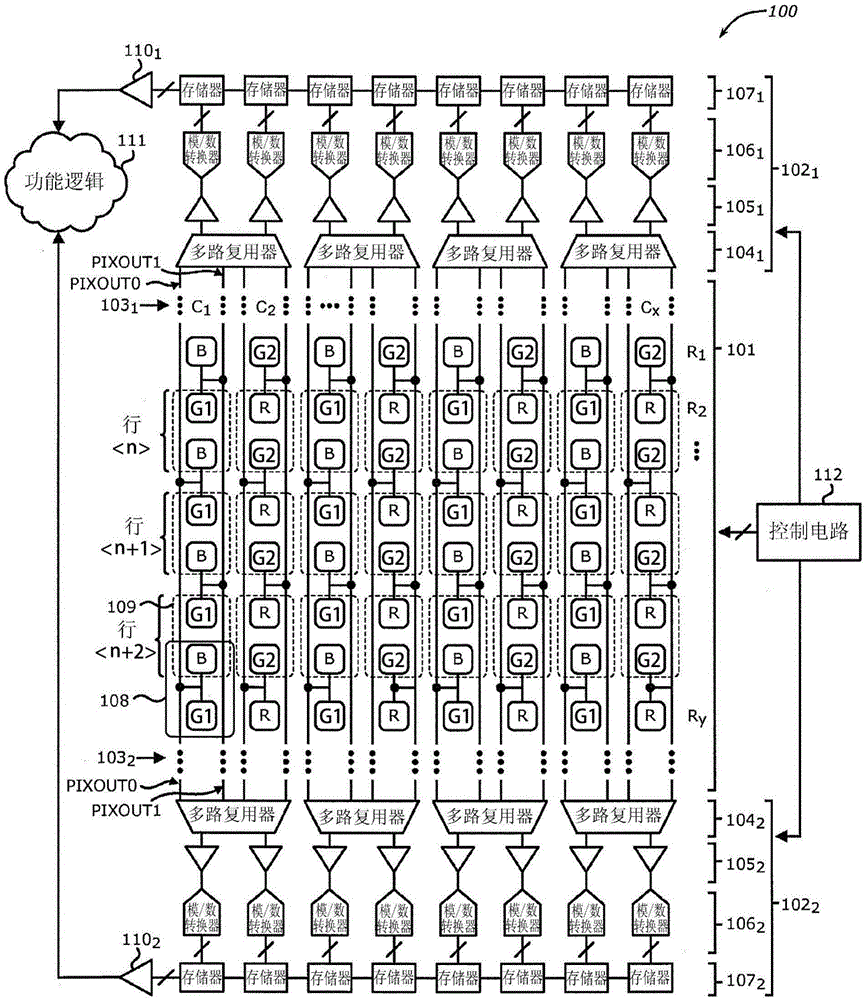

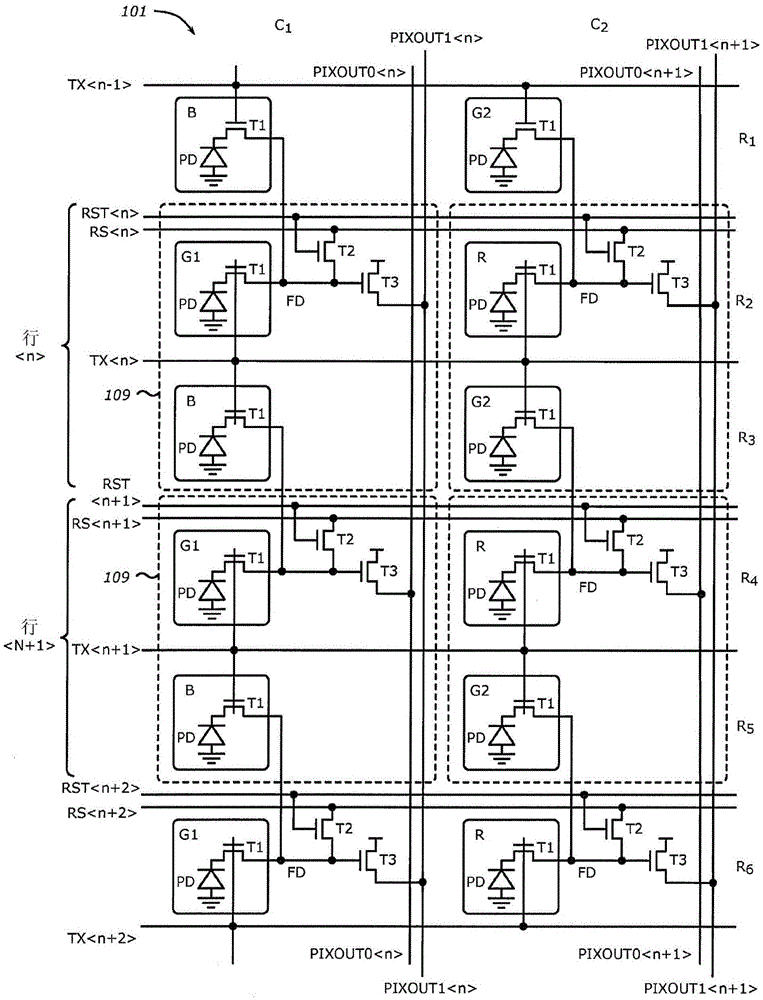

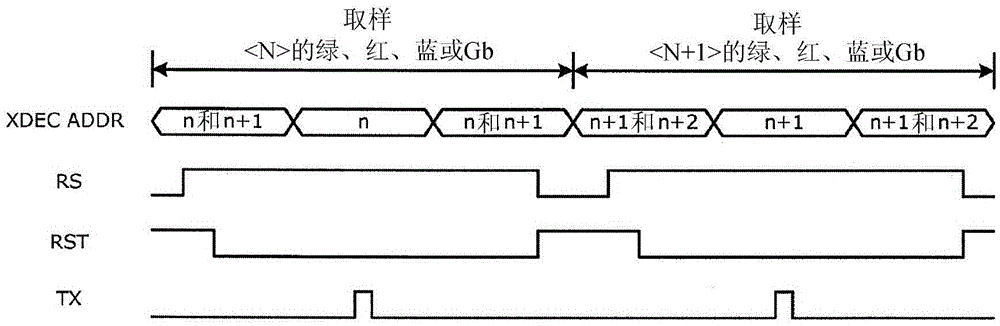

[0072] Pixel implementation, row drivers and timing

[0073] figure 2 An example of a pixel array in a multi-line simultaneous readout scheme according to an embodiment of the present invention will be described. in figure 2 In the embodiment in, two shared no-line selection pixels are used as an example. In another embodiment, other pixel structures and variations can be used. A logical unit cell 109 (enclosed by a dashed line) contains two pixels that have the same row decoder address (for example, row ) And share the same row of driver signals, the same transmission (TX) line, and the same reset (RST) and set (RS) signals.

[0074] in figure 2 , The pixels are arranged in two columns (for example, columns C1 and C2) and six rows (for example, rows R1, R2...R6). The illustrated embodiment of each pixel circuit includes a photodiode PD, a transfer transistor T1, a reset transistor T2, and a select transistor T3. During operation, the transfer transistor T1 receives the tran...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More