Multiple-row concurrent readout scheme for high-speed CMOS image sensor with backside illumination

A counter and arithmetic technology, applied in the arithmetic counter circuit, configuration and application field of high-performance CMOS image sensor, can solve the problem of full well and so on

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment approach

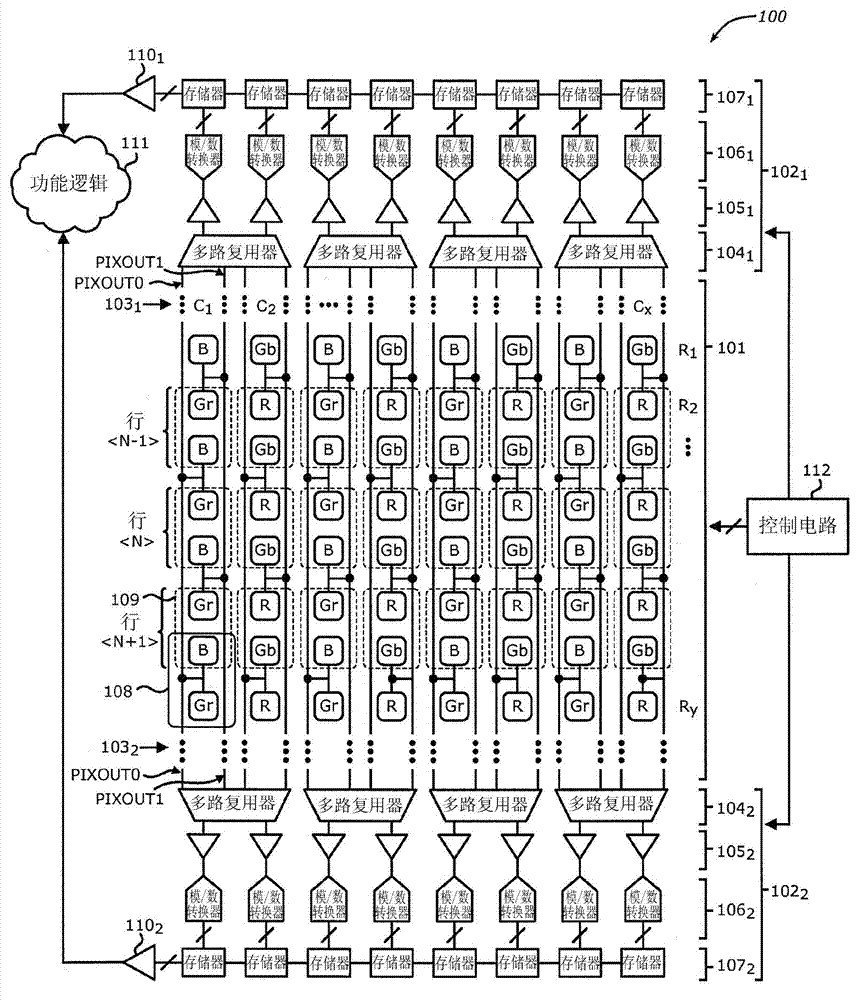

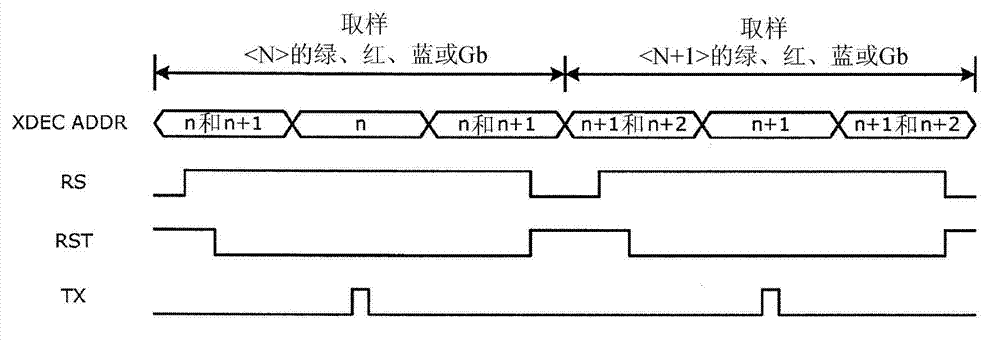

[0072] Pixel Implementation, Row Drivers, and Timing

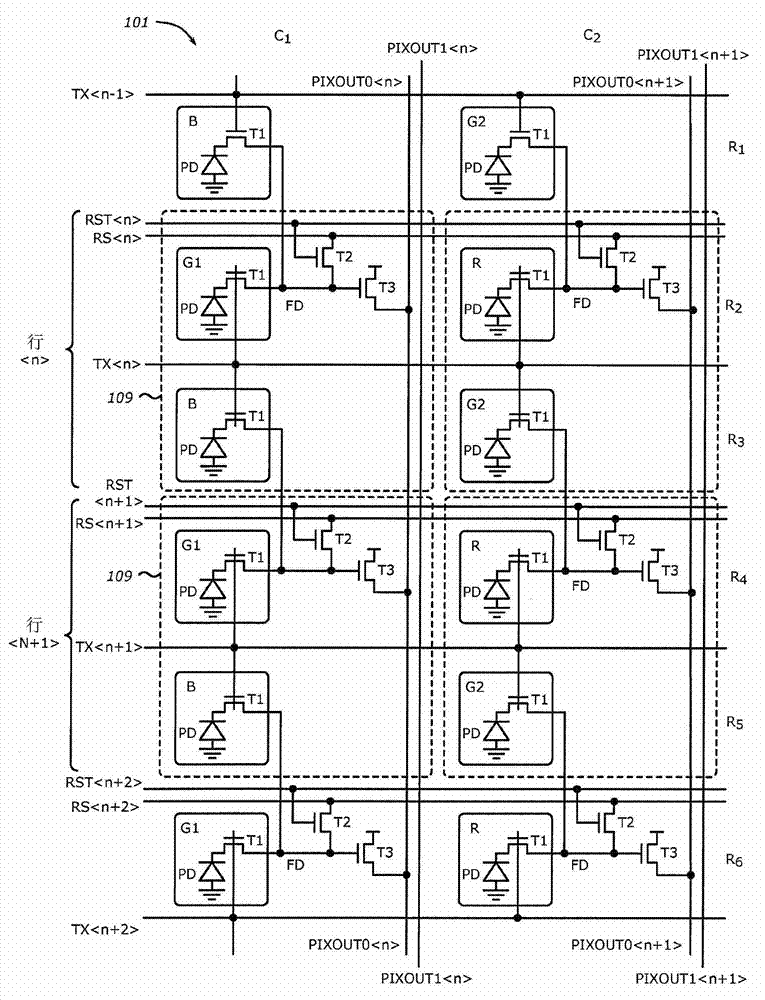

[0073] figure 2 An example of a pixel array in a multi-row simultaneous readout scheme according to an embodiment of the present invention is illustrated. exist figure 2 In the embodiment in , two shared non-row selection pixels are used as an example. In other embodiments, other pixel structures and variations may be used. One logical unit cell 109 (outlined with a dotted line) contains two pixels that have the same row decoder address (e.g., row ) and share the same row driver signal, the same transmit (TX) line, and the same reset (RST) and set (RS) signals.

[0074] exist figure 2 , pixels are arranged in two columns (for example, columns C1 and C2 ) and six rows (for example, rows R1 , R2 . . . R6 ). The illustrated embodiment of each pixel circuit includes a photodiode PD, transfer transistor Tl, reset transistor T2, and select transistor T3. During operation, transfer transistor T1 receives a tran...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More