Management system and method of processor last level high-speed buffer

A last-level cache and management system technology, applied in the field of last-level cache management systems, can solve the problems of limited performance improvement and difficult to achieve, and achieve the effect of low cost

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0044] The technical solutions of the present invention will be described in detail below in conjunction with the accompanying drawings and preferred embodiments. It should be understood that the following examples are only used to illustrate and explain the present invention, but not to limit the technical solution of the present invention.

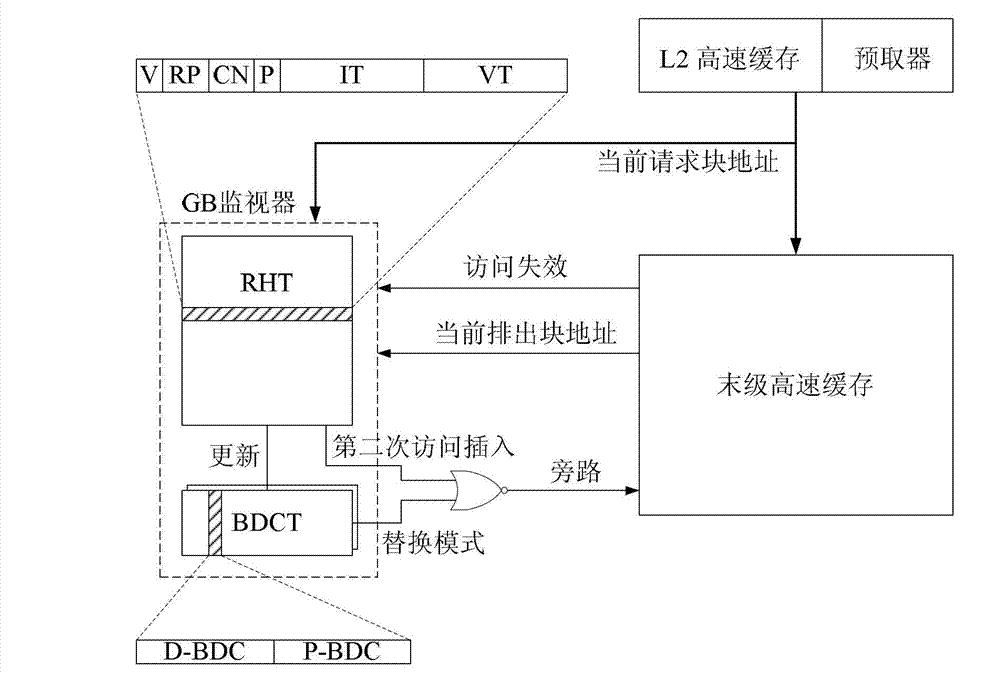

[0045] Such as figure 1 Shown is an embodiment of the management system of the processor's last-level cache of the present invention, including a coarse-grained bypass (GB) monitor and the last-level cache, wherein:

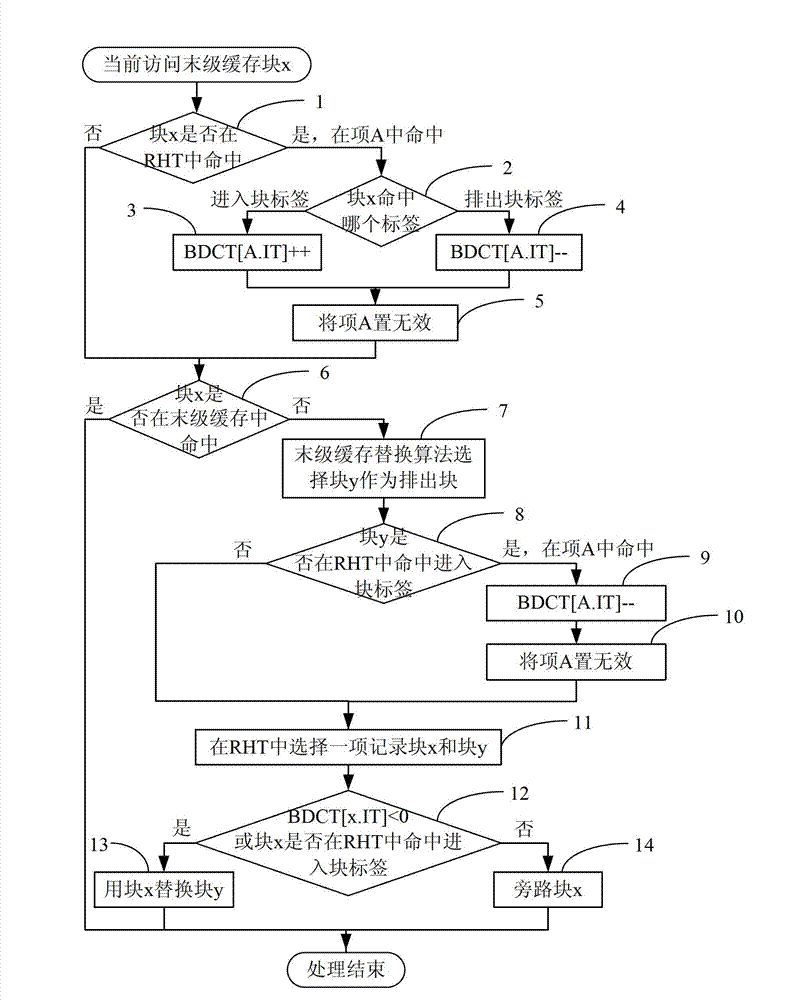

[0046] The GB monitor is used to record the incoming block and outgoing block pair when each last-level cache access fails, and guides the switching of the replacement mode or the bypass mode by learning the behavior of the optimal bypass algorithm, the optimal bypass algorithm Behaviors are formed by accumulating the actions of selecting the last-level cache to adopt the replacement method and the bypass method according ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More