Manufacturing method of separated grid type flash memory with peripheral circuit

A manufacturing method and technology of peripheral circuits, which are applied in the fields of circuits, semiconductor/solid-state device manufacturing, electrical components, etc., can solve the problems of polysilicon residue and uneven surface of silicon oxide layer, and achieve the effect of avoiding poor terminal isolation.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

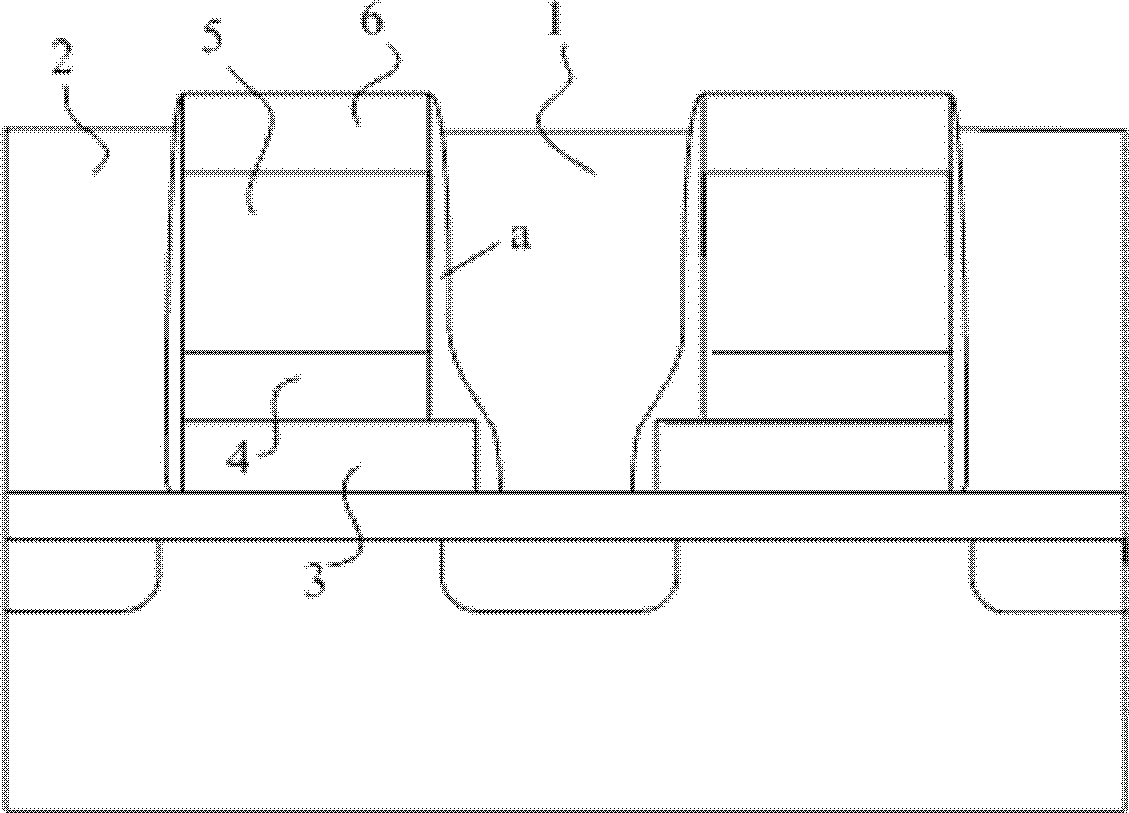

[0028] As described in the background technology, during the formation process of the word line gate and the polysilicon layer of the erasable gate on both sides of the separated gate structure, the thickness is difficult to control and cannot meet the ideal requirements, which in turn leads to breakdown between devices The voltage dropped drastically, from the expected 18V, to less than 10V. In view of the problems referred to above, the inventor of the present invention has proposed a kind of word line manufacturing method of the split-gate flash memory with peripheral circuit, and it comprises the following steps:

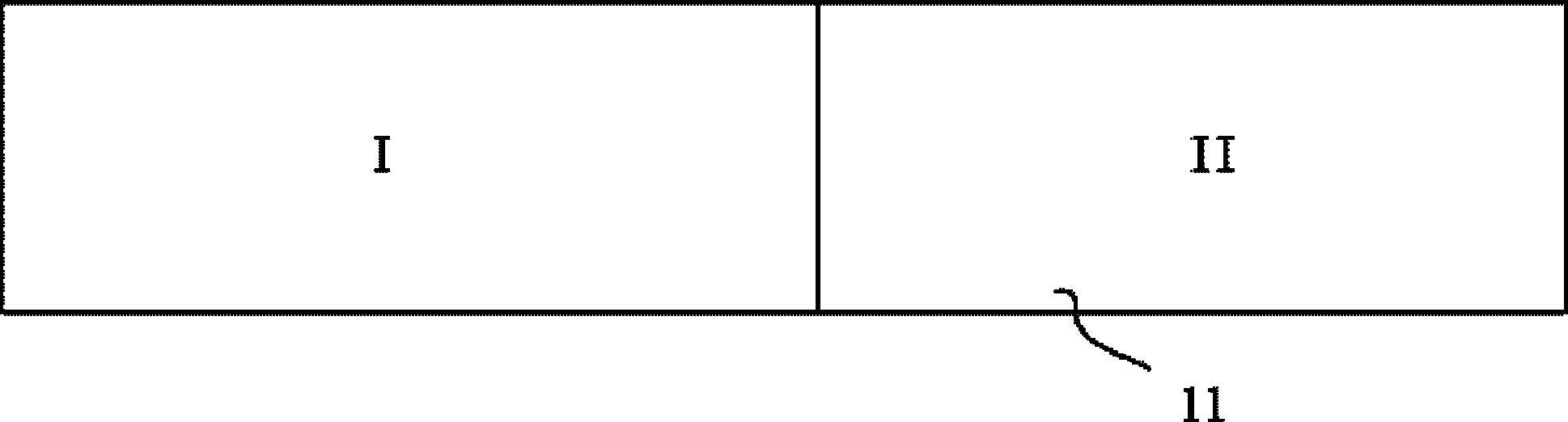

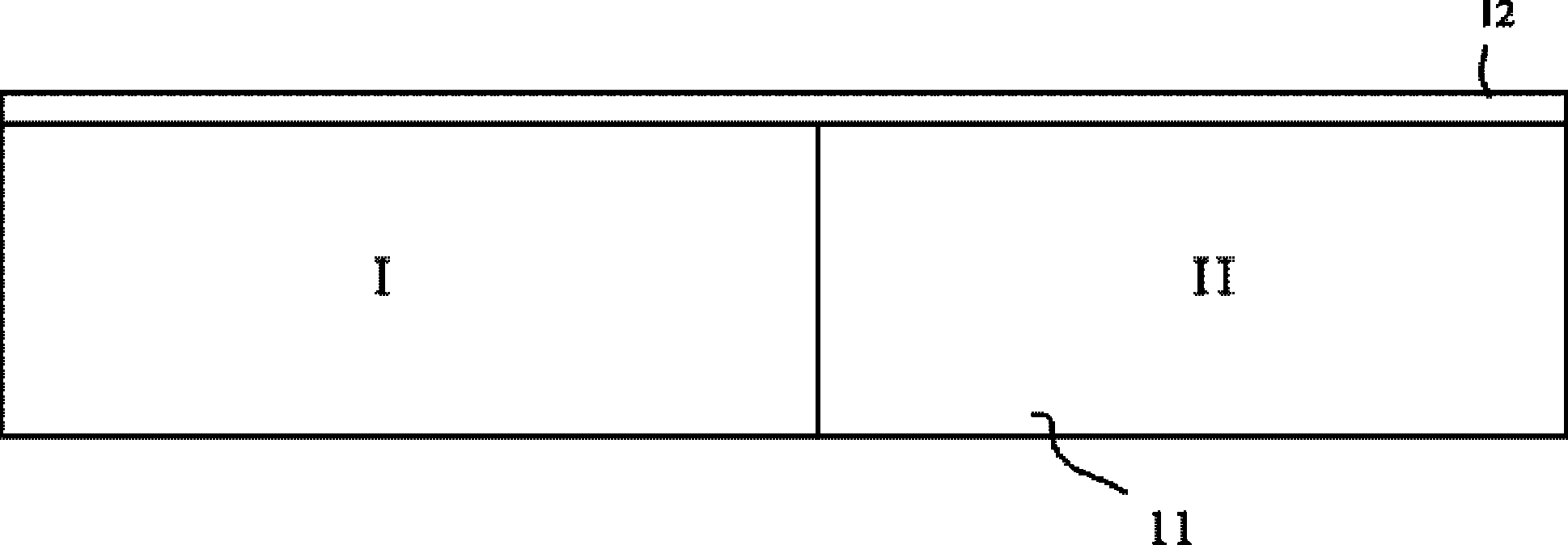

[0029] S1: Provide a semiconductor substrate, the semiconductor substrate includes a first region and a second region, a split-gate flash memory transistor will be subsequently formed on the first region, and a peripheral circuit transistor will be subsequently formed on the second region;

[0030] S2: Form a gate stack in the first region, the gate stack includ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More