Method for forming fin field effect transistor

A fin field effect and transistor technology, which is applied in semiconductor/solid-state device manufacturing, electrical components, circuits, etc., can solve problems such as difficulty in ensuring stable performance of fin field effect transistors, and achieve uniform distribution of ion implantation

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

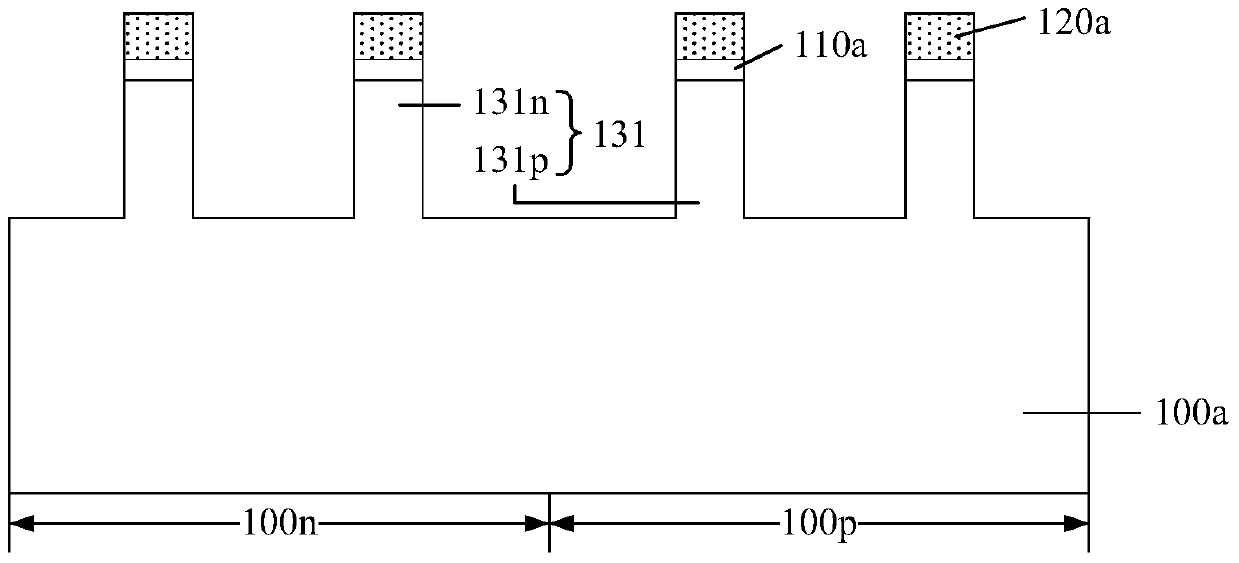

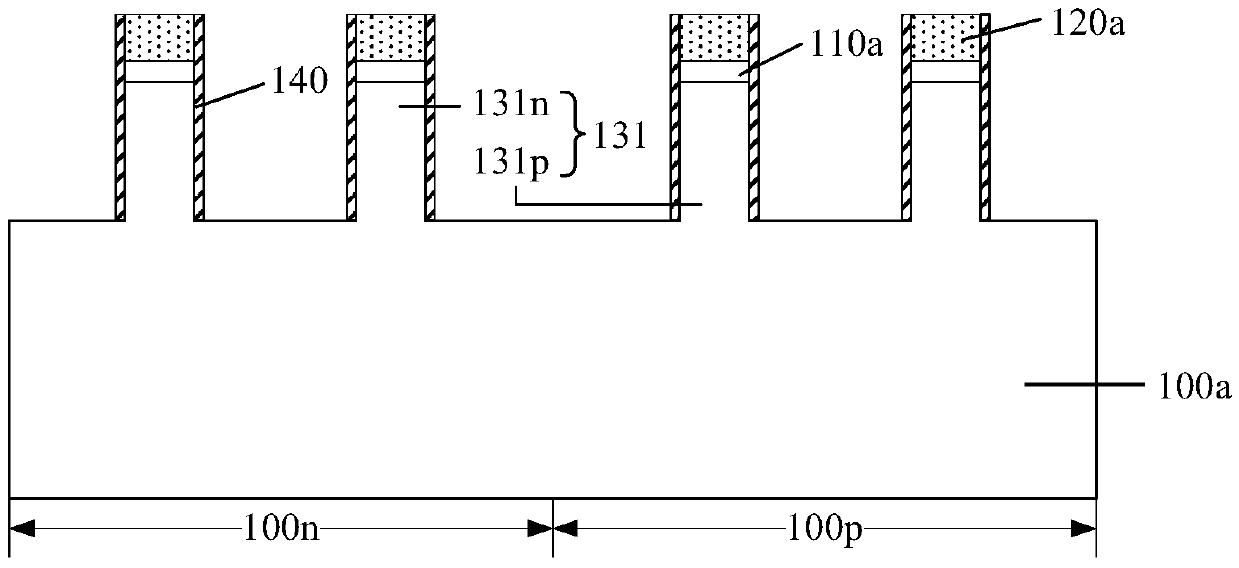

[0031] An embodiment of the present invention provides a method for forming a fin field effect transistor, which will be described in detail below with reference to the accompanying drawings.

[0032] Figure 1 to Figure 13 It is a schematic cross-sectional view of an intermediate structure of a method for forming a fin field effect transistor according to a specific embodiment of the present invention.

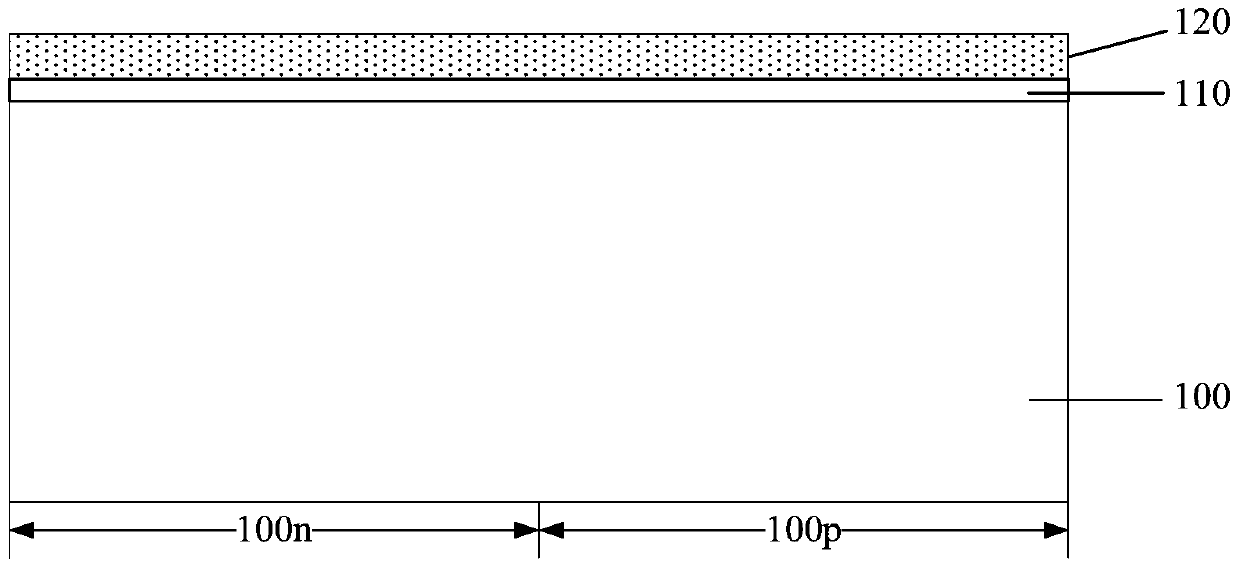

[0033] refer to figure 1 A substrate 100 is provided, and a pad layer 110 and a mask layer 120 are sequentially formed on the surface of the substrate 100 .

[0034] The substrate 100 includes an adjacent NMOS region 100n and a PMOS region 100p. The NMOS region 100n is subsequently used to form an NMOS transistor, and the PMOS region 100p is used to form a PMOS transistor. The substrate 100 is used to provide a platform for subsequent processes, and to form fins by etching.

[0035] In the embodiment of the present invention, the substrate 100 may be a silicon substrate, ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More