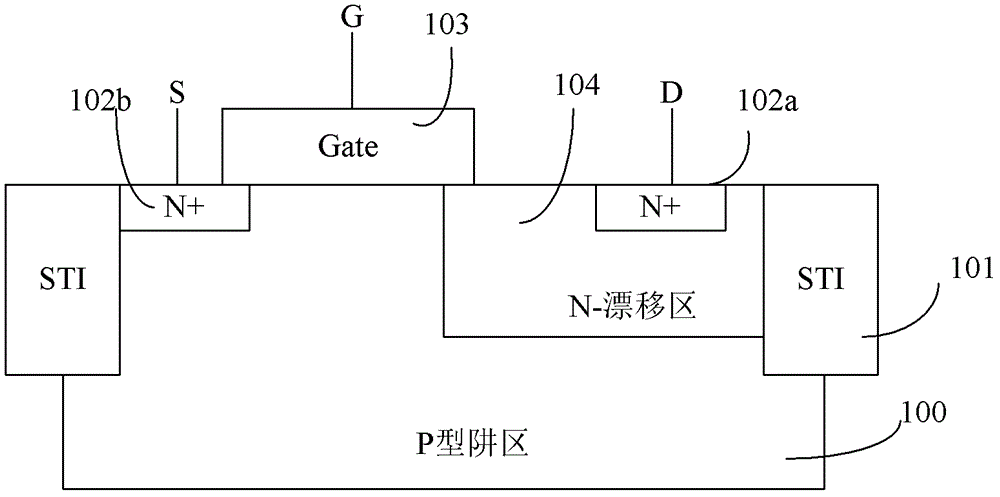

ldmos transistor and its manufacturing method

A manufacturing method and transistor technology, which are applied in semiconductor/solid-state device manufacturing, semiconductor devices, electrical components, etc., can solve problems such as reducing device area, and achieve the effect of improving breakdown voltage and high breakdown voltage

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

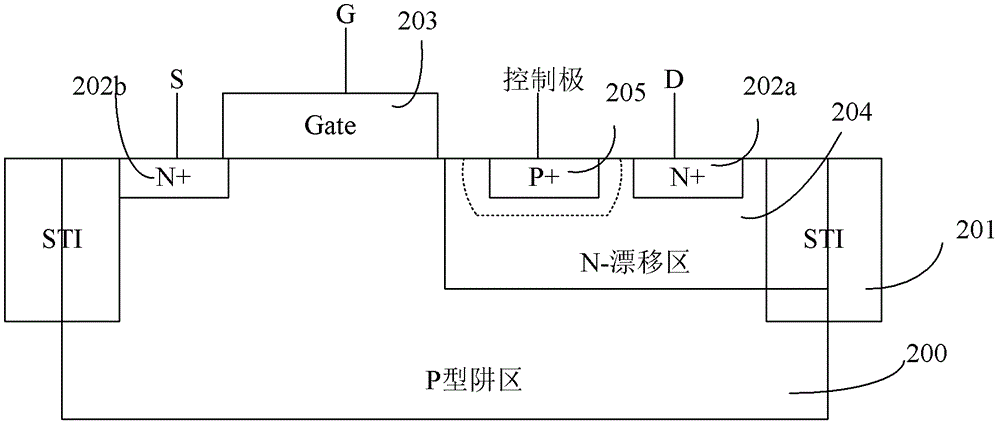

[0030] The LDMOS transistor and its manufacturing method proposed by the present invention will be further described in detail below with reference to the drawings and specific embodiments.

[0031] like figure 2 As shown, the present invention proposes an LDMOS transistor, which includes a semiconductor substrate 200 having a well region, a source region 202b and a drain region located in the surface of the semiconductor substrate 200, and a gate located above the semiconductor substrate 200 ( Gate) 203, wherein the drain region includes a drain drift region 204, a drain contact region 202a located in the drain drift region 204, and a drain tuning region 205 located in the drain drift region 204 and close to the gate 203, The doping type of the drain tuning region 205 is opposite to that of the drain contact region 202a.

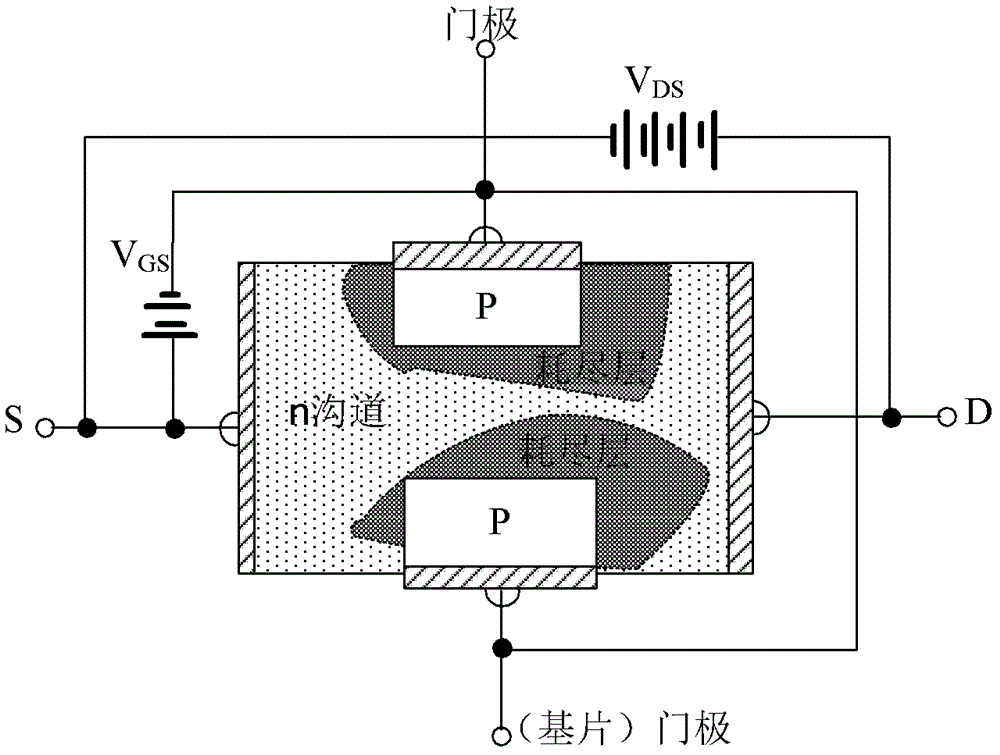

[0032] When the well region and the drain tuning region 205 are P-type, the source region 202b, the drain drift region 204 and the drain contact region 2...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More