Instruction obtaining device for processor and processor with same

A technology for obtaining devices and processors, which is applied in the direction of machine execution devices and concurrent instruction execution, which can solve the problems of time-consuming and long instruction time, and achieve the effect of saving addressing time and reducing instruction output time

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0016] Embodiments of the present invention will be further described below in conjunction with the accompanying drawings.

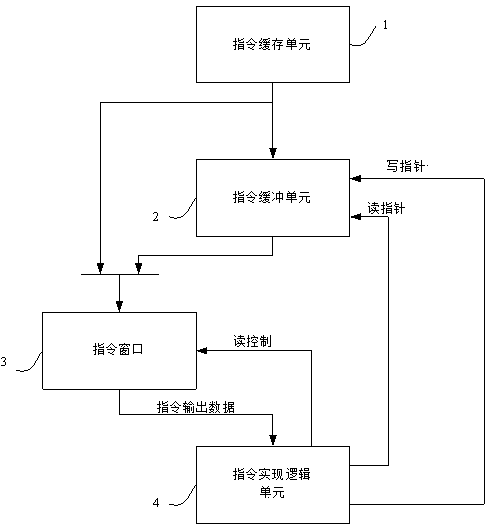

[0017] Such as figure 1 As shown, in a device for obtaining instructions in a processor and its processor embodiment of the present invention, the device for obtaining instructions in a processor includes an instruction cache unit 1, an instruction buffer unit 2, and an instruction window 3 and instruction implementation logic unit 4; basically, the above-mentioned instruction cache unit 1 and instruction buffer unit 2 form a secondary cache (cache memory); this secondary cache is not directly connected to the instruction implementation logic unit 4 , but is connected with the instruction implementation logic unit 4 through the instruction window 3; that is to say, although there are other connections or signal interactions therebetween, the instruction implementation logic unit 4 will not directly access the above cache and obtain the instruction conten...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More