Power gating method and device

A technology of power gating and power enabling, which is applied in the field of integrated circuits, can solve the problems of wasting power consumption optimization space, memory access modules cannot accurately use traditional power gating methods, etc., and achieve the effect of reducing leakage power consumption

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

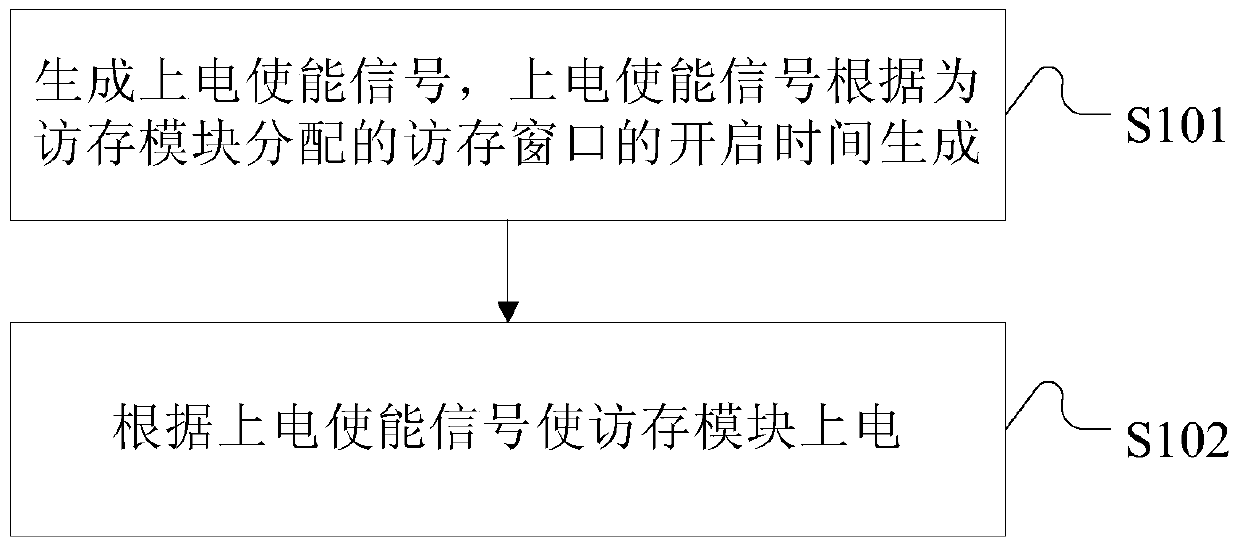

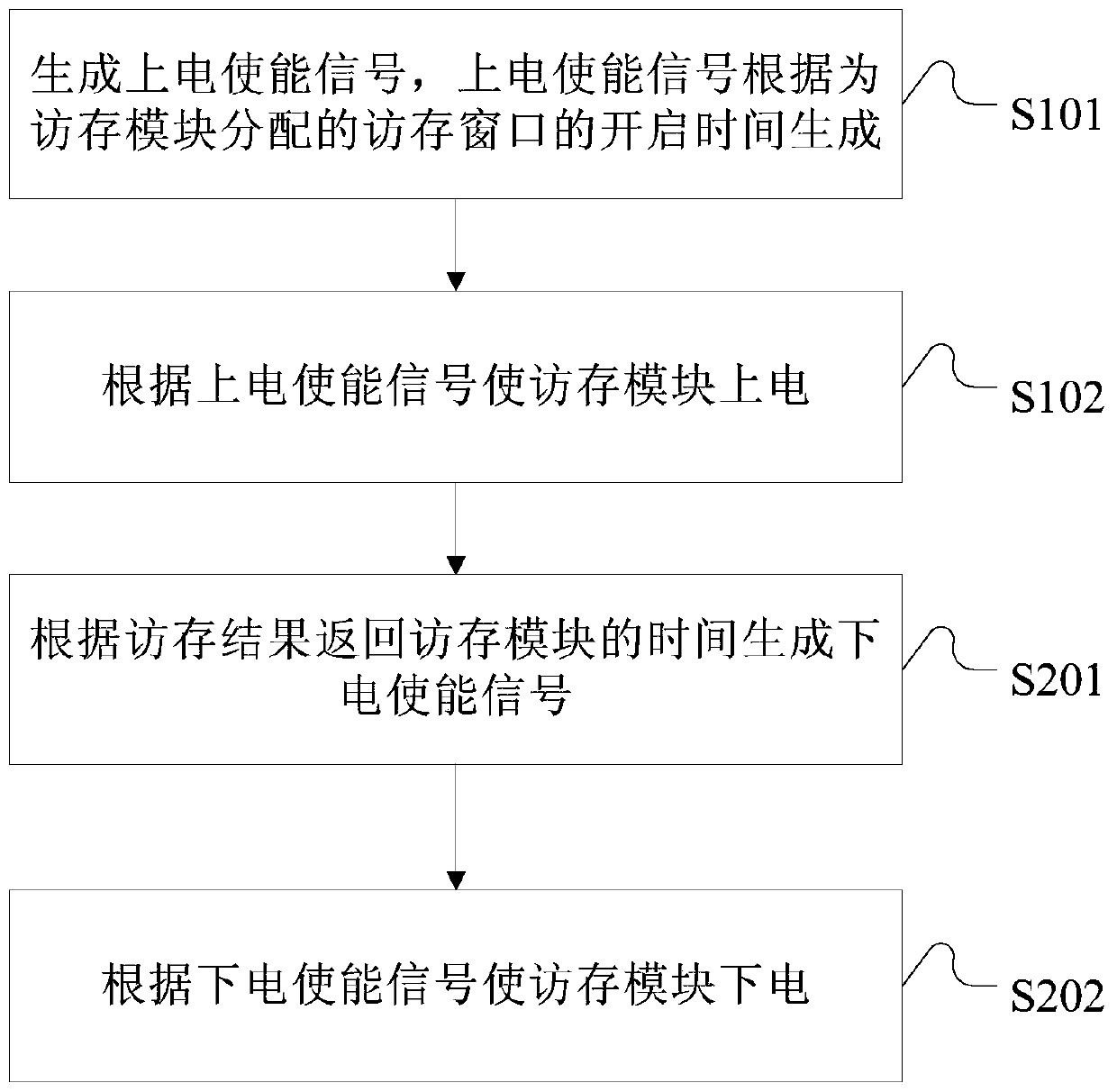

[0019] Such as figure 1 As shown, it is a schematic flow chart of Embodiment 1 of the power gating method provided by the present invention, which specifically includes the following steps:

[0020] S101. Generate a power-on enable signal, and the power-on enable signal is generated according to the opening time of the memory access window allocated for the memory access module;

[0021] Preferably, the power-on enable signal can be generated according to a preset time before the opening time of the memory access window assigned to the memory access module.

[0022] Specifically, the power-on enable signal in this embodiment can be executed by the scheduling module in the power gating device of the present invention, wherein the scheduling module can be implemented by a memory access scheduler, and the memory access scheduler can A memory access window is allocated to the memory access module, so that the memory access module sends the memory access requests intensively withi...

Embodiment 3

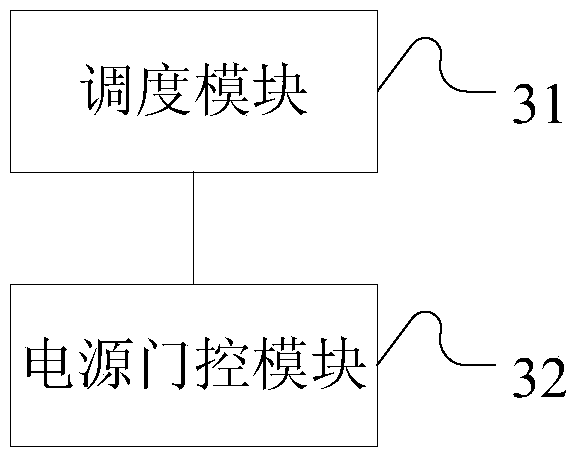

[0035] Such as image 3 As shown, it is a schematic structural diagram of an embodiment of a power gating device provided by the present invention, specifically including:

[0036] The scheduling module 31 is configured to generate a power-on enable signal, and the power-on enable signal is generated according to the opening time of the memory access window allocated for the memory access module;

[0037] Wherein, the scheduling module 31 may be a memory access scheduler in the prior art.

[0038] The power gating module 32 is configured to power on the memory access module according to the power-on enable signal generated by the scheduling module.

[0039] Further, the scheduling module 31 is further configured to: generate a power-off enable signal according to the time when the memory access result is returned to the memory access module;

[0040] Correspondingly,

[0041] The power gating module 32 is configured to: power off the memory access module according to the po...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More