A Design Optimization Method for Instruction Level Parallel Processor with Low Power Consumption

An optimization method and processor technology, applied in the direction of data processing power supply, electrical digital data processing, digital data processing components, etc., can solve the problems of random opening and closing of circuits, no consideration of additional energy consumption, and poor results

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

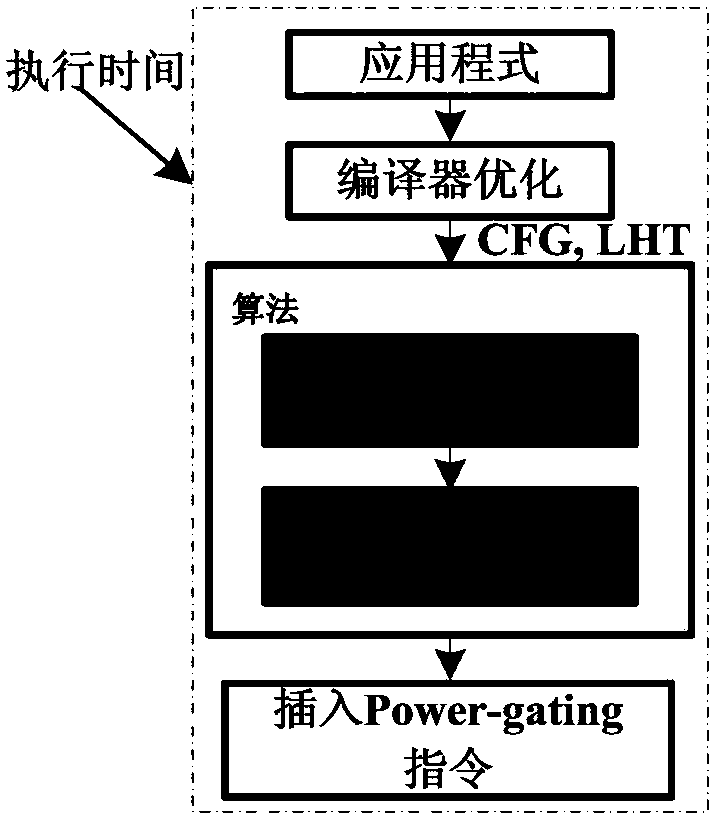

[0023] The present invention mainly uses the compiler to help analyze and schedule the instructions of the application program, analyze the execution time of the application program, the hardware demand, and the demand for parallelism, divide the application program, and set the parallelism of each area. Insert power gating command to turn off idle hardware devices and improve energy efficiency. figure 1 Shows the compiler workflow in the entire scheme. The present invention will be described below in conjunction with the accompanying drawings and embodiments.

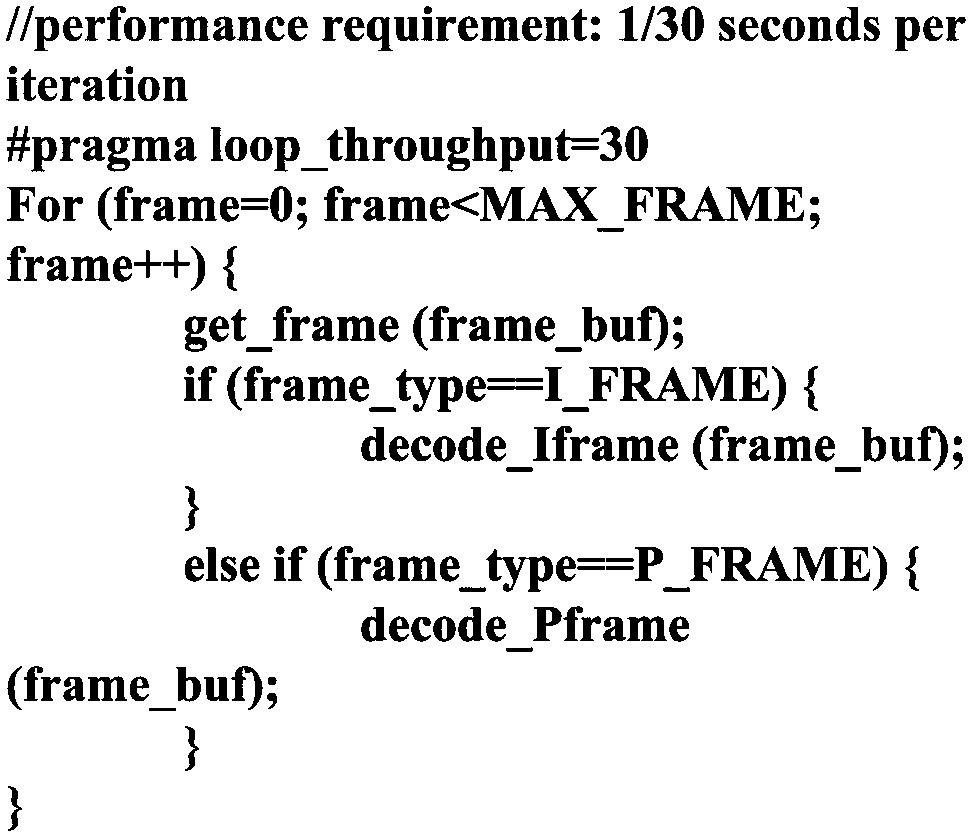

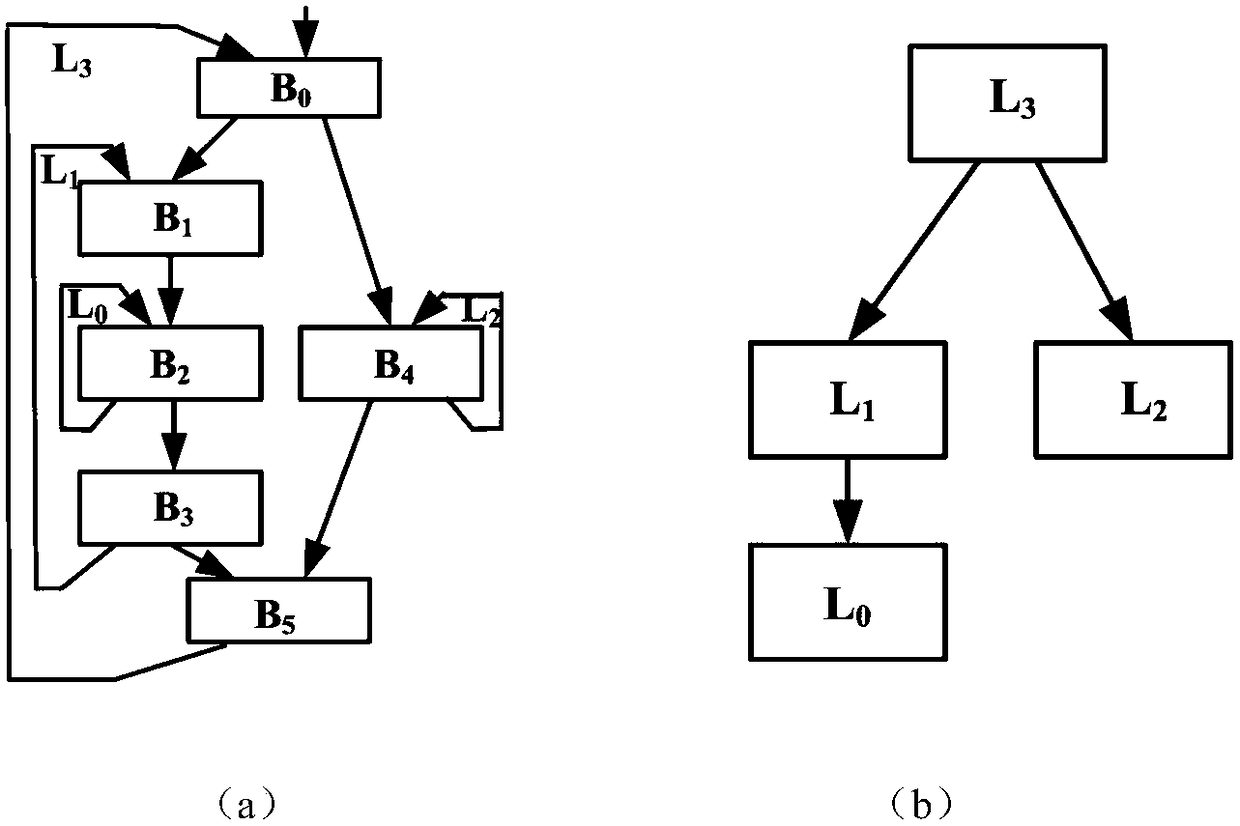

[0024] (1) Input one such as figure 2 For the application program shown, the compiler first converts such a high-level language into the bytecode of the intermediate language, and then uses the optimization tool of the compiler to extract the CFG and LHTs of this application program, such as image 3 As shown, and analyze the execution time of this program at various degrees of parallelism and the demand for hardwar...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More