Patents

Literature

33results about How to "Reduce leakage power consumption" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

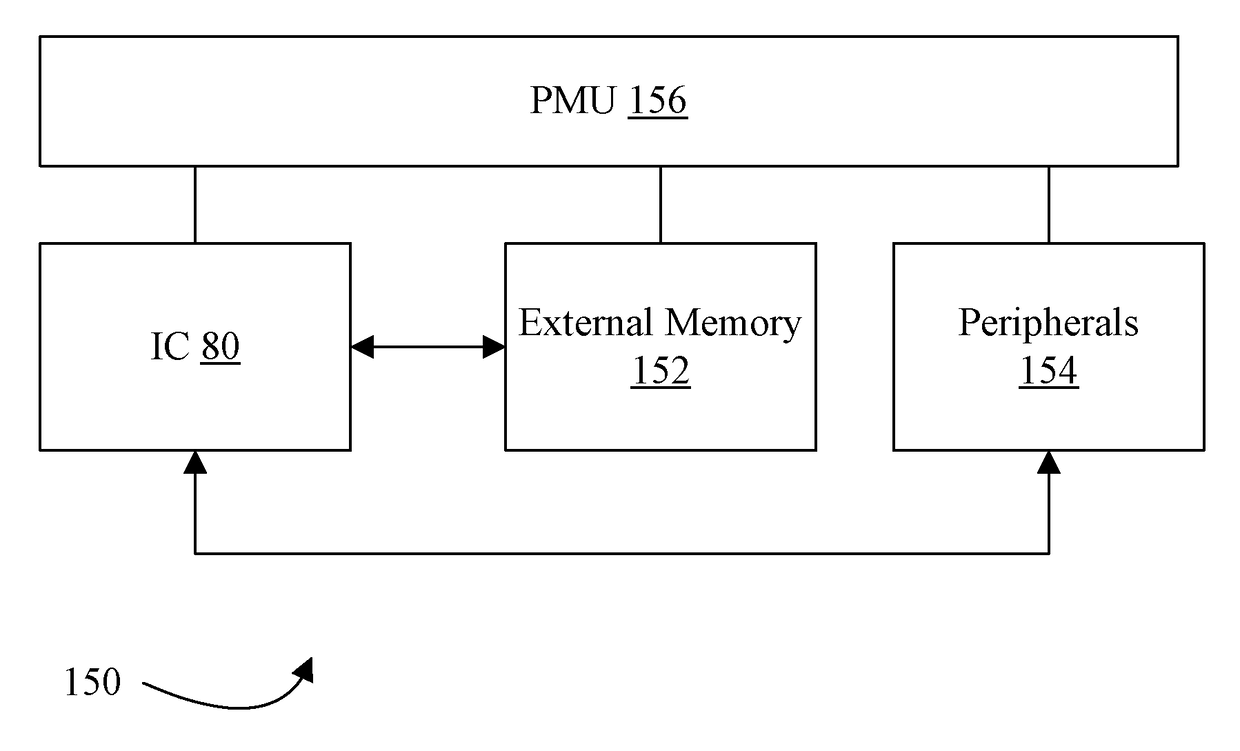

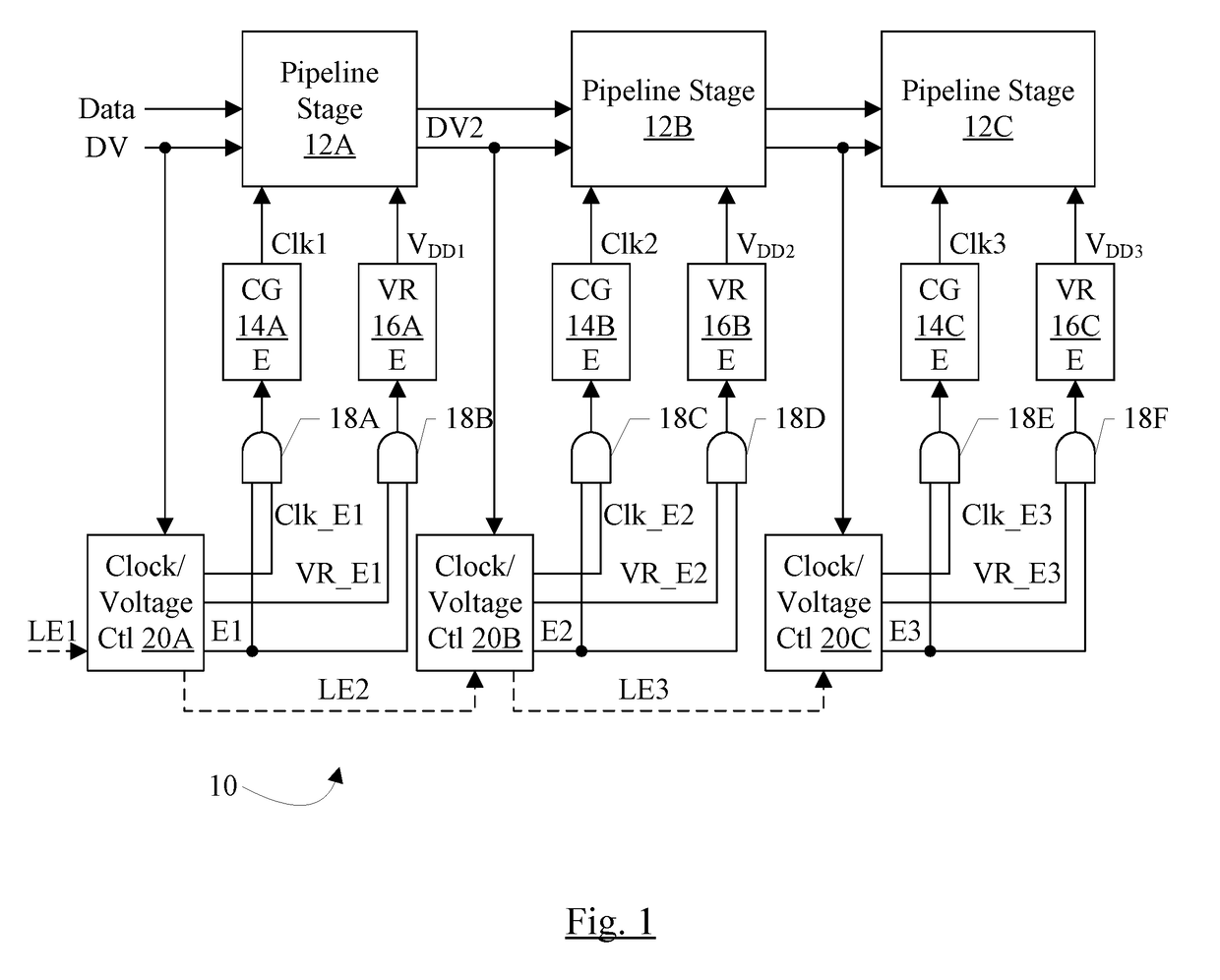

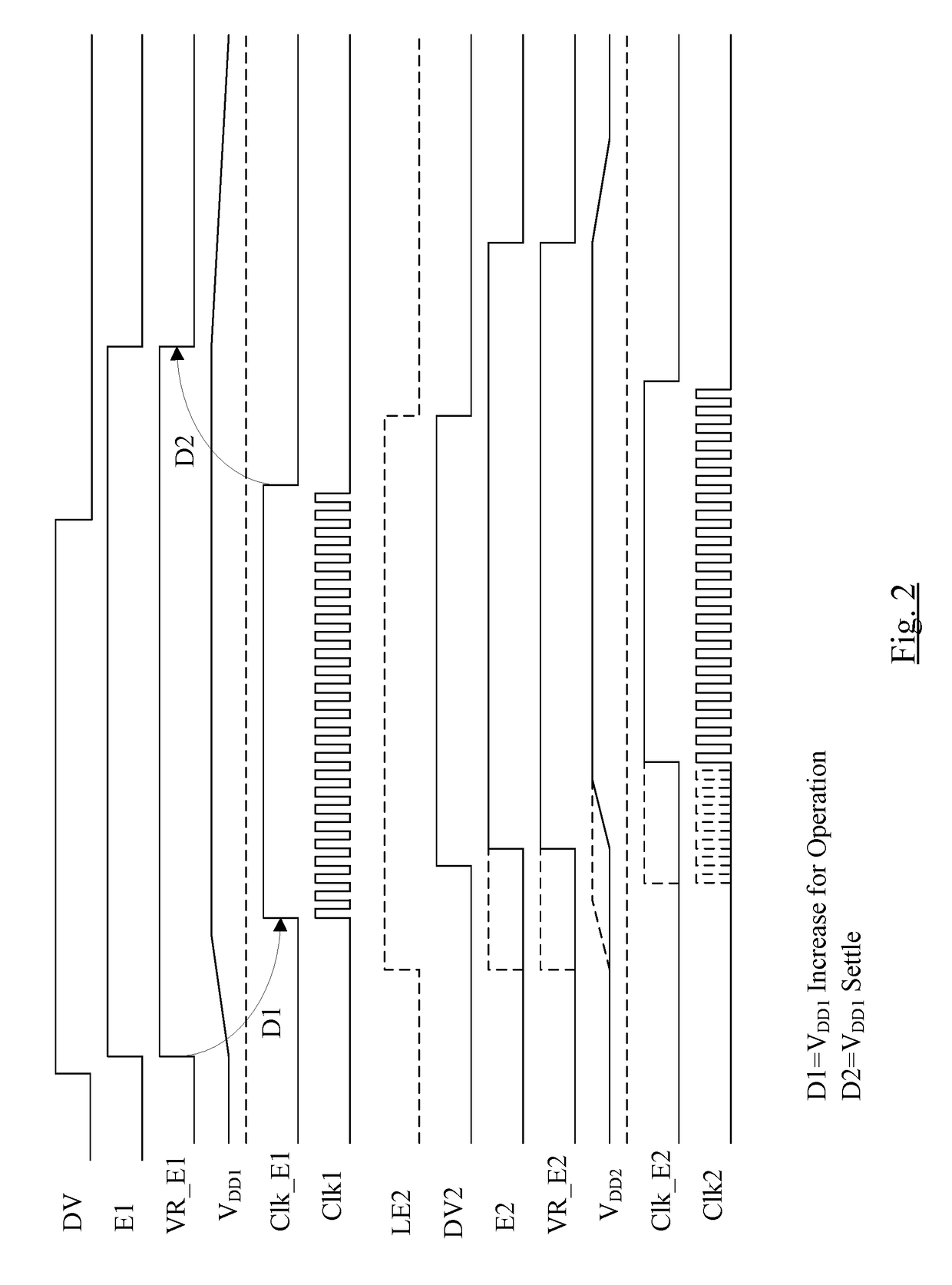

Power Management Architecture

ActiveUS20170220100A1Reduce leakage power consumptionPrevent spurious power consumptionPower supply for data processingProgram controlIntegrated circuitVoltage

In one embodiment, an integrated circuit includes a power management architecture in which one or more pipelines are actively powered and clocked when data is provided for processing, but which are clock gated and in retention when there is no data to be processed. When data is provided to the pipeline, supply voltage may be actively provided to initial stages of the pipeline and the clocks may be ungated when the voltage is stable enough for operation. Subsequent stages of the pipeline may be sequentially provided power and clocks as the data progresses through the pipeline. Initial stages may be clock gated and power may be deactivated when additional data is not provided for processing. Accordingly, when the pipeline is viewed as a whole, power may be seen as rolling forward ahead of the data processing, and power may be inhibited in a similar rolling fashion.

Owner:ALLLE INC

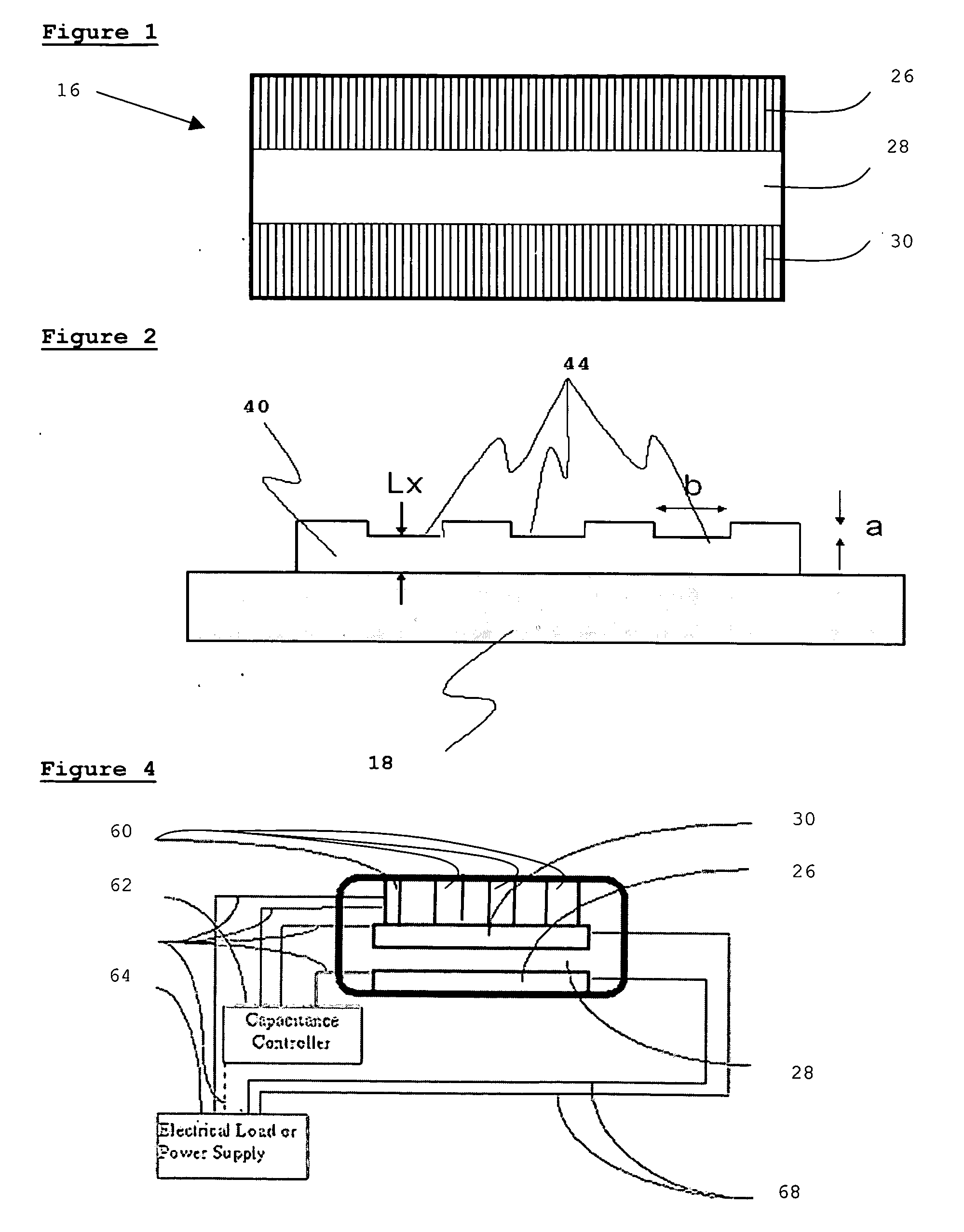

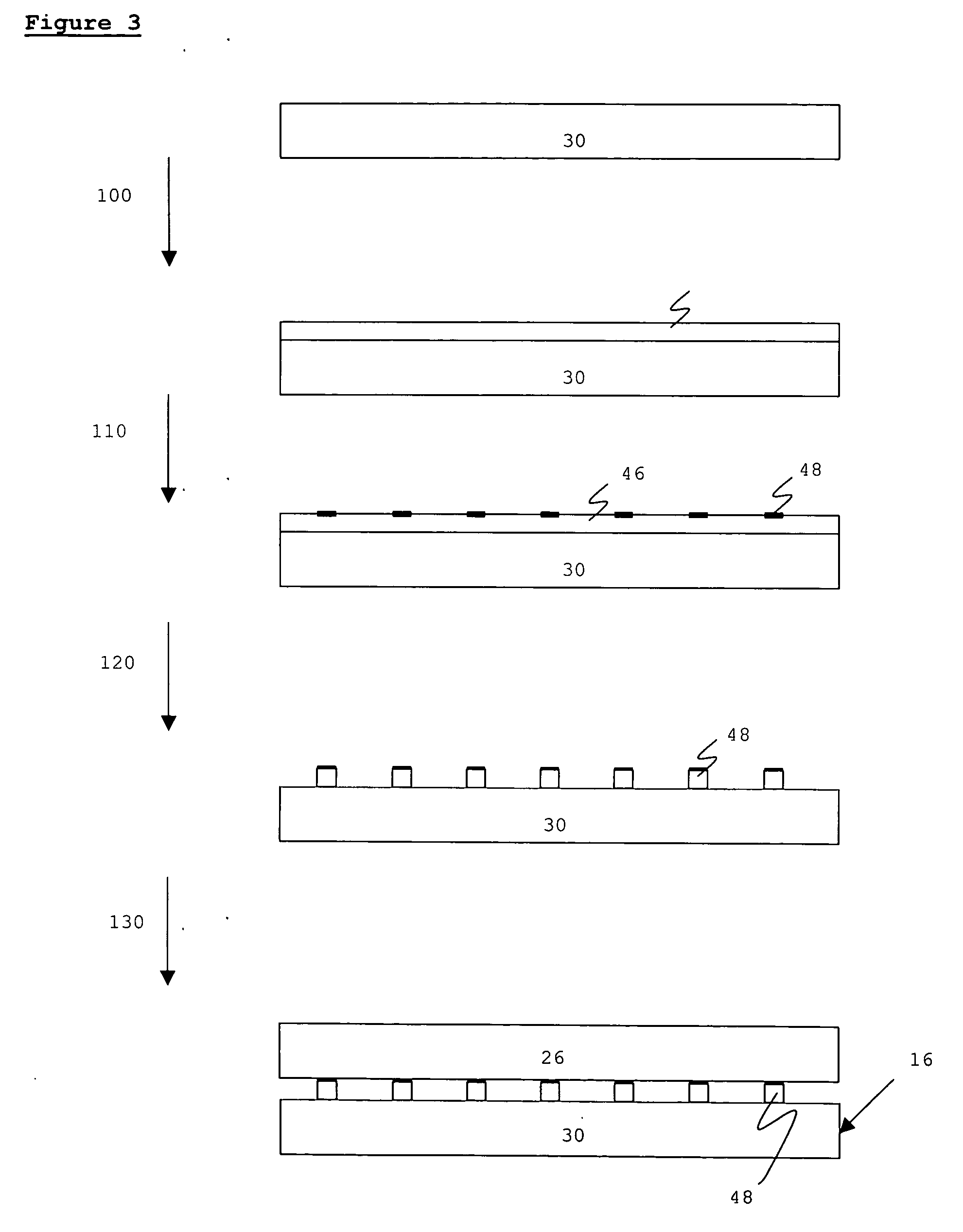

Cooling device using direct deposition of diode heat pump

InactiveUS20070053394A1Extend your lifeImprove reliabilityEnergy efficient heating/coolingSemiconductor/solid-state device detailsEngineeringHeat pump

A diode heat pump is disclosed which may be deposited directly onto a processor unit using thin-film deposition techniques to achieve more efficient cooling. The diode heat pump is either formed in situ on the processor unit or attached to the processor unit after each unit has been manufactured. Further embodiments of diode heat pumps are also disclosed.

Owner:BOREALIS TECH LTD

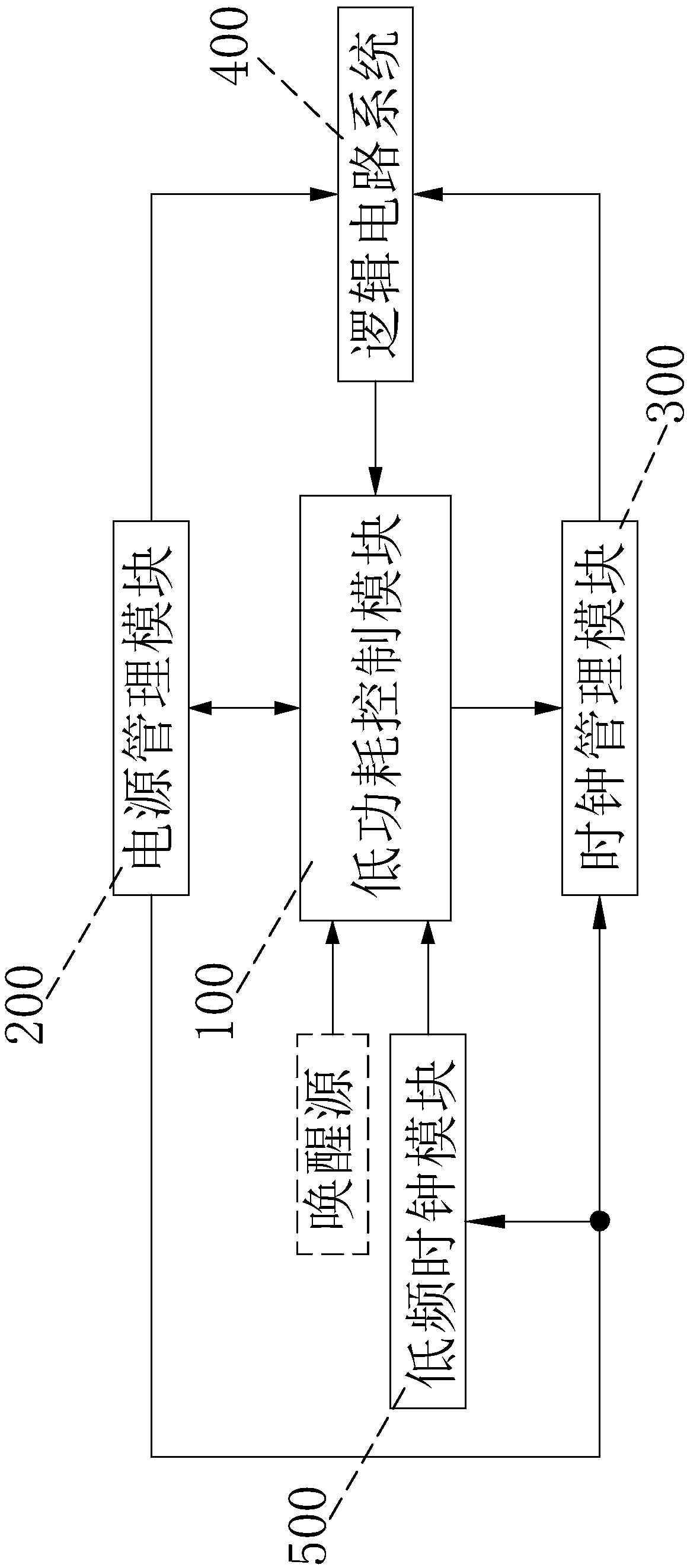

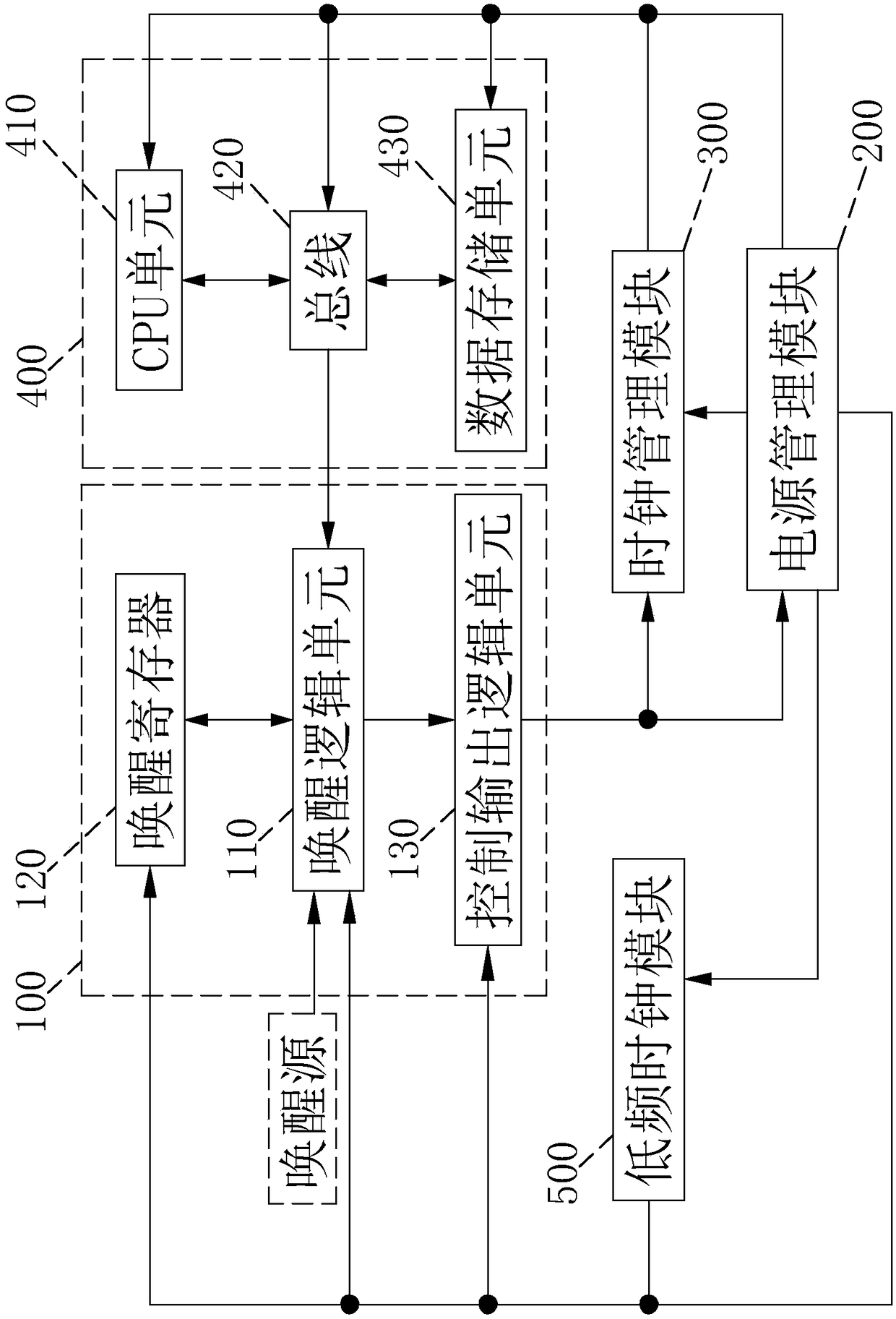

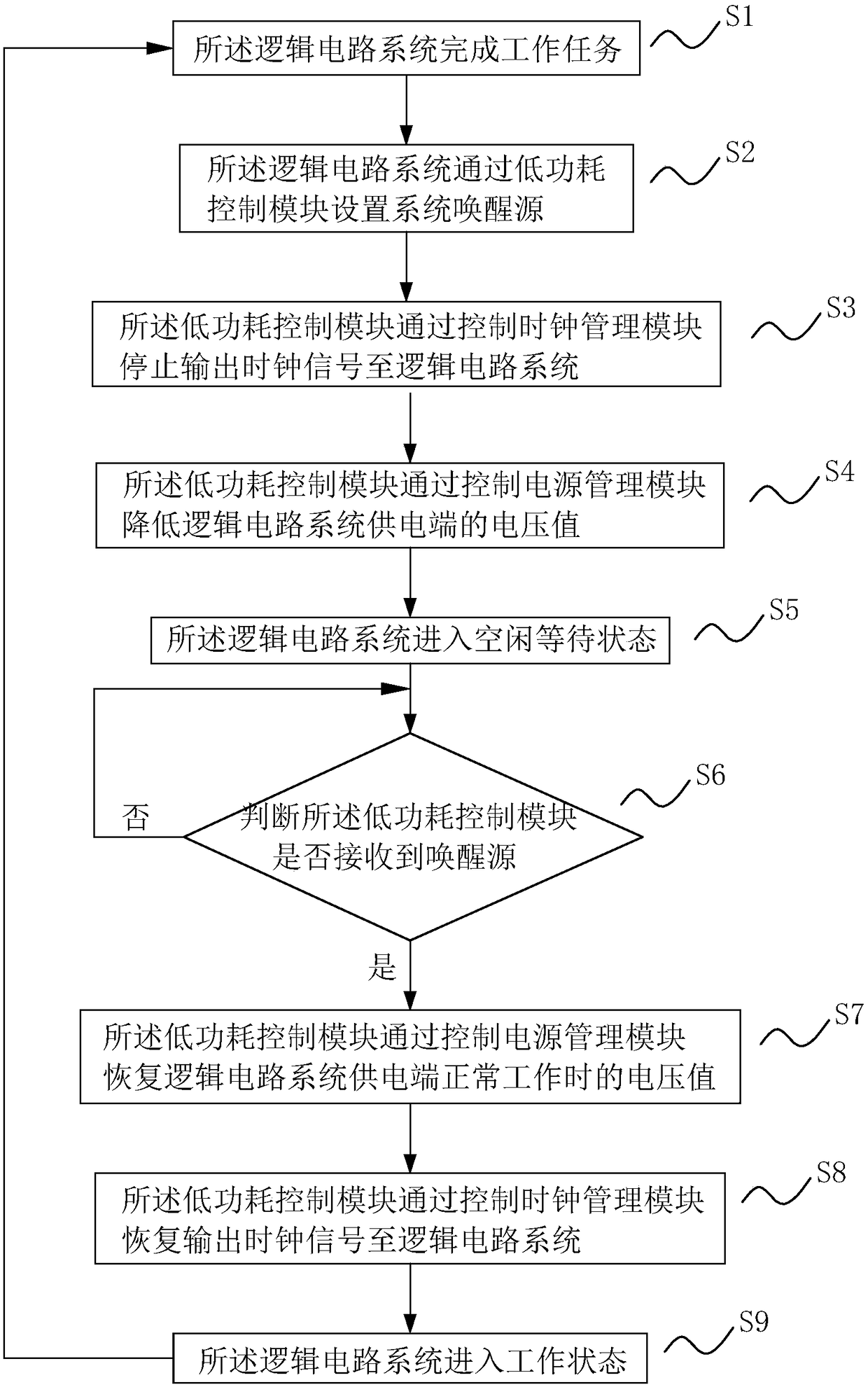

Small-size SoC ultra-low power consumption control circuit and method

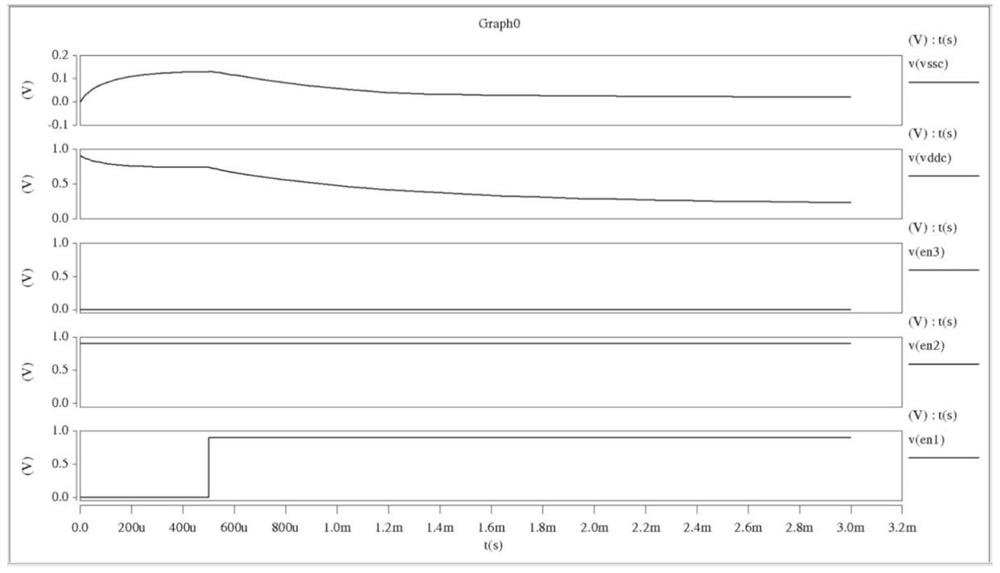

InactiveCN108089689AEliminate logic dynamic powerReduce leakage power consumptionPower supply for data processingUltra low powerLogical circuit

The invention discloses a small-size SoC ultra-low power consumption control circuit and method. The circuit structurally comprises a logic circuit system, a low power consumption control module a power management module, a clock management module and a low-frequency clock module. When an idle state is required, a voltage value at a power supply end of the logic circuit system is reduced, by the low power consumption control module on hardware, to only keep a data state in the logic circuit system and not support a lowest value of signal reversal, and meanwhile, a clock source of the logic circuit system is closed to eliminate logic dynamic power consumption and reduce electric leakage power consumption to be the lowest; and moreover, software is not required for storing a system operationstate, and when awakening is carried out, the software is not required to restore the scene and the next instruction of the system can be directly operated, so that the awakening speed is improved and the user experience is strengthened.

Owner:珠海慧联科技有限公司

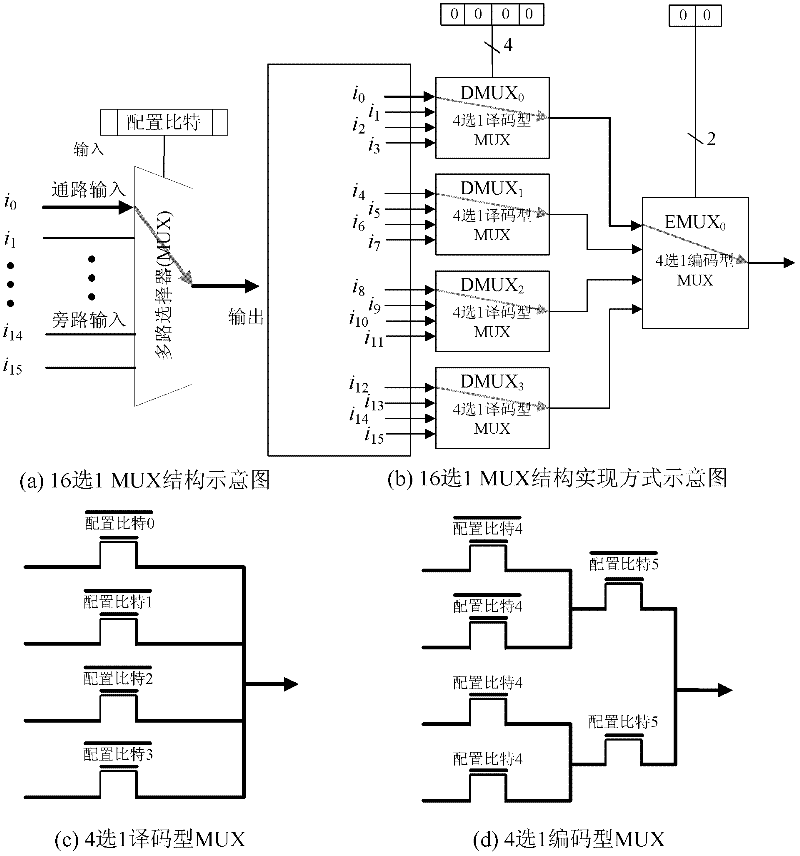

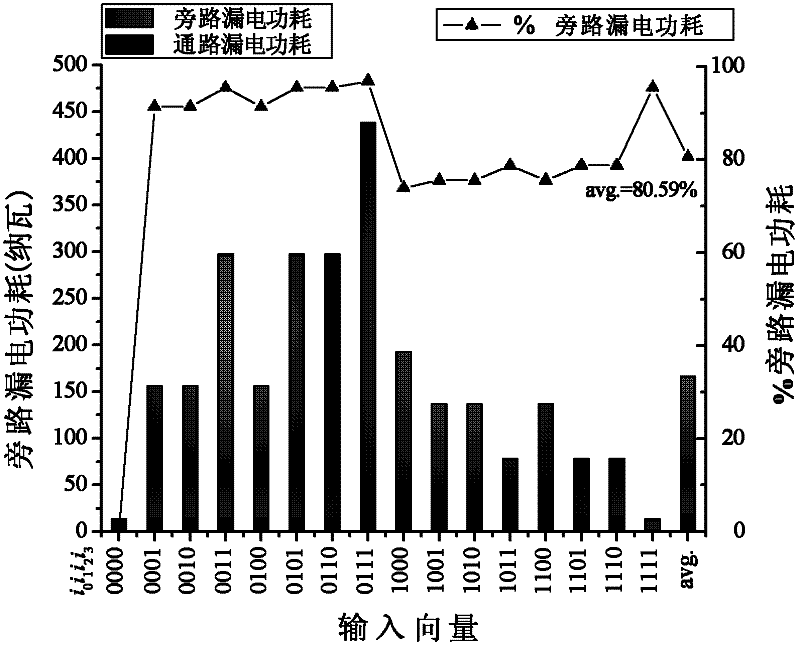

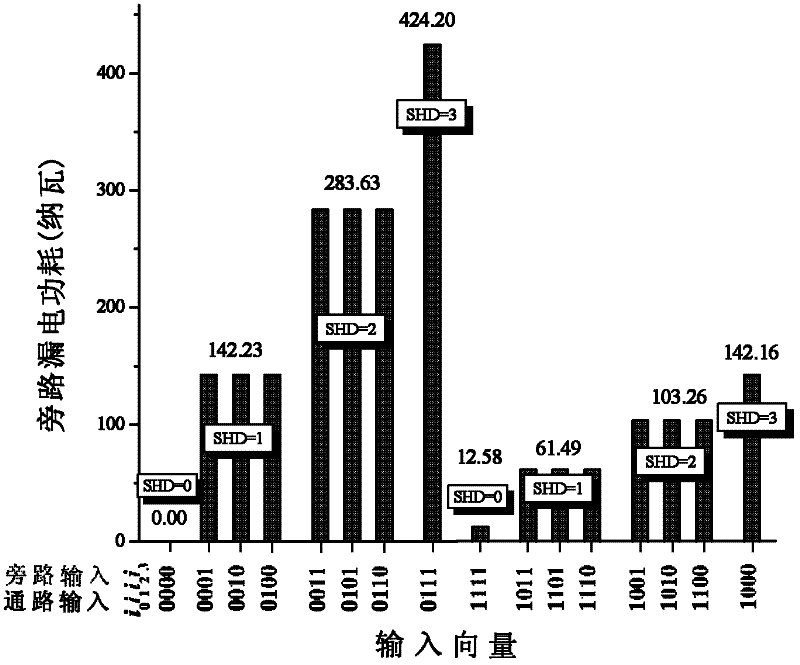

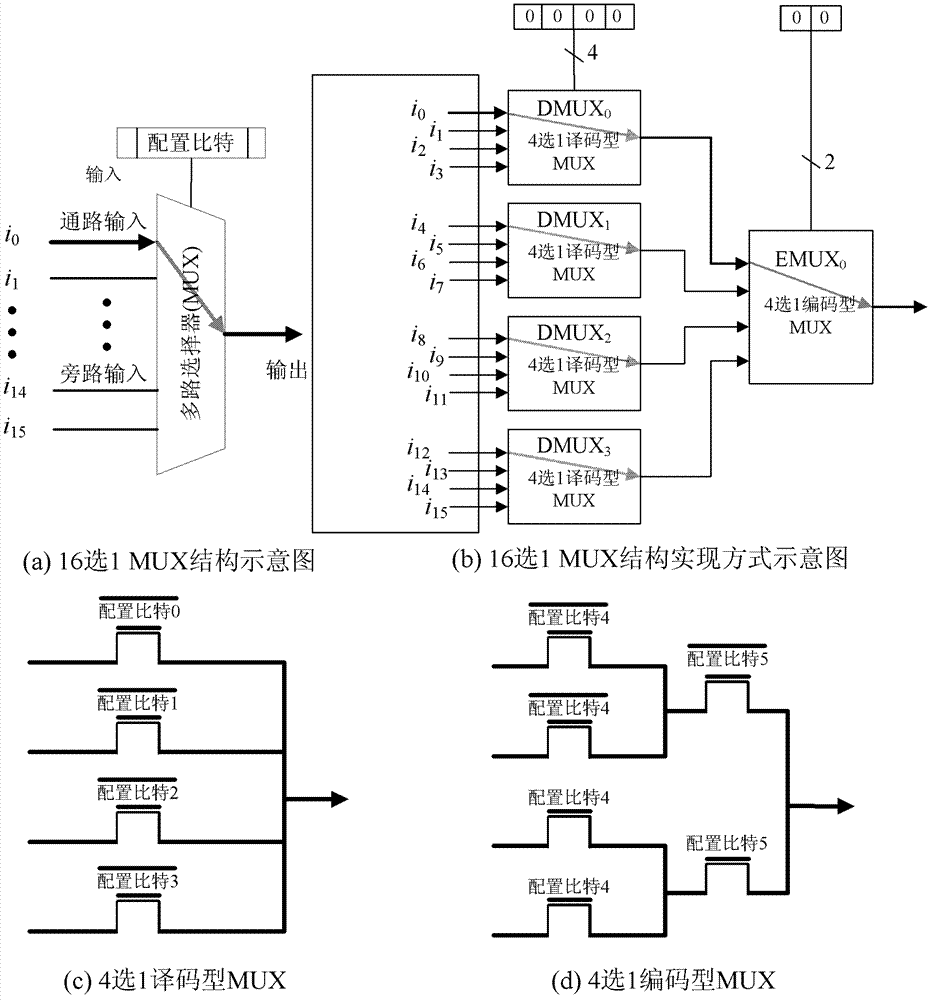

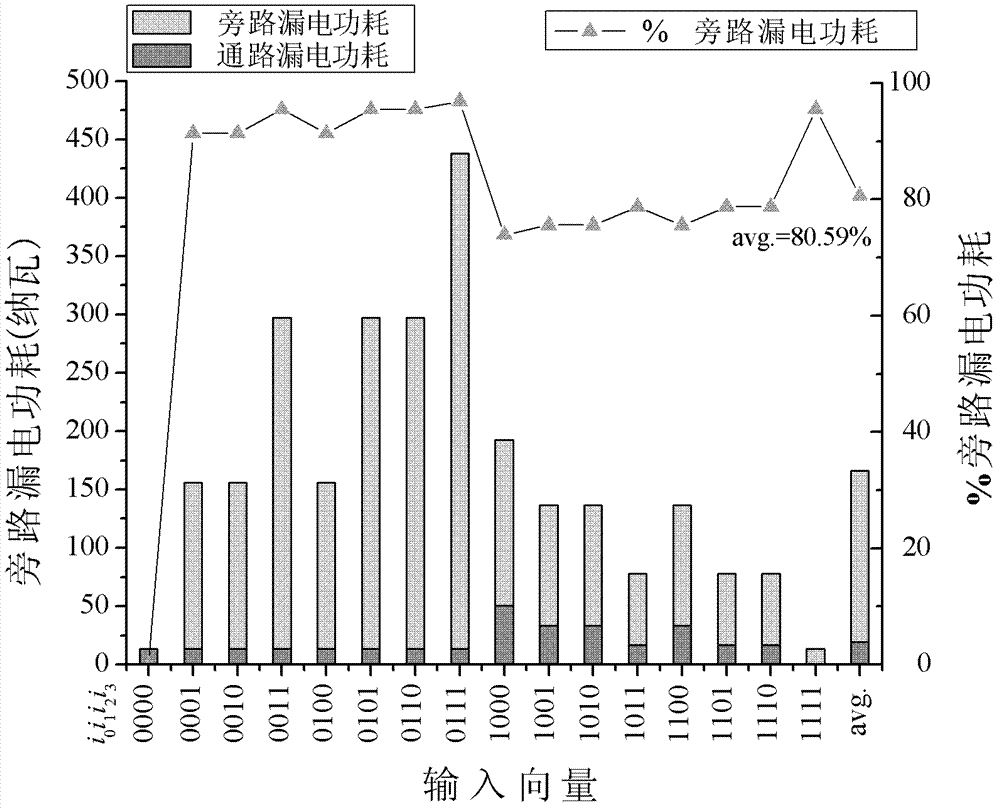

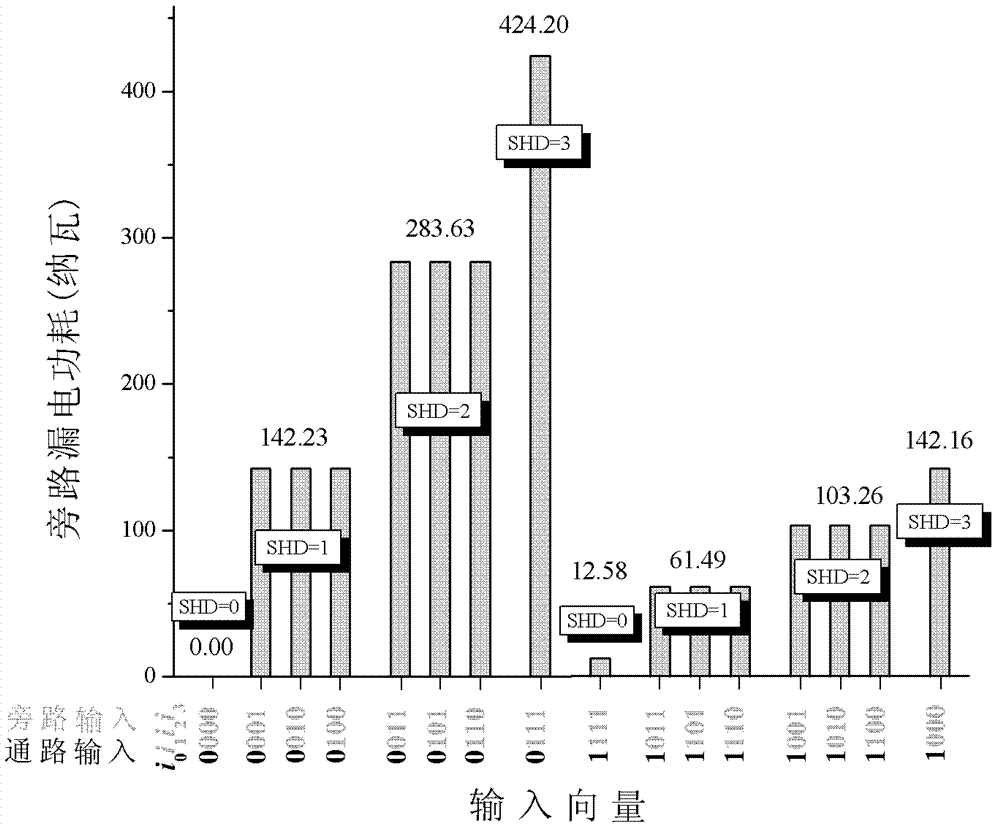

Low power consumption design method for SRAM (static random-access memory) type FPGA (field-programmable gate array)

ActiveCN102609563AReduce leakage power consumptionTiming impactSpecial data processing applicationsStatic random-access memoryLow-power electronics

The invention provides a low power consumption design method for a SRAM (static random-access memory) type FPGA (field-programmable gate array), which includes steps: firstly, building a leakage power information graph according to structure and circuit information of the FPGA; secondly, evaluating leakage power of each MUX during wiring phase to obtain the leakage power; thirdly, importing the leakage power to wiring cost function to lower circuit leakage power. By implementing low power consumption design during the wiring phase and comprehensively considering delay consumption, congestion consumption and leakage power consumption of the circuit during the wiring process, timing performance of the circuit is hardly affected. By modifying circuit wiring manner to implement low power consumption design, the method is irrelevant with chip structure of the FPGA and suitable for current mainstream FPGA, processing of the FPGA chips is not affected and no extra area consumption is imported.

Owner:INST OF COMPUTING TECH CHINESE ACAD OF SCI

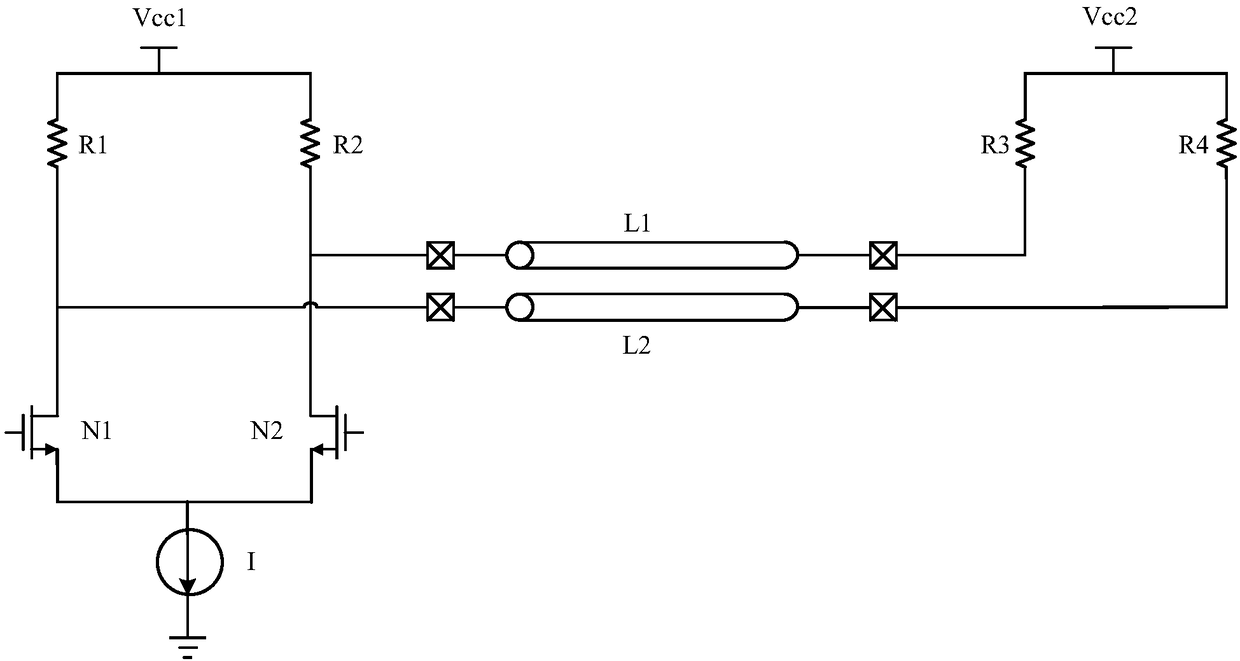

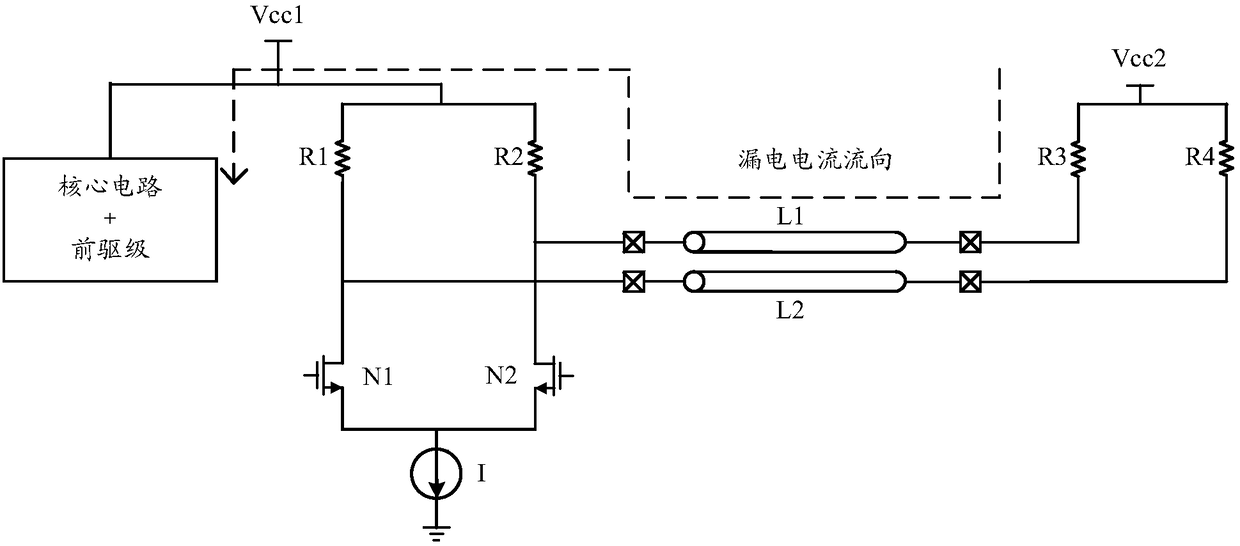

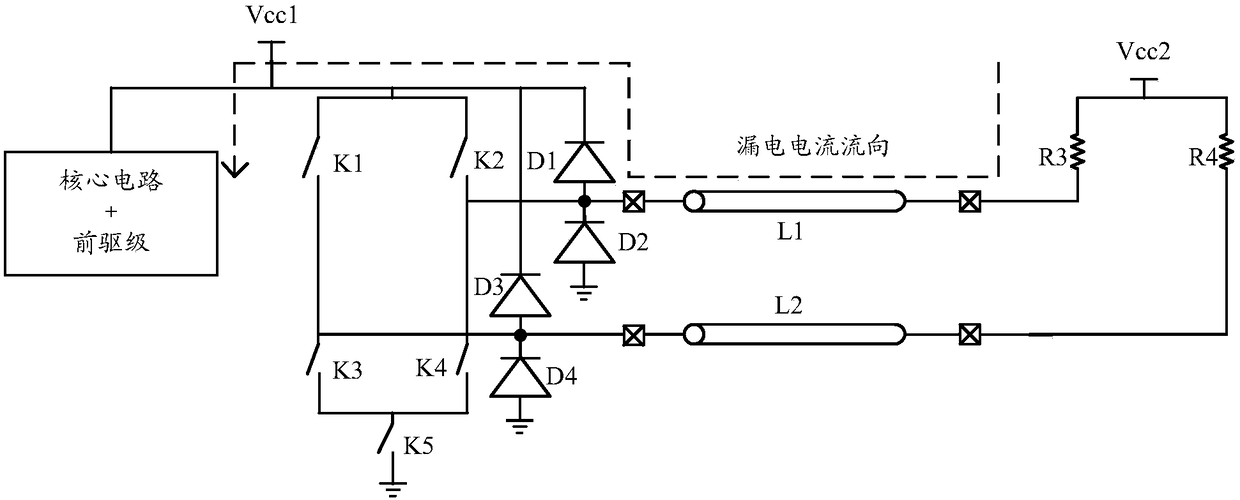

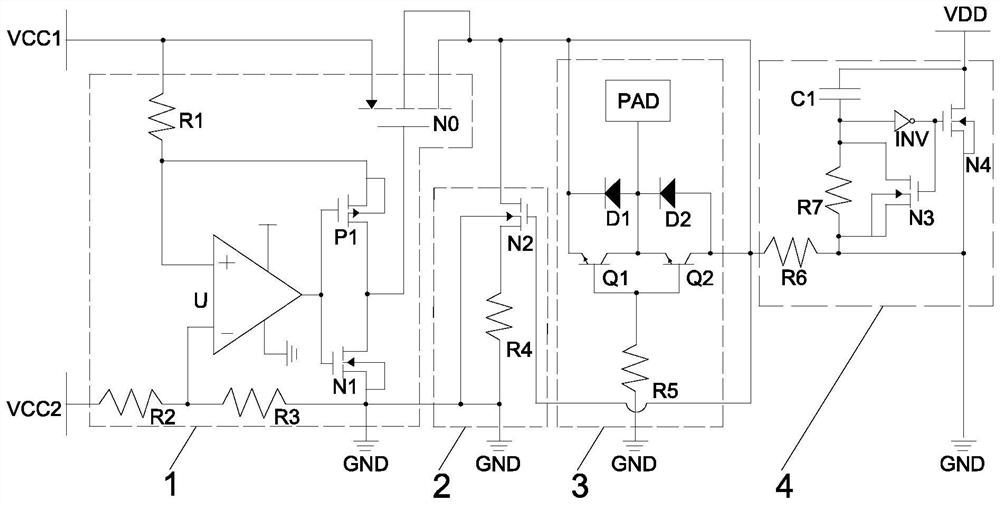

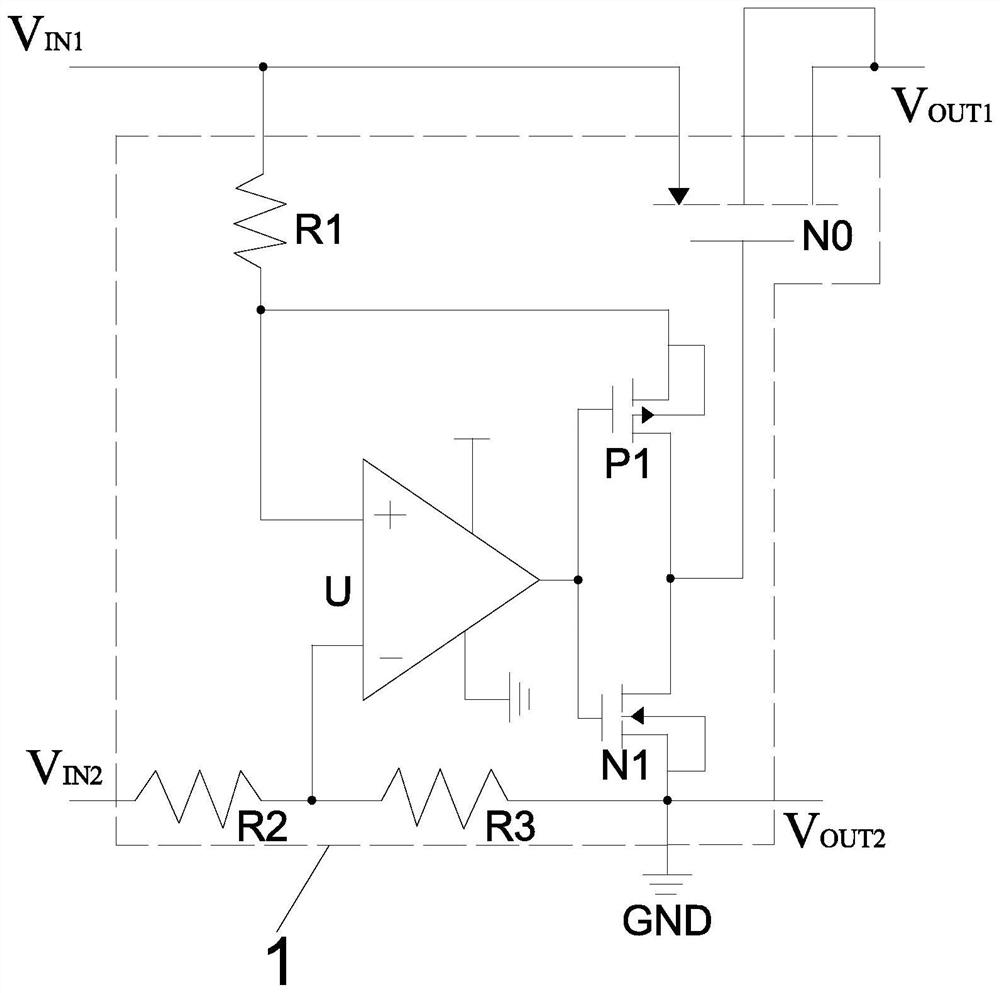

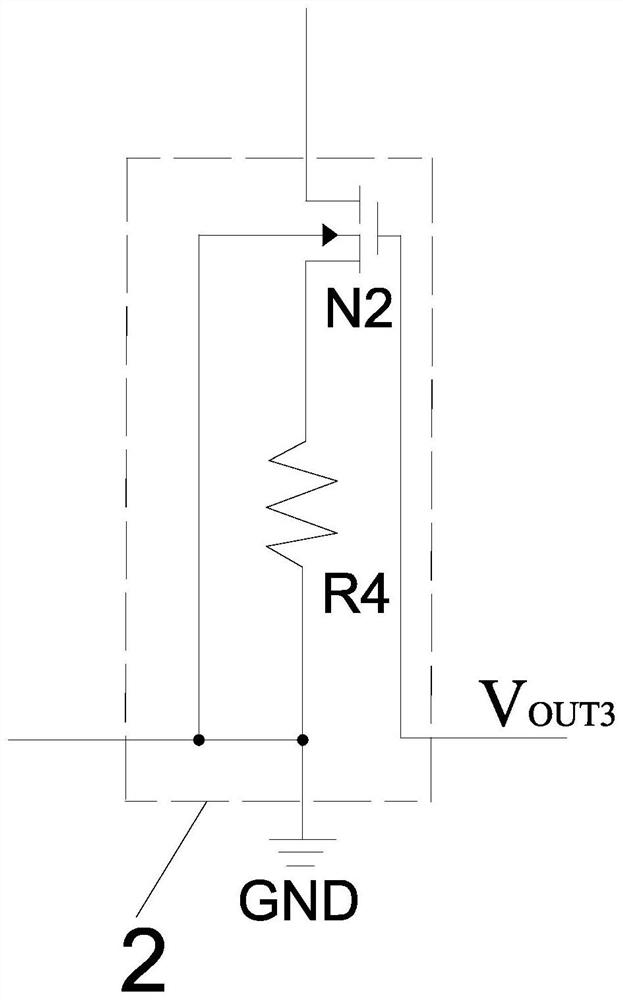

IO interface ESD leakage protection circuit

ActiveCN108199362APrevent inflowExtended service lifeEmergency protective arrangements for limiting excess voltage/currentControl switchLeakage power

The invention discloses an IO interface ESD leakage protection circuit comprising a control switch circuit used for controlling the on or off of the switch according to voltages on a sending terminal,a receiving terminal and an ESD diode node, wherein the first end of the control switch circuit is connected with a sending terminal power source VCC1, the second end of the same is connected with the cathode of the first diode of the ESD diode, and the third end of the same is connected with a receiving terminal power source VCC2 via a common terminal of the first diode and the second diode of the ESD diode and a terminating resistor, and the anode of the first diode is connected with the cathode of the second diode. The IO interface ESD leakage protection circuit provided by the invention interpedently segments the power source of the ESD diode, so that the controllable switch can be turned off when ensuring that the sending terminal is out of power, so as to prevent leakage current from flowing into a main power rail, the discharging path passing through the ESD diode is disconnected, the unnecessary leakage power consumption is reduced, and the service life of the IO chip is improved.

Owner:LONTIUM SEMICON CORP

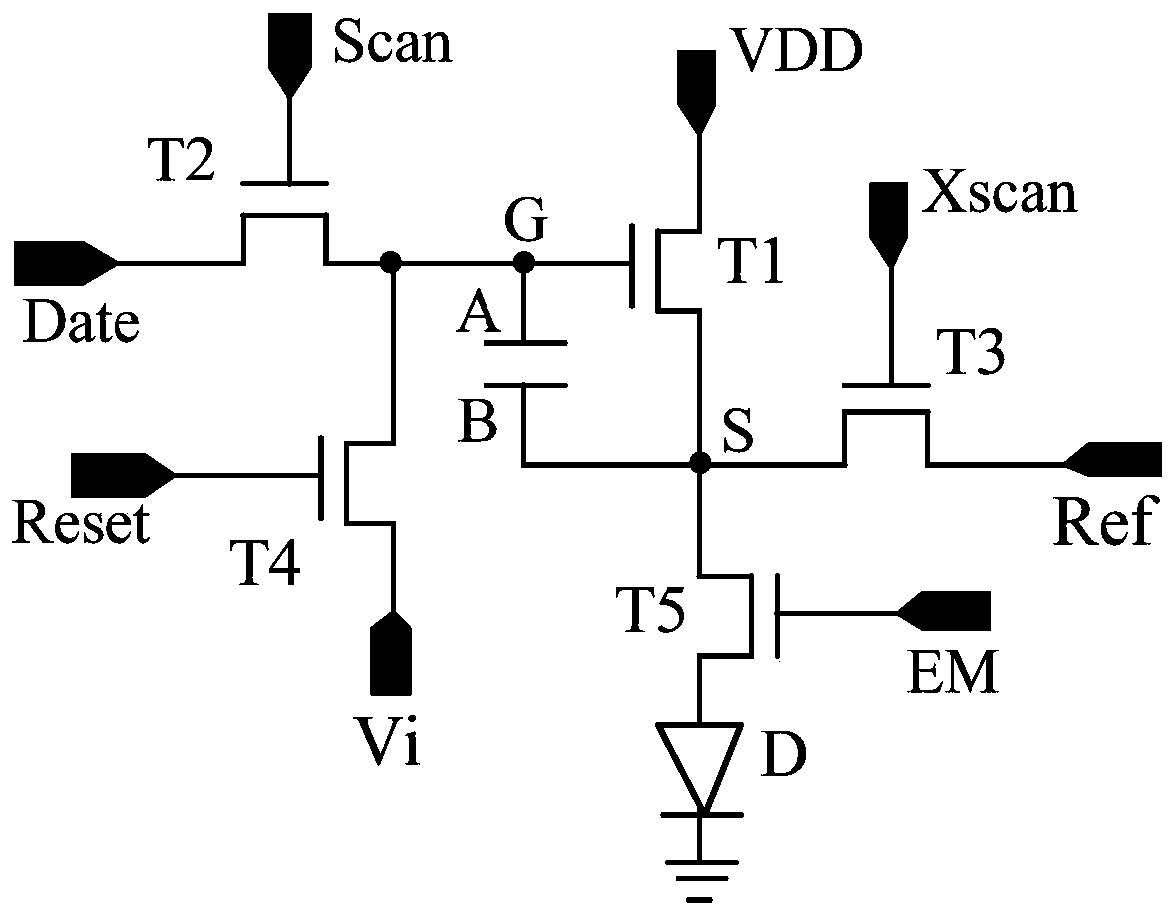

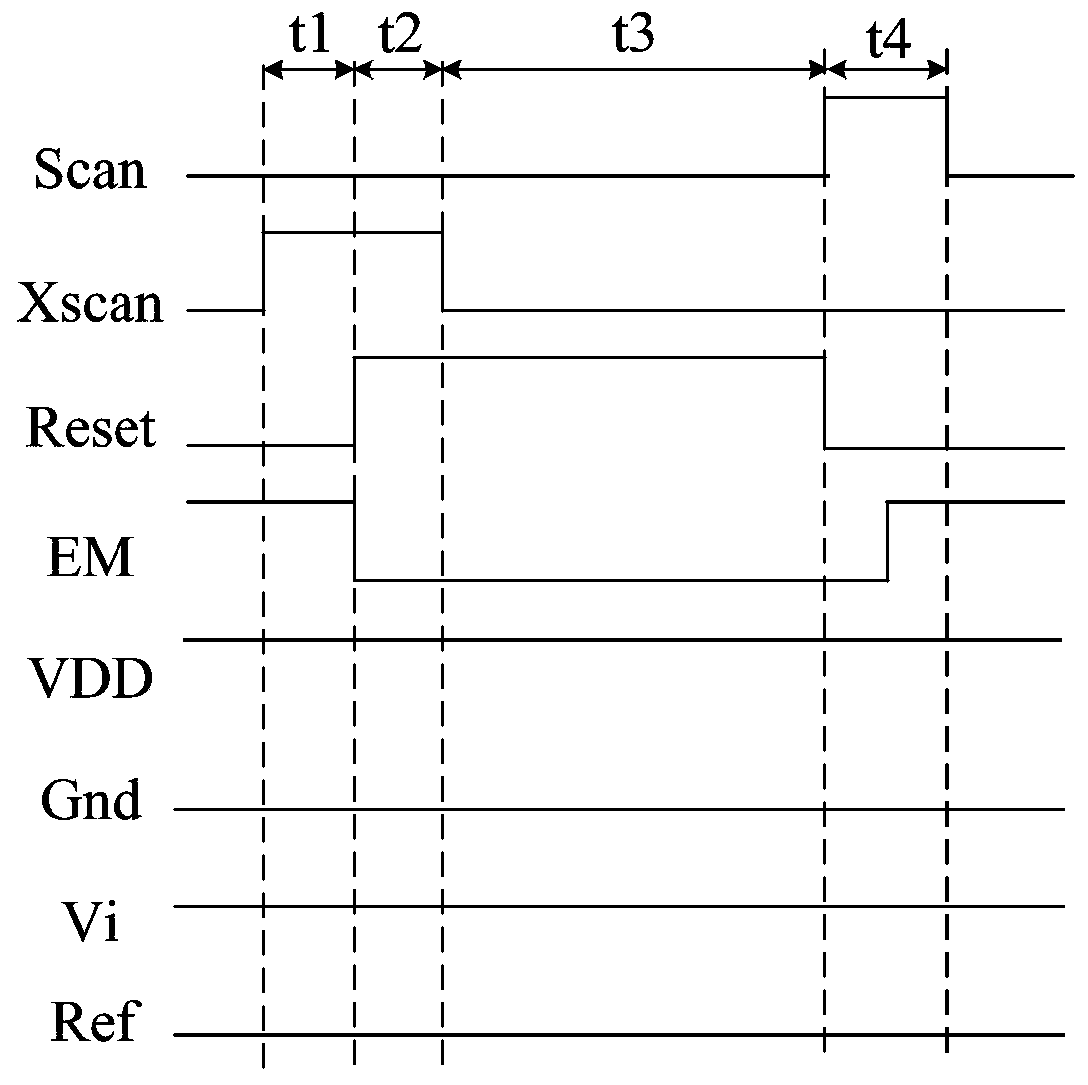

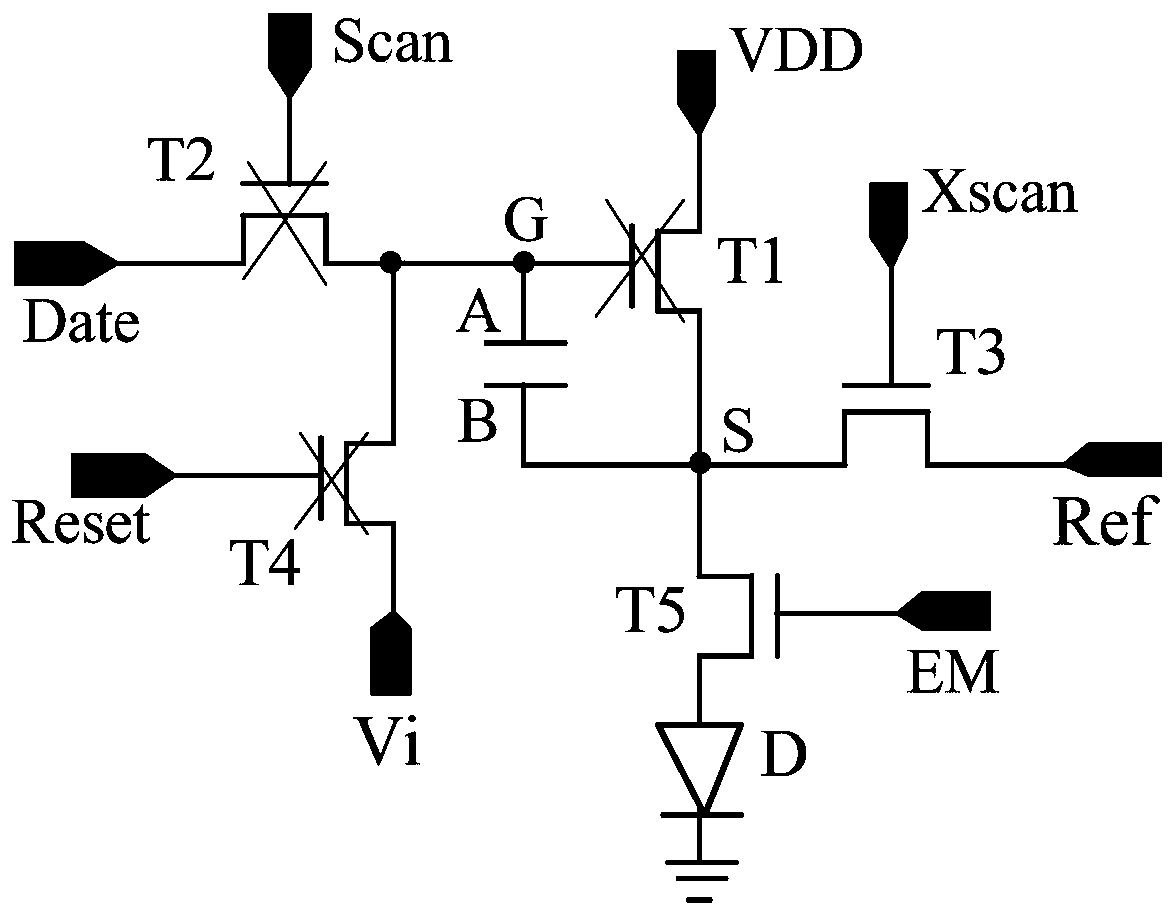

Pixel driving circuit and display panel

InactiveCN111261109AHigh compensation accuracyReduce leakage power consumptionStatic indicating devicesHemt circuitsComputer science

According to a pixel driving circuit and a display panel provided by the invention, the pixel driving circuit of a 5T1C structure is adopted to effectively compensate the threshold voltage of a driving transistor in each pixel, so that the electric leakage power consumption of the pixel driving circuit during threshold voltage extraction can be effectively reduced, and the compensation precision of the pixel driving circuit is further improved.

Owner:SHENZHEN CHINA STAR OPTOELECTRONICS SEMICON DISPLAY TECH CO LTD

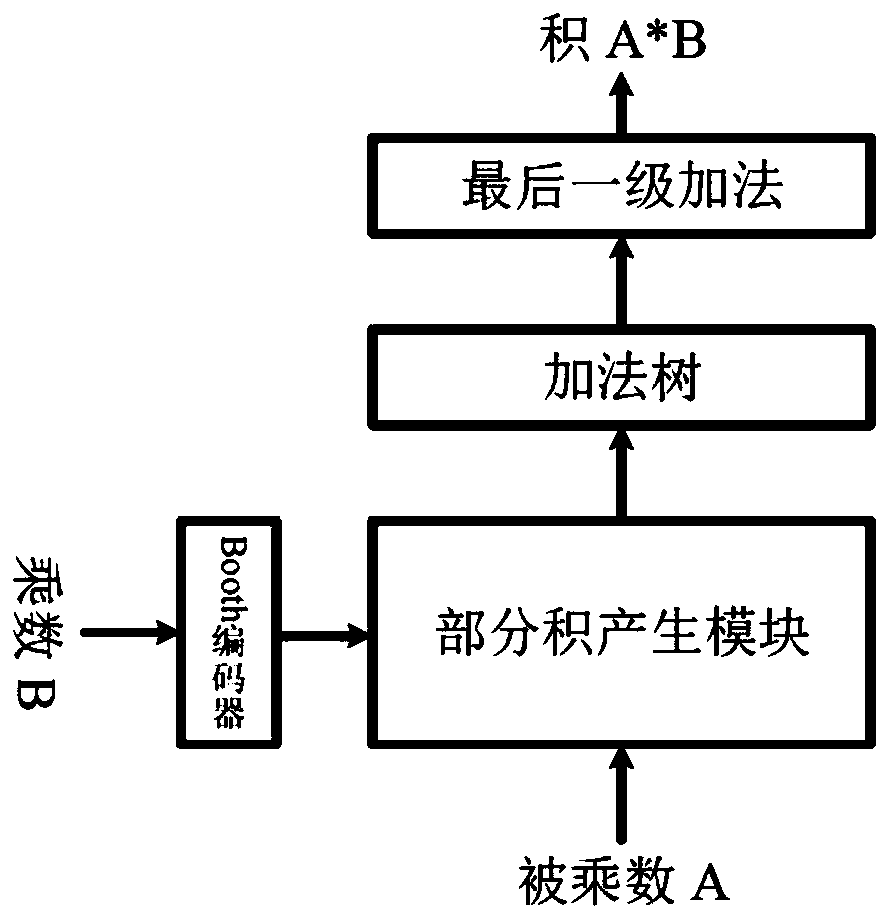

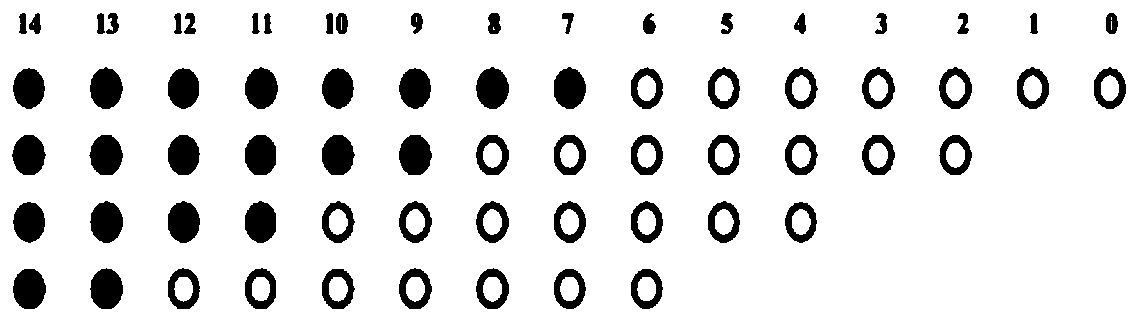

Nonvolatile 8-bit Booth multiplier based on RRAM

ActiveCN110196709AImprove storage densityReduce power consumptionDigital data processing detailsDigital storageElectricityBinary multiplier

The invention discloses a nonvolatile 8-bit Booth multiplier based on RRAM (Random Access Memory), which adopts Booth codes of RRAM storage multipliers and mainly comprises a partial product generation module, a Wallace addition tree and an addition chain. Compared with the prior art, the nonvolatile 8-bit Booth multiplier based on the RRAM is improved in speed, power consumption and area. The multiplier has the advantages that the data density is higher; power consumption is low and area is small; read-write power consumption and electric leakage power consumption are low; the configuration information of the multiplier B is not lost after power failure; and the reliability and the electrifying speed are high. Since the multiplication is a basic arithmetic operation in a data intensive application, the multiplier of the present invention can be applied to a variety of types of computing systems.

Owner:ZHEJIANG UNIV

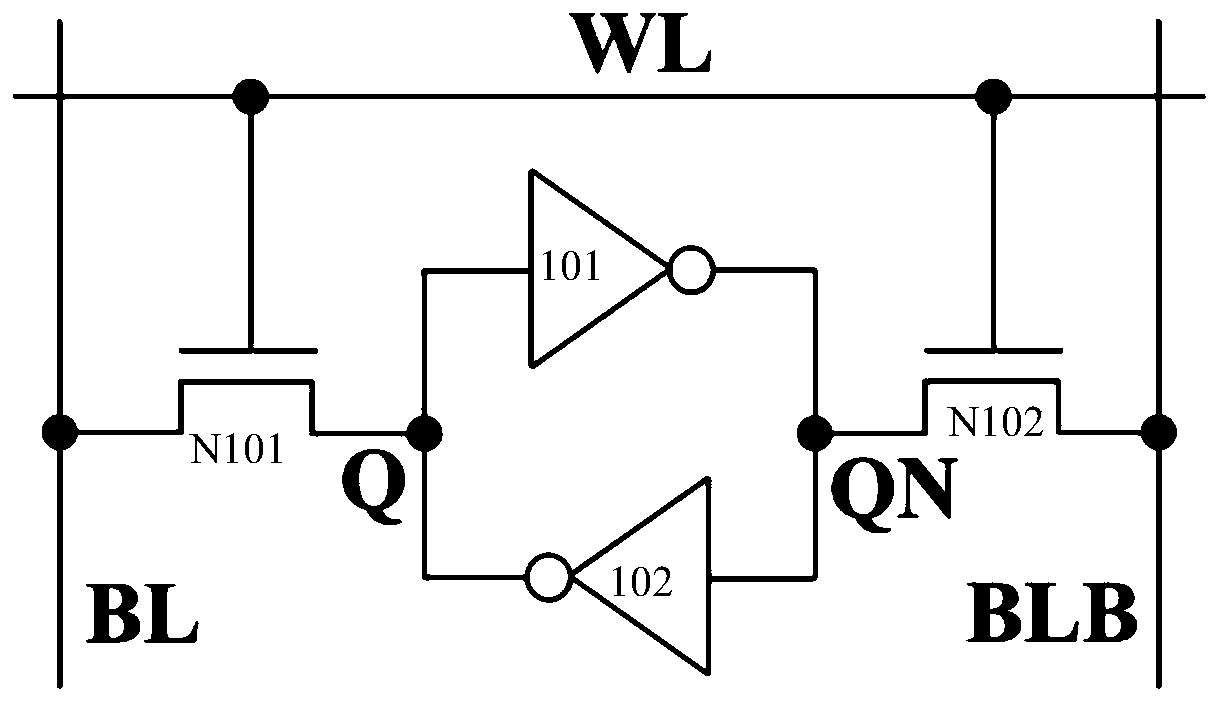

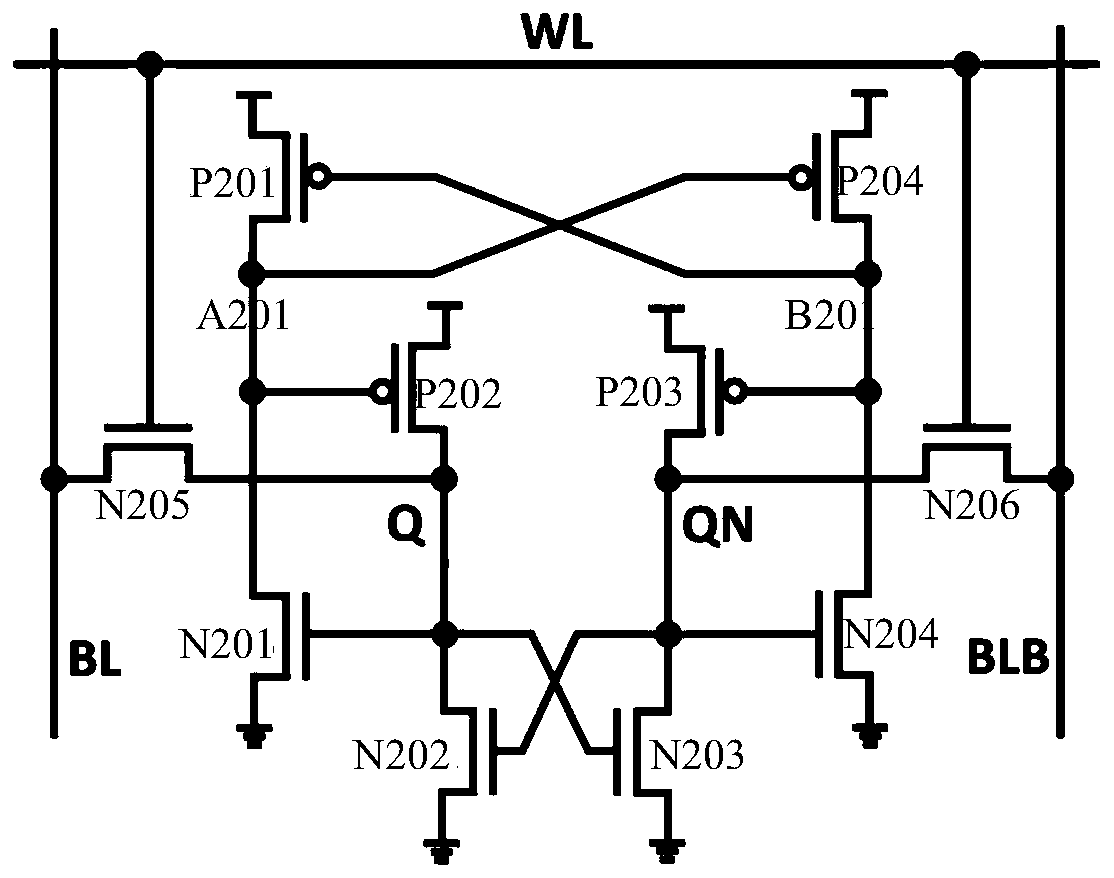

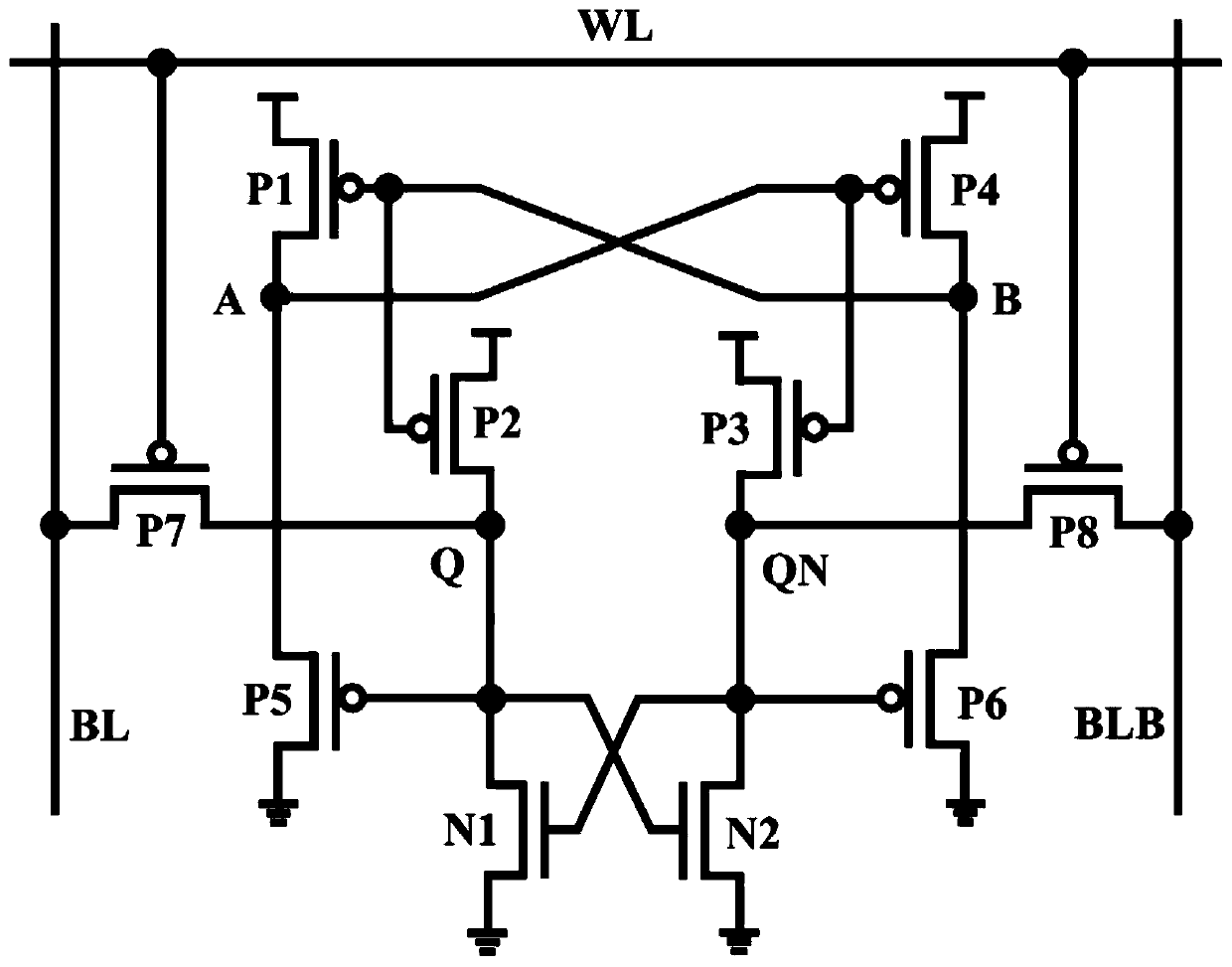

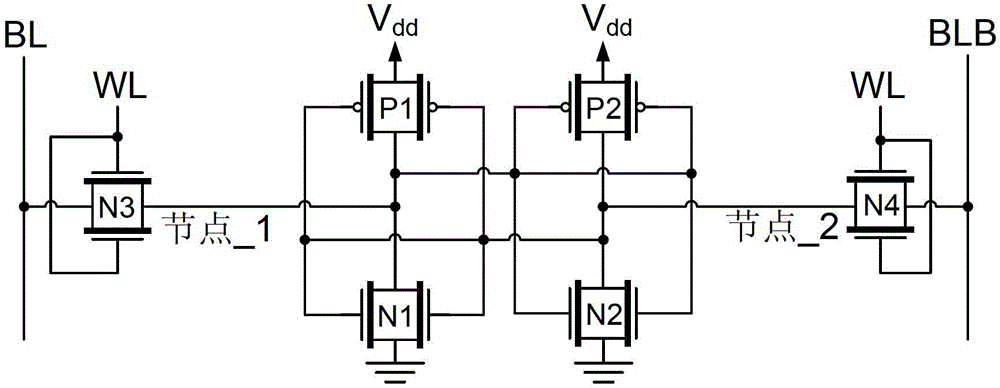

Memory cell structure of SRAM

ActiveCN109887535AImprove resistance to soft errorsEliminate distractionsDigital storageStatic random-access memoryHemt circuits

The invention discloses a memory cell structure of an SRAM (static random access memory), a main body structure consists of two NMOS (N-channel Metal Oxide Semiconductor) tubes and six PMOS (p-channelmetal oxide semiconductor) tubes, and the two transmission tubes are both PMOS (p-channel metal oxide semiconductor) tubes. The drain electrodes of the first NMOS tube and the second PMOS tube and the grid electrodes of the fifth PMOS tube and the second NMOS tube are connected with a Q node; the drain electrodes of the second NMOS tube and the third PMOS tube and the grid electrodes of the sixthPMOS tube and the first NMOS tube are connected with a QN node; the drain electrode of the first PMOS tube, the source electrode of the fifth PMOS tube, the grid electrode of the third PMOS tube andthe grid electrode of the fourth PMOS tube are all connected with a third node; the drain electrode of the fourth PMOS transistor, the source electrode of the sixth PMOS transistor and the grid electrodes of the first PMOS transistor and the second PMOS transistor are all connected with a fourth node; the source electrodes of the first to fourth PMOS tubes are connected to a power supply voltage,and the source electrodes of the first NMOS tube and the second NMOS tube and drain electrodes of the fifth PMOS tube and the sixth PMOS tube are grounded. The soft error resistance and the read static noise tolerance of the circuit can be improved, and the electric leakage power consumption can be reduced.

Owner:SHANGHAI HUAHONG GRACE SEMICON MFG CORP

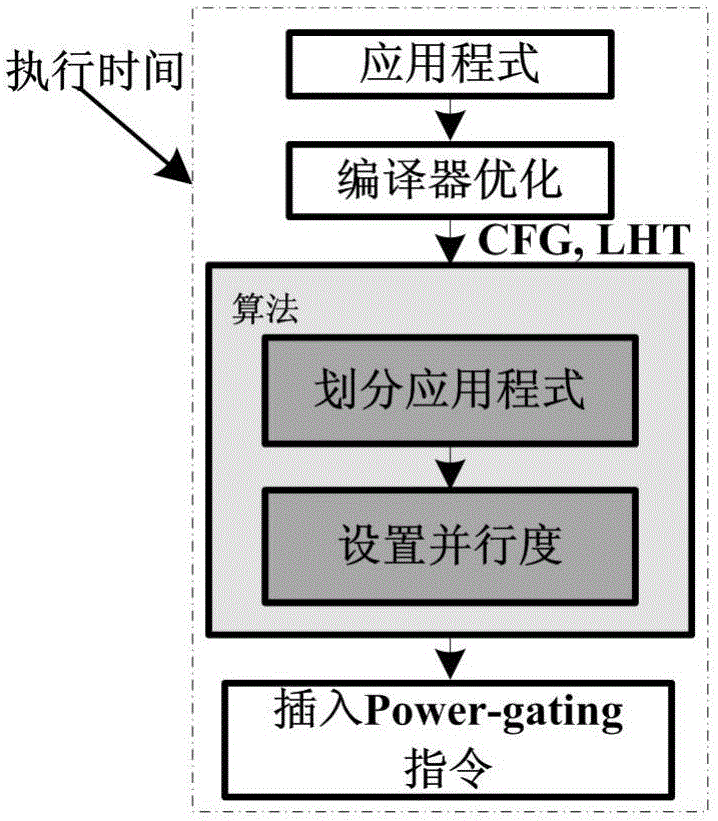

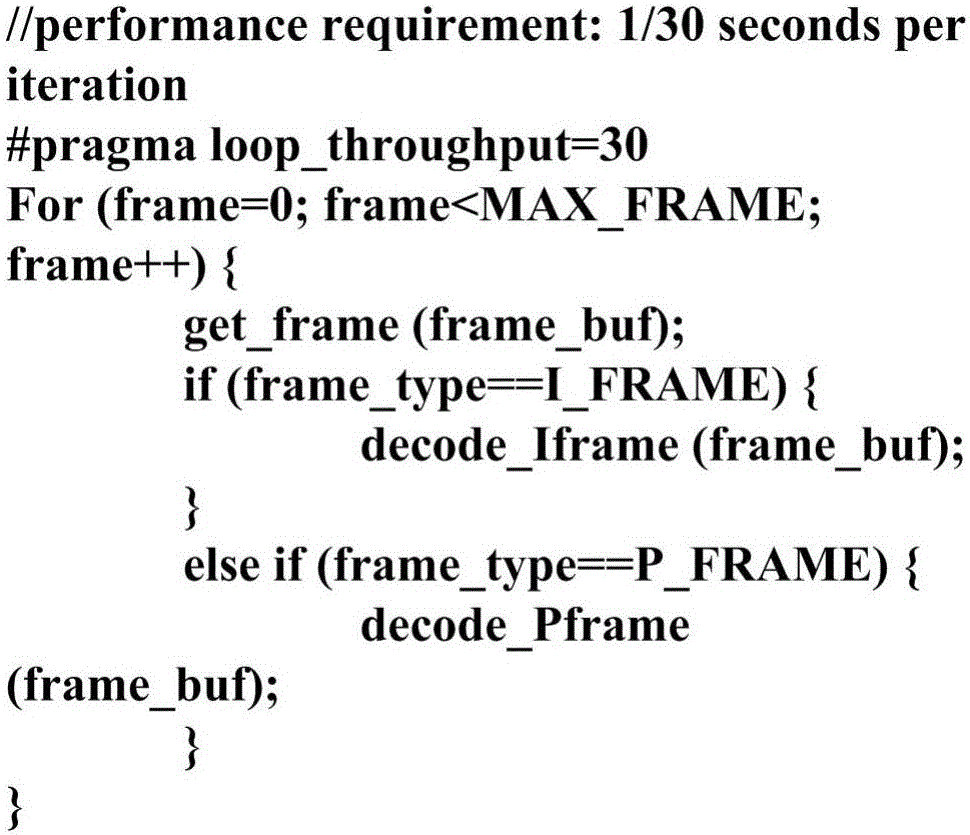

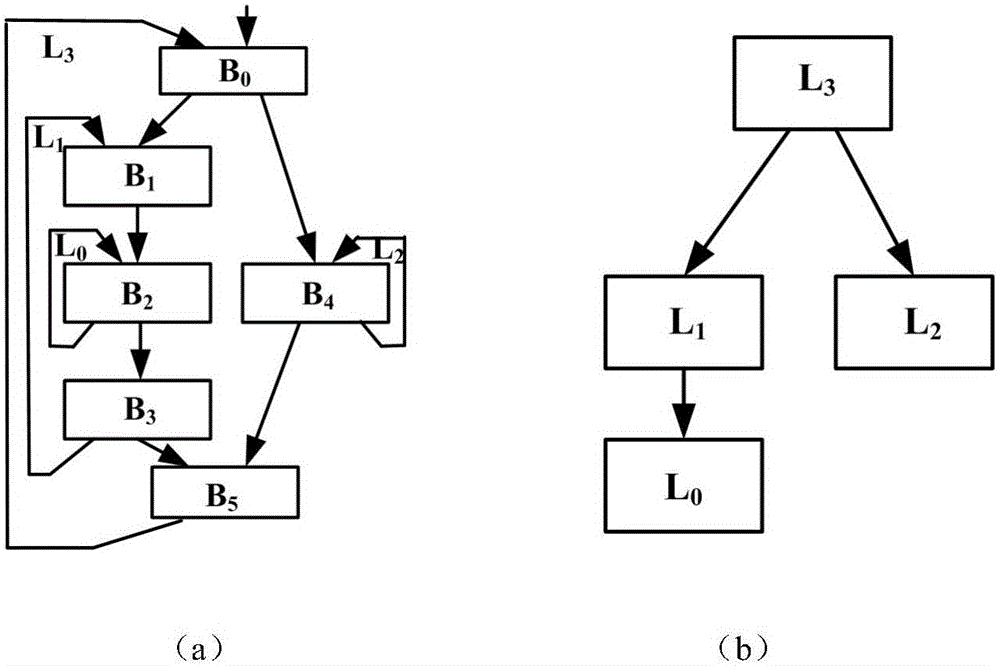

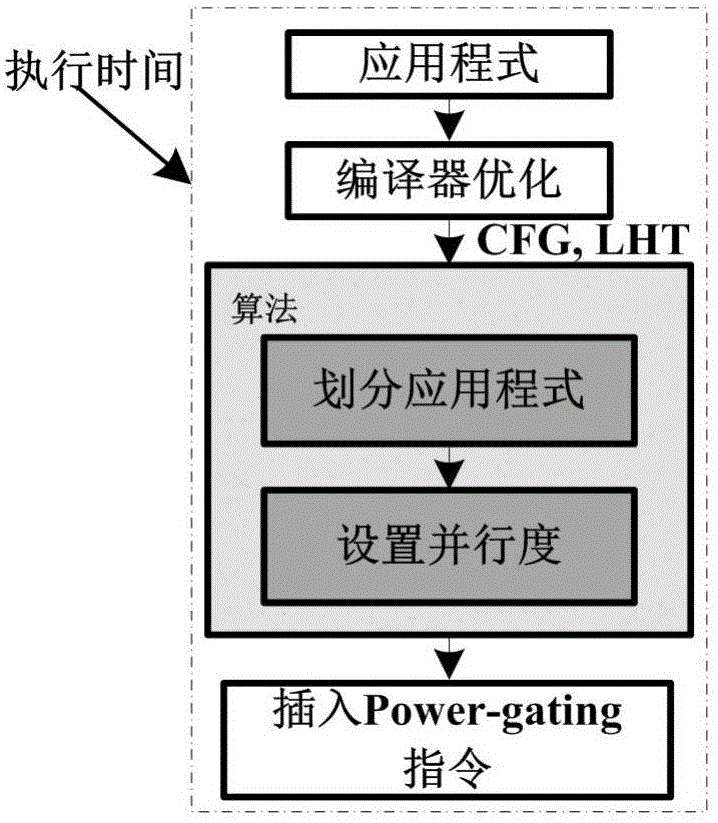

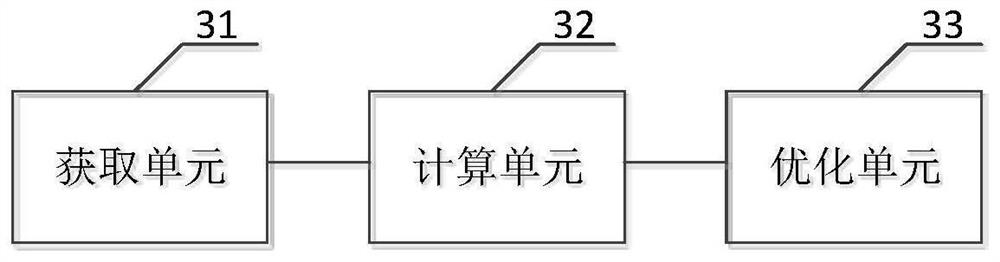

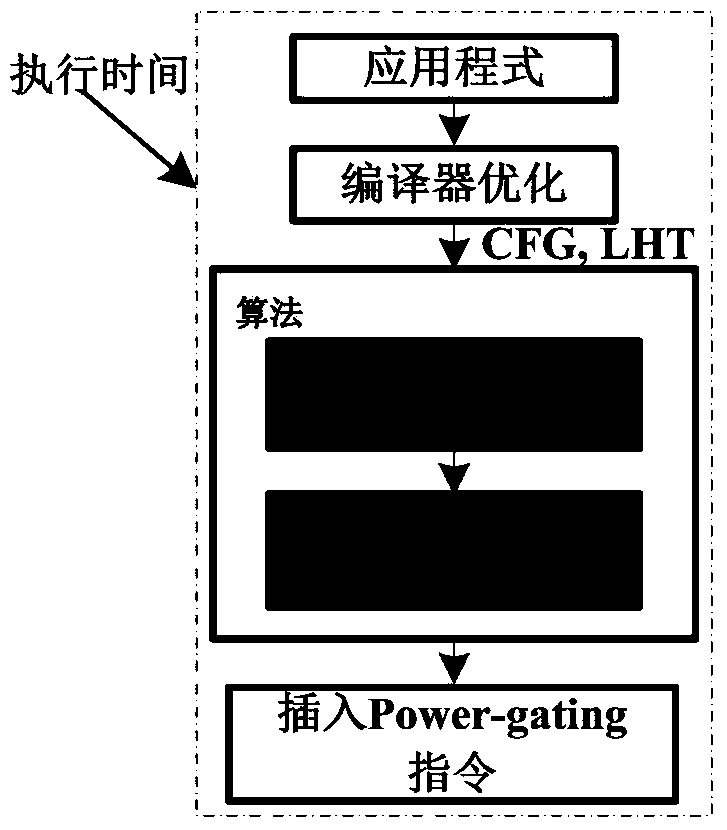

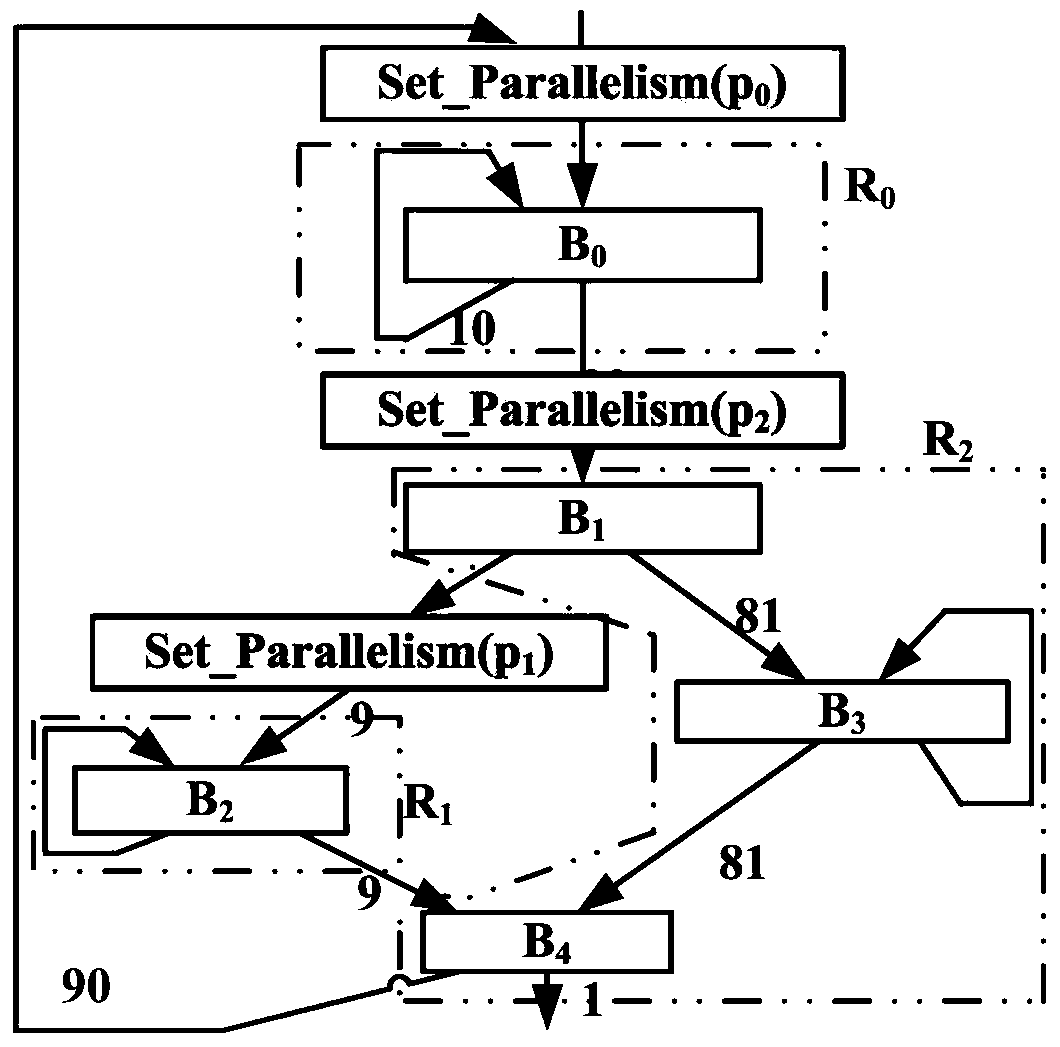

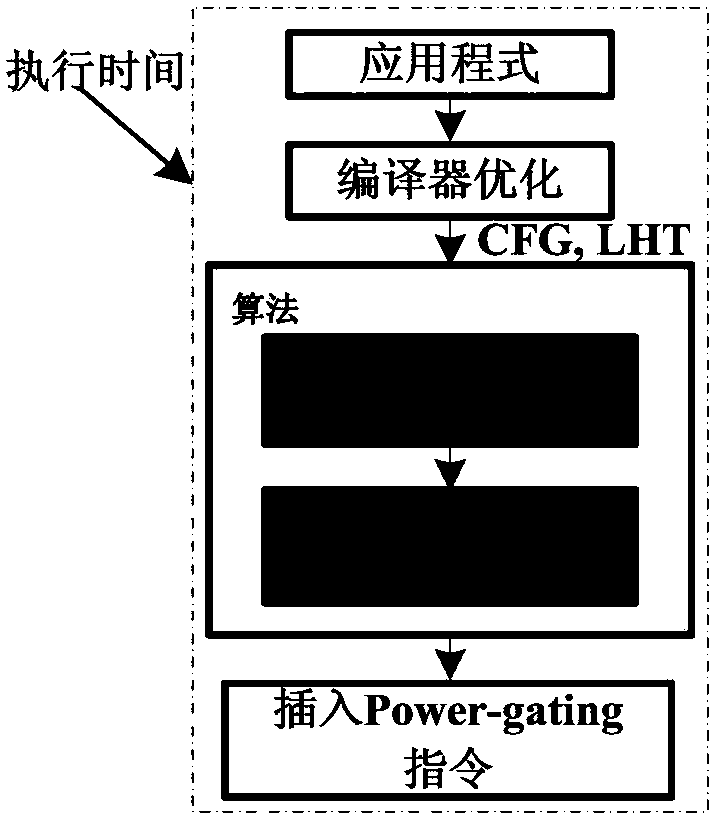

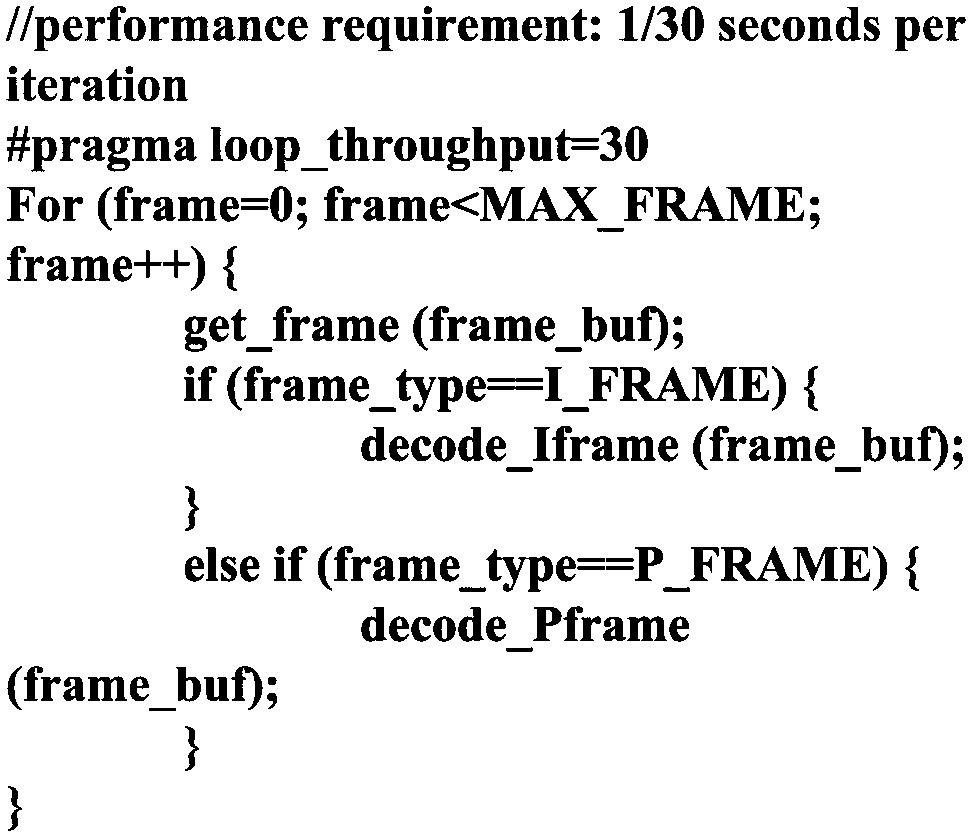

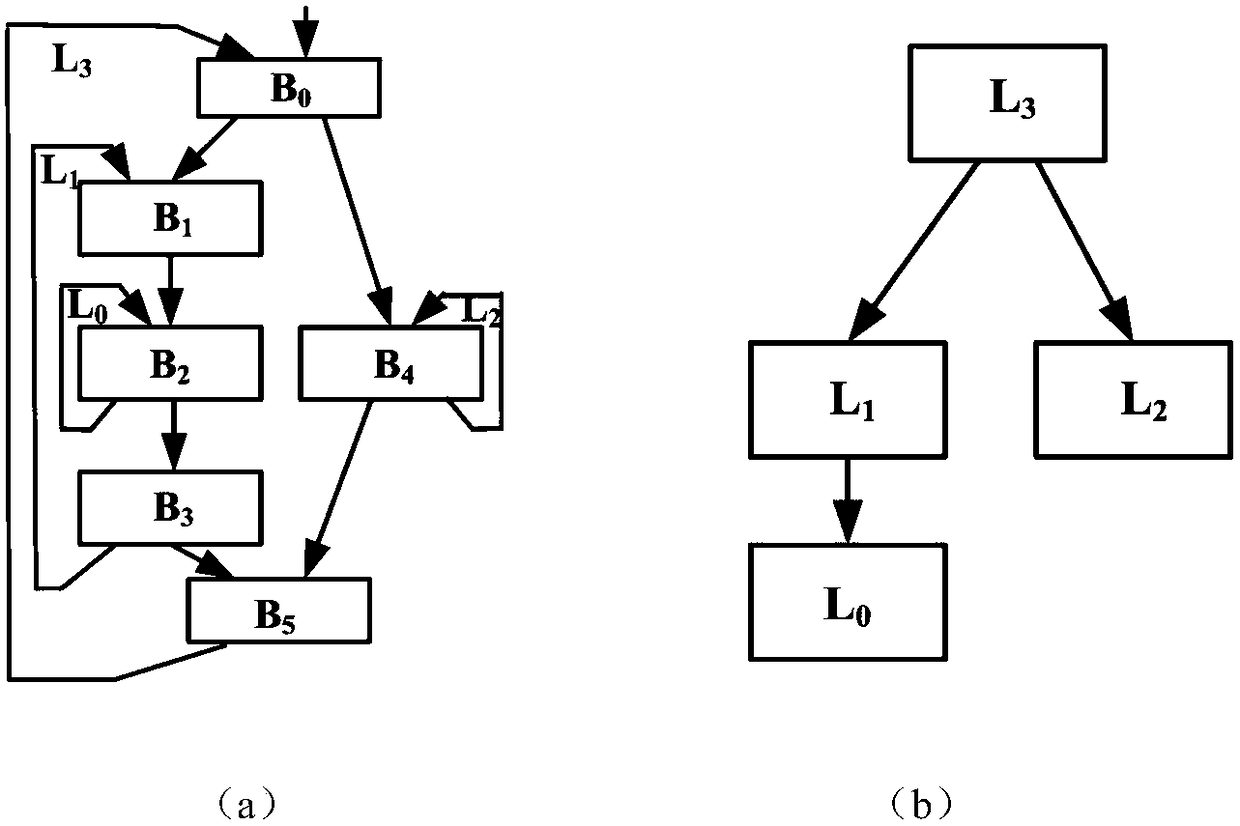

Low-power design optimization method for instruction-level parallel processor

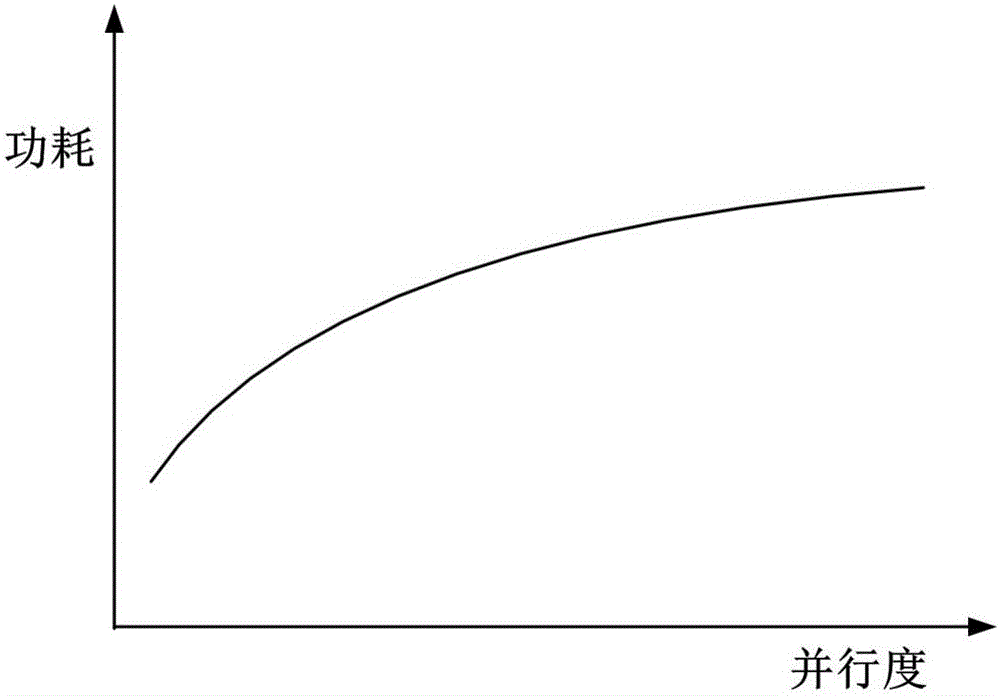

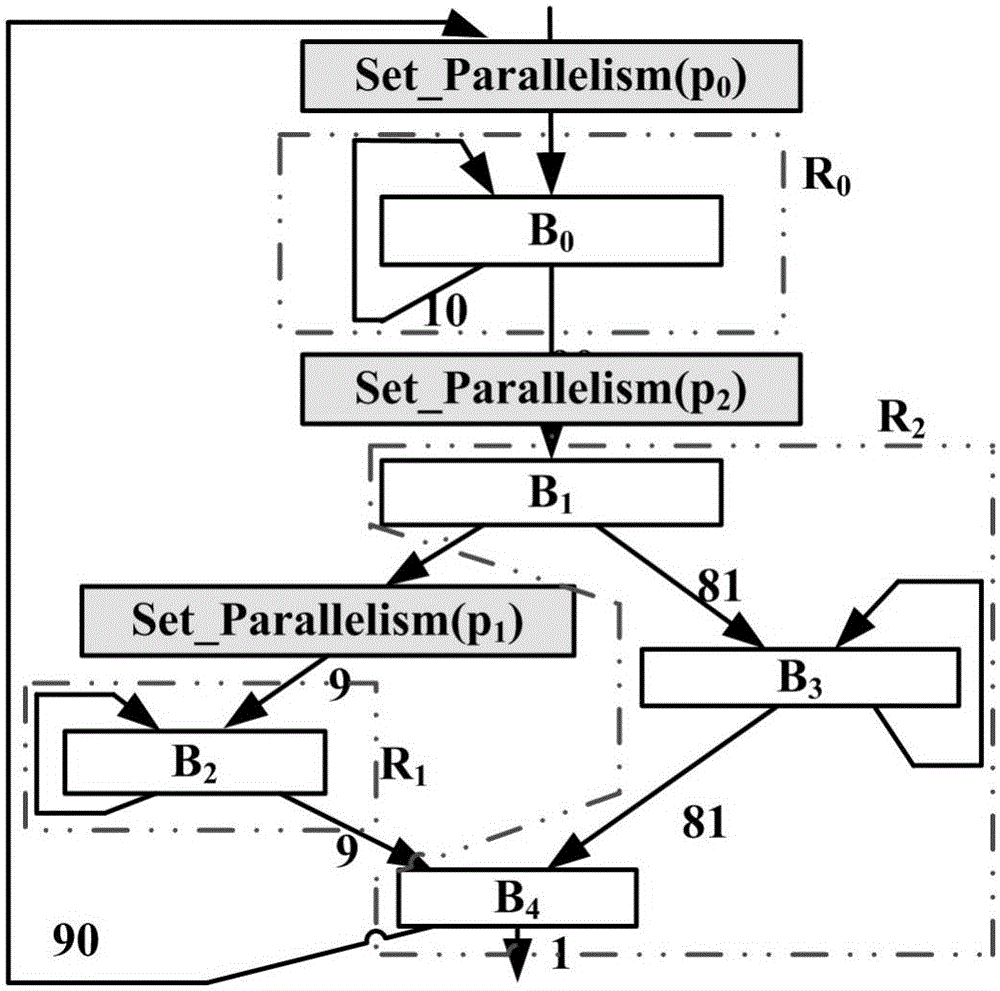

InactiveCN105929928AParallelism adjustments and changesReduce leakage power consumptionPower supply for data processingEnergy efficient computingLow-power electronicsWork Performances

The invention relates to a low-power design optimization method for an instruction-level parallel (ILP) processor. The method comprises the steps of analyzing a hardware resource and parallelism demand information of each part of an input application program by utilizing a compiler, and obtaining basic blocks of the application program as well as a control flow graph (CFG) and loop hierarchy trees (LHTs), which are formed by the basic blocks; identifying regional cores; expanding a region, combining the residual basic blocks in the region, finding out the regional cores directly connected with the residual basic blocks, comparing executive frequencies of edges connecting the regional cores, finding out the edge with the maximum executive frequency, and combining the basic block connected with the maximum edge in the regional cores until the residual basic blocks do not exist; and re-scheduling the application program, scheduling each region by using the set parallelism, inserting a power gating instruction before executing each region, and turning off idle hardware resources to reduce electric leakage power consumption. According to the method, the influence of the electric leakage power consumption on the working performance of the processor can be reduced and the utilization rate of the hardware resources in the ILP processor can be increased.

Owner:TIANJIN UNIV

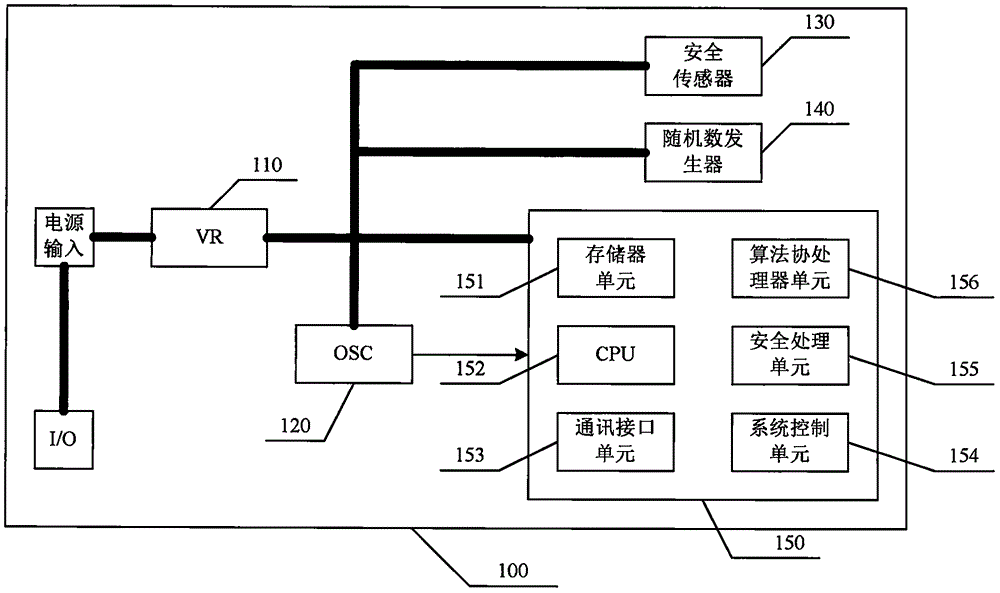

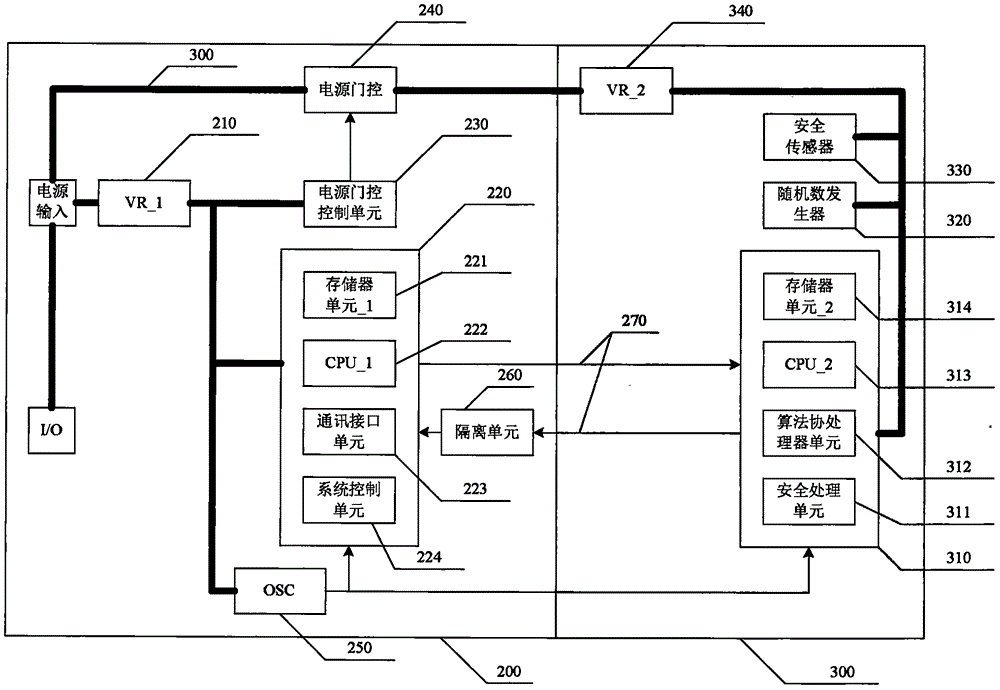

Low-electric-leakage bi-CPU core safe chip configuration

InactiveCN106066970AReduce overall power consumptionReduce power consumptionInternal/peripheral component protectionPower supply for data processingCommunication interfaceHigh complexity

The invention provides a low-electric-leakage bi-CPU core safe chip configuration, which realizes minimal safe physical isolation and static power consumption. The configuration employs two CPU subsystems, one of which is a low performance and low power dissipation logic gate count for processing communication interface and other non-security applications. The other CPU subsystem is a high-performance high-security CPU for providing complex and high performance cipher calculation, sensitive information processing and other high security applications. The high-performance CPU system is high in logic complexity, and a power supply is cut off by a gate control when a chip enters into a standby state to lower the integral electric leakage and power consumption of the chip.

Owner:BEIJING CEC HUADA ELECTRONIC DESIGN CO LTD

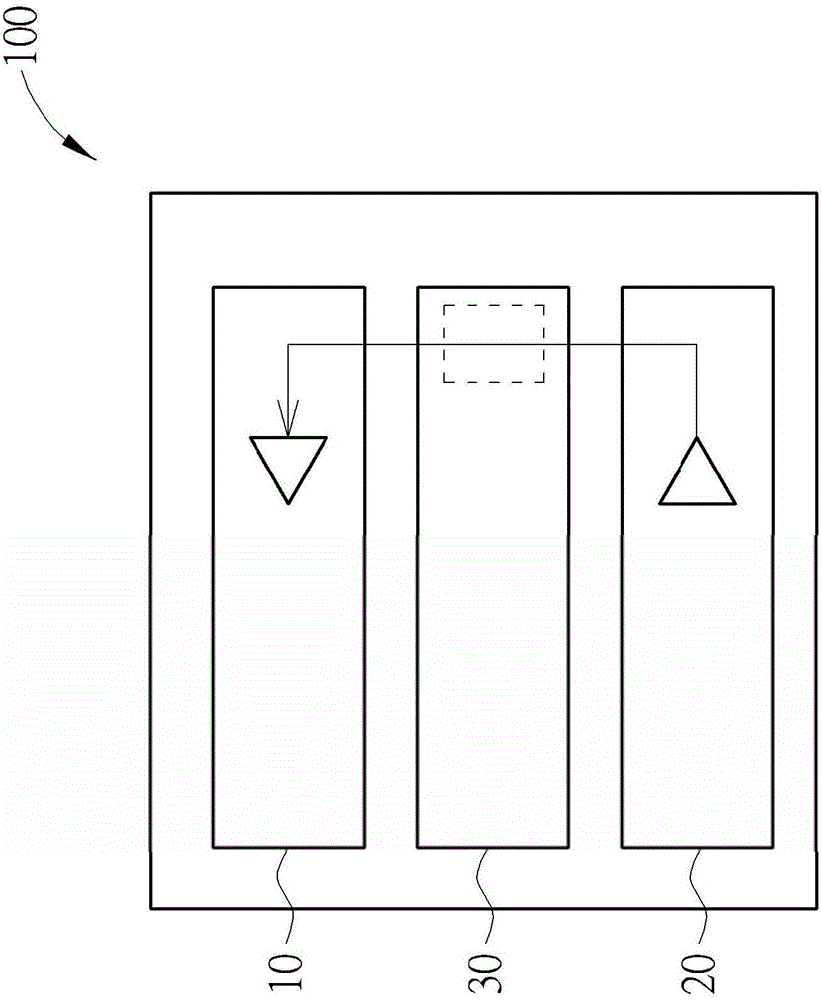

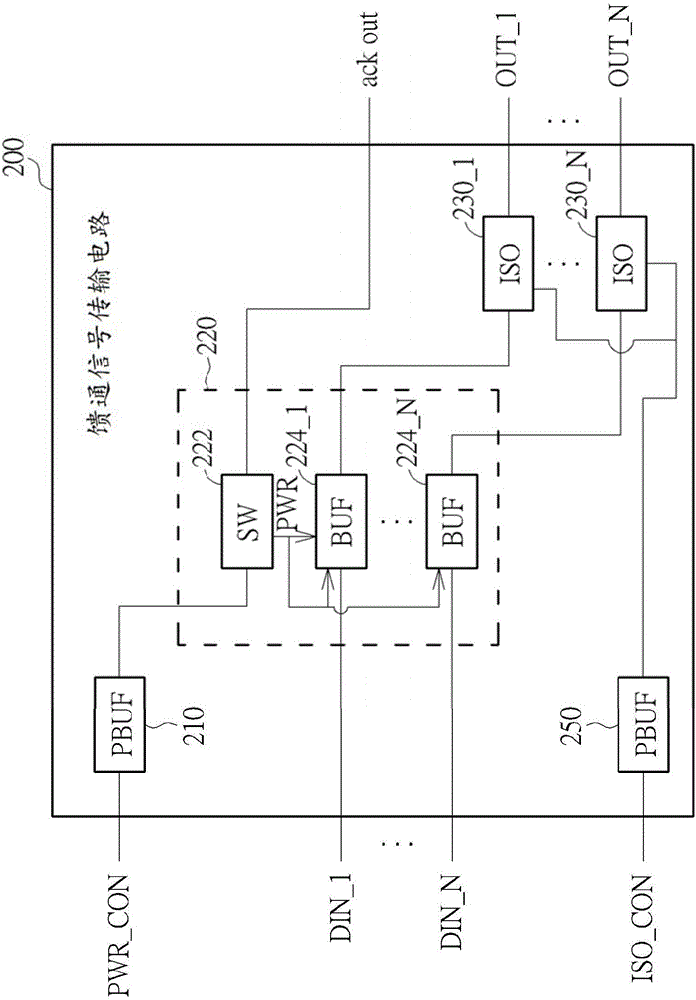

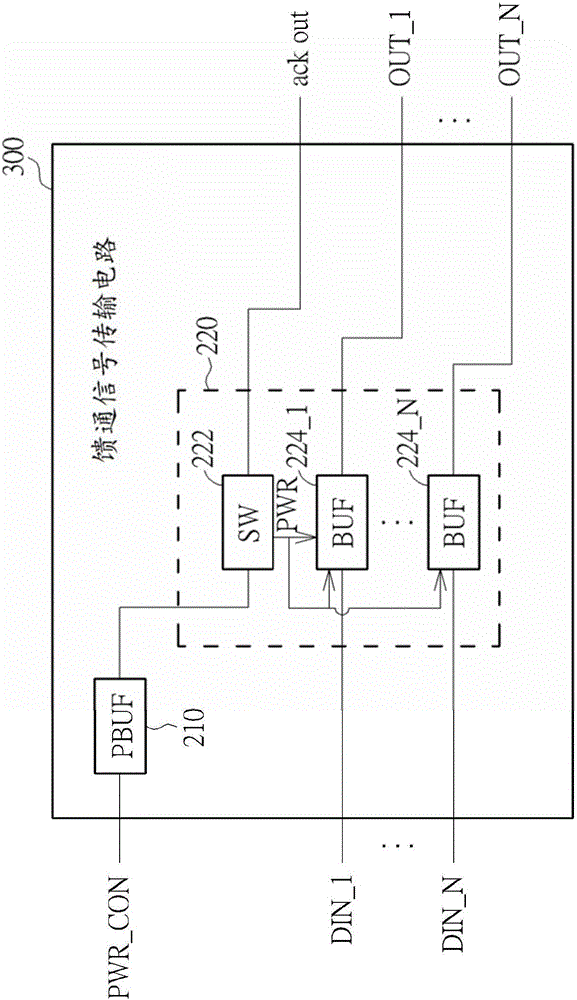

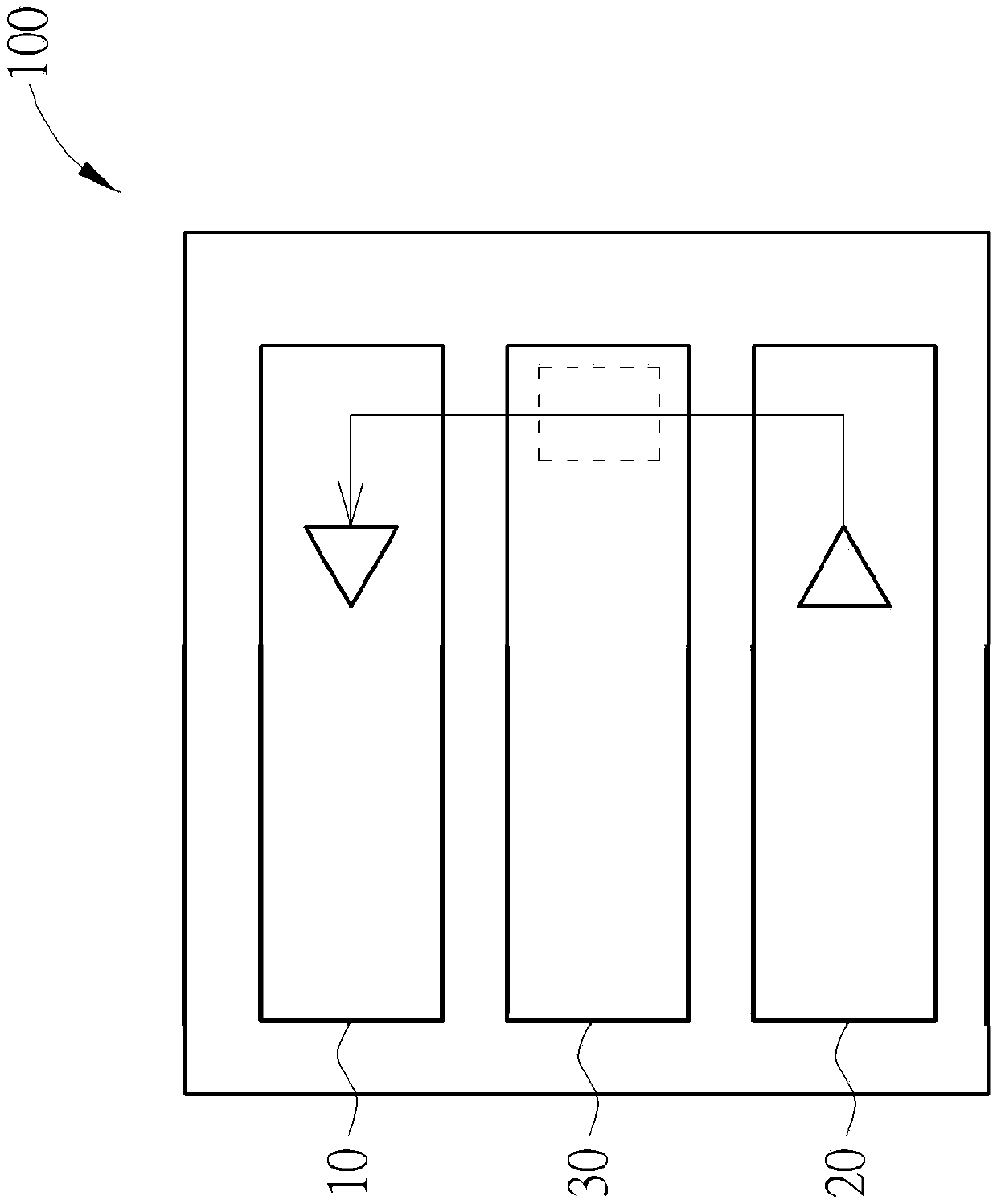

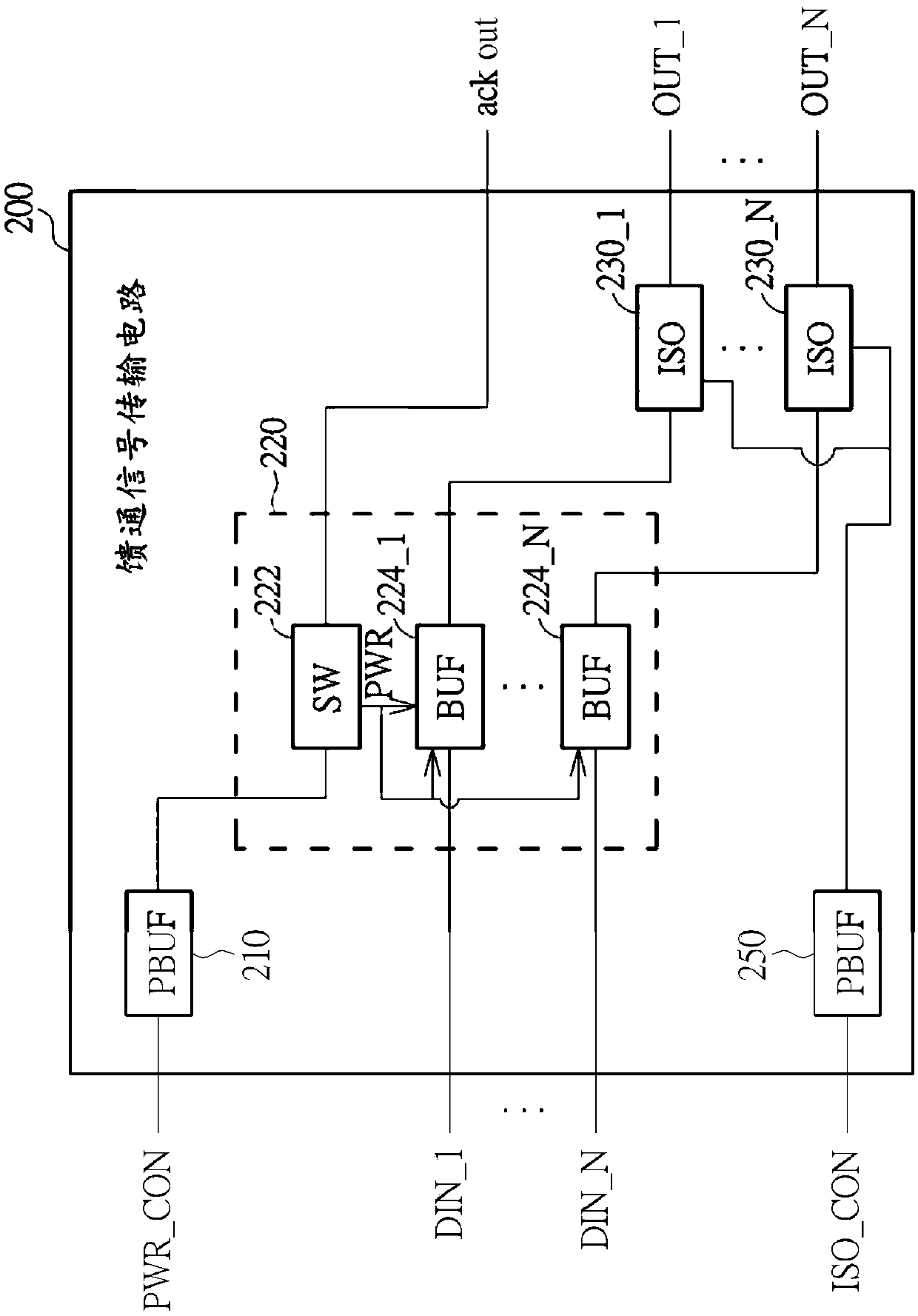

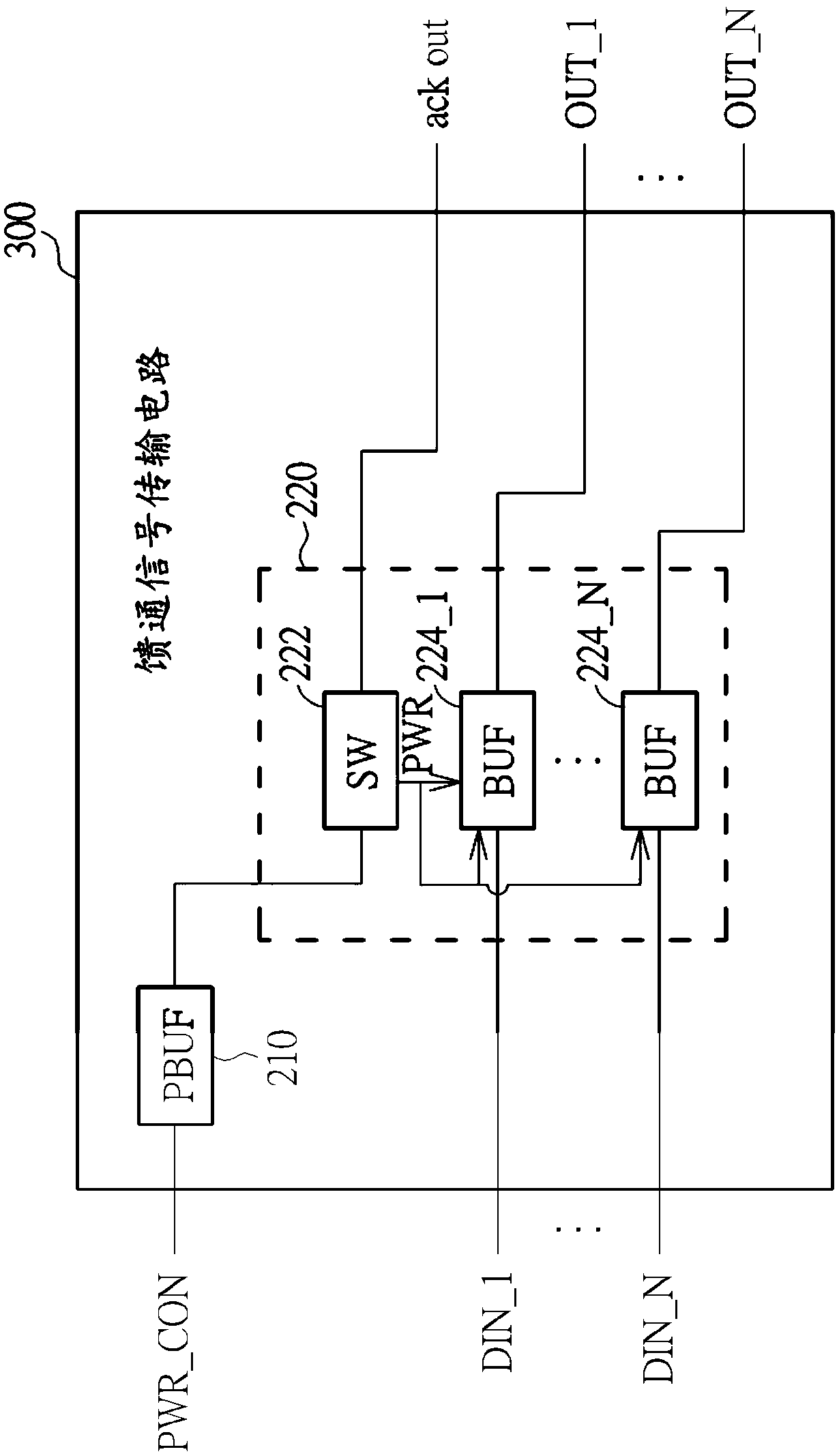

Feed-through signal transmission device/method and related feed-through signal transmission circuit

InactiveCN106301340AReduce leakage power consumptionLogic circuit interface arrangementsElectricityControl cell

The present invention relates to a feed-through signal transmission device / method and a related feed-through signal transmission circuit. The device comprises feed-through signal transmission circuits, each feed-through signal transmission circuit includes at least one subcircuit, wherein when the subcircuit executes the feed-through signal transmission, the subcircuit keeps the power-on state, and the subcircuit includes a relay for feed-through normal opening and a normally opening control cell. When the subcircuit executes the feed-through signal transmission, the power-on state of the subcircuit is kept, wherein the subcircuits of the feed-through signal transmission circuit are located at the position of the single silicic chip areas based on the grids. The feed-through signal transmission device / method and the related feed-through signal transmission circuit can perform cutting-off according to the requirement so as to greatly reduce the electric leakage power loss.

Owner:MEDIATEK INC

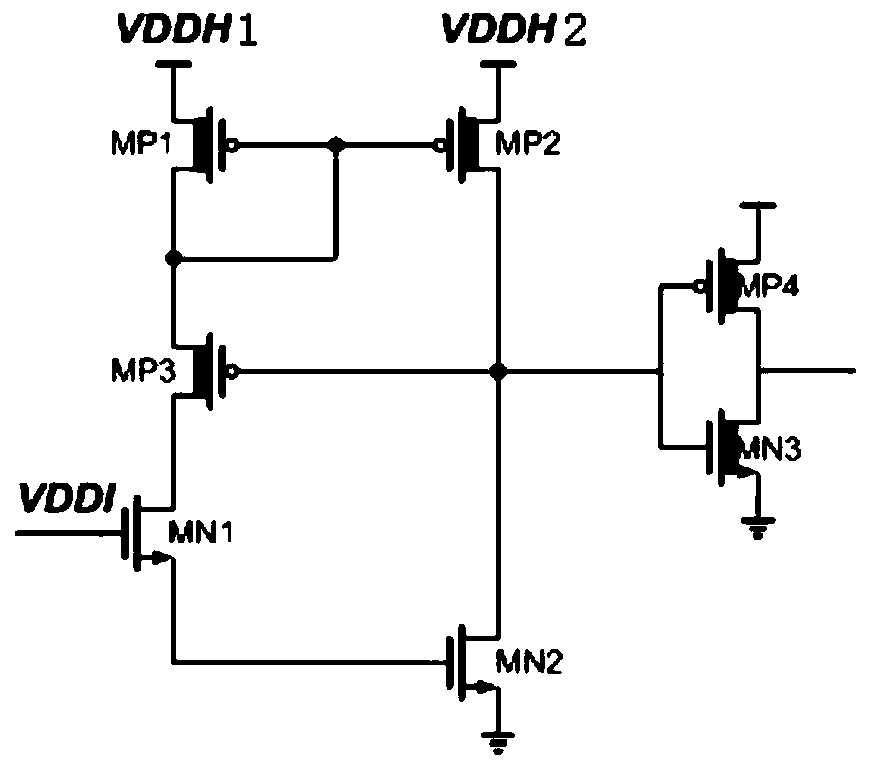

Level shifter

PendingCN111355481AReduce complexityFully consider the driving abilityLogic circuits coupling/interface using field-effect transistorsConvertersWilson current mirror

The invention discloses a level shifter. The level shifter comprises a Wilson current mirror circuit and a phase inverter circuit. The Wilson current mirror circuit is connected with the inverter circuit, the inverter circuit comprises an inverter circuit PMOS tube and an inverter circuit NMOS tube, an output end of the Wilson current mirror circuit is connected with a grid electrode of the PMOS tube of the inverter circuit and a grid electrode of the NMOS tube of the inverter circuit, a source electrode of the PMOS tube of the inverter circuit is connected with a inverter circuit power supply, a drain electrode of the PMOS tube of the inverter circuit is connected with the drain electrode of the NMOS tube of the inverter circuit, and a source electrode of the NMOS transistor of the inverter circuit is grounded. The level shifter has the advantages that the circuit structure is simple, and the delay time and the power consumption of the circuit can be effectively reduced.

Owner:北京中科芯蕊科技有限公司

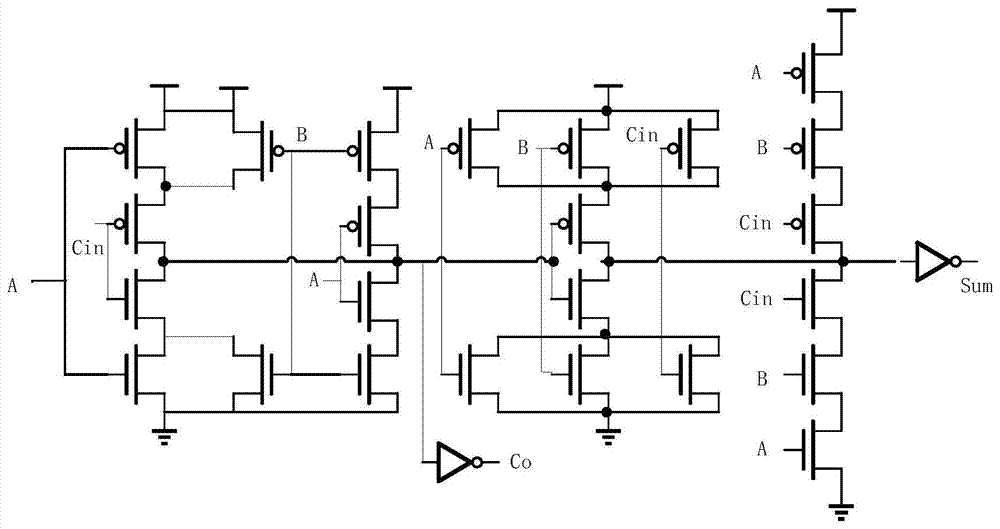

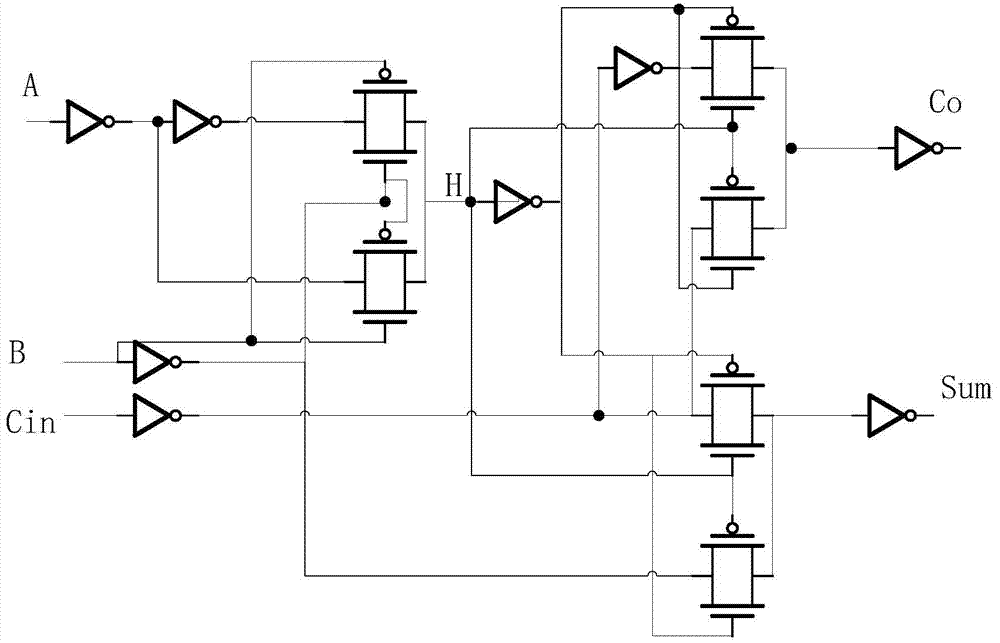

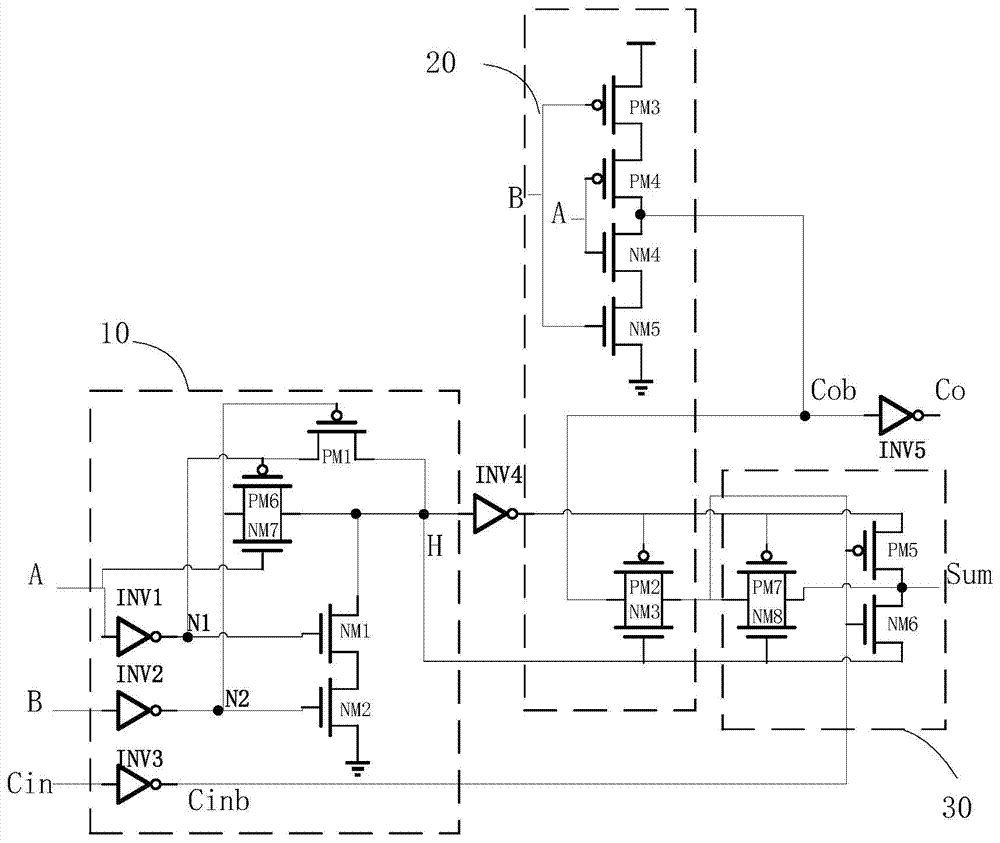

A Low-power, low-area, non-compete 1 Bit full adder standard cell

InactiveCN104333371AReduce power consumptionAvoid direct connectionLogic circuits characterised by logic functionCouplingExclusive or

The invention discloses a low-power, low-area, non-compete 1 bit full adder standard cell, having first to third input terminals, a Carry bit output terminal and an And bit output terminal, wherein the minimum operating voltage is less than or equal to 0.81V, the low-power, low-area, non-compete 1 bit full adder standard cell comprises: an exclusive OR circuit, for generating an exclusive OR signal required by And bit and Carry bit output; a summing circuit for outputting an And bit related signal; and a Carry bit output circuit, which outputs Carry bit result using coupling of a transmission pipe to a mirror circuit. The working condition of the circuit of the invention covers all process corners and harsh temperature ranges (-40 DEG C to 125 DEG C), there is no competition of Carry bit output terminal, and the invention is applicable for computing cell modules in various consumer electronic products.

Owner:SHANGHAI JIAO TONG UNIV

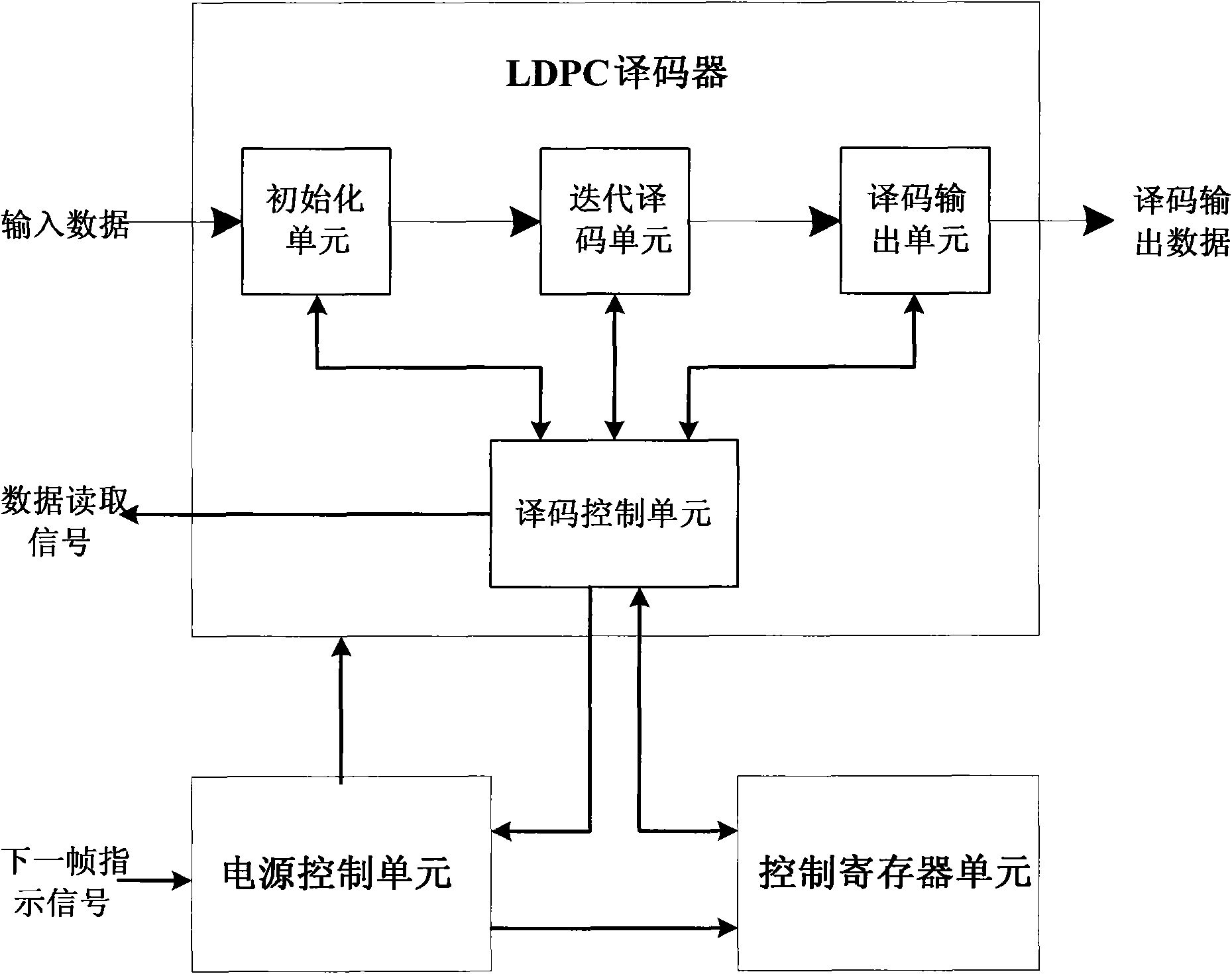

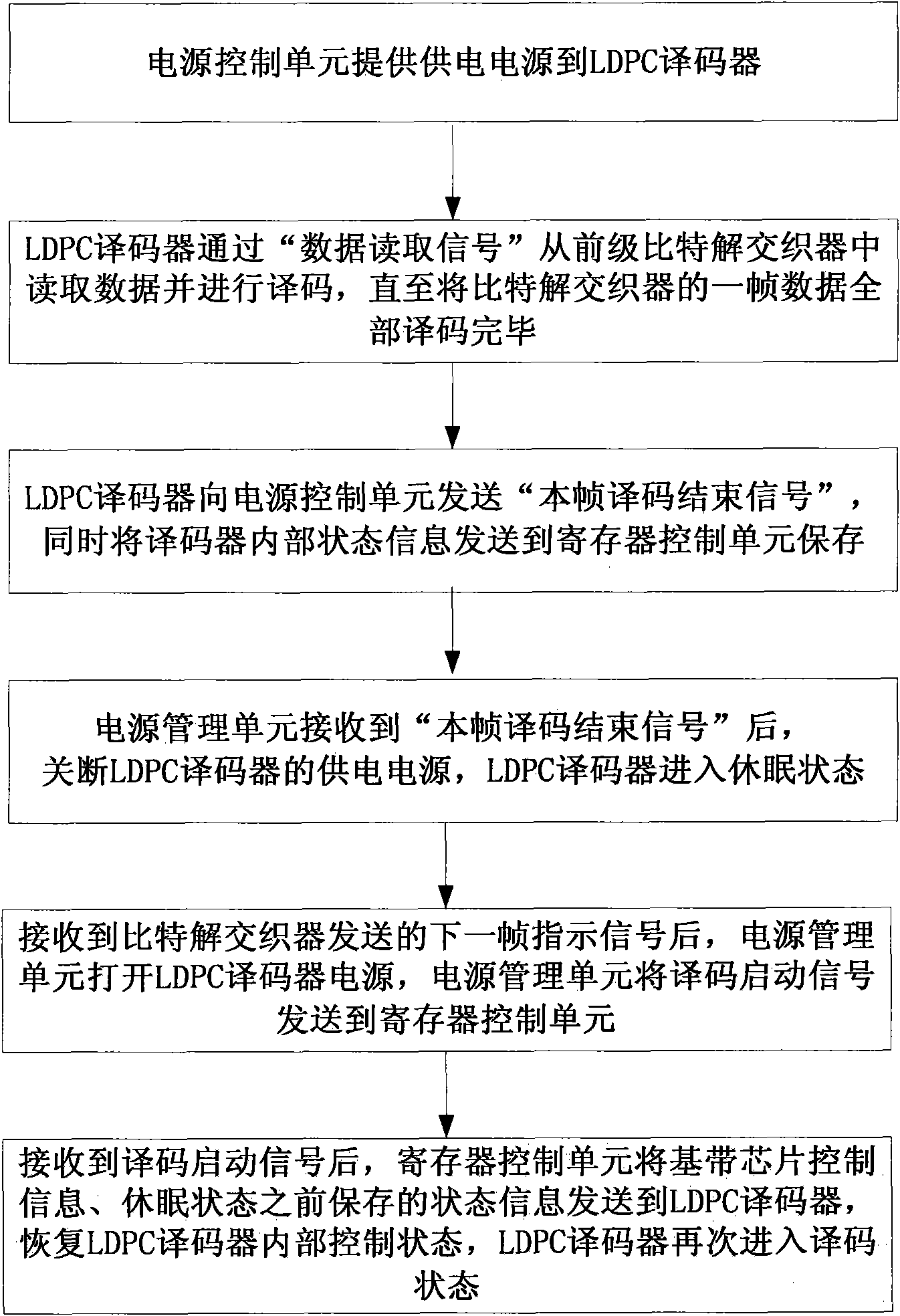

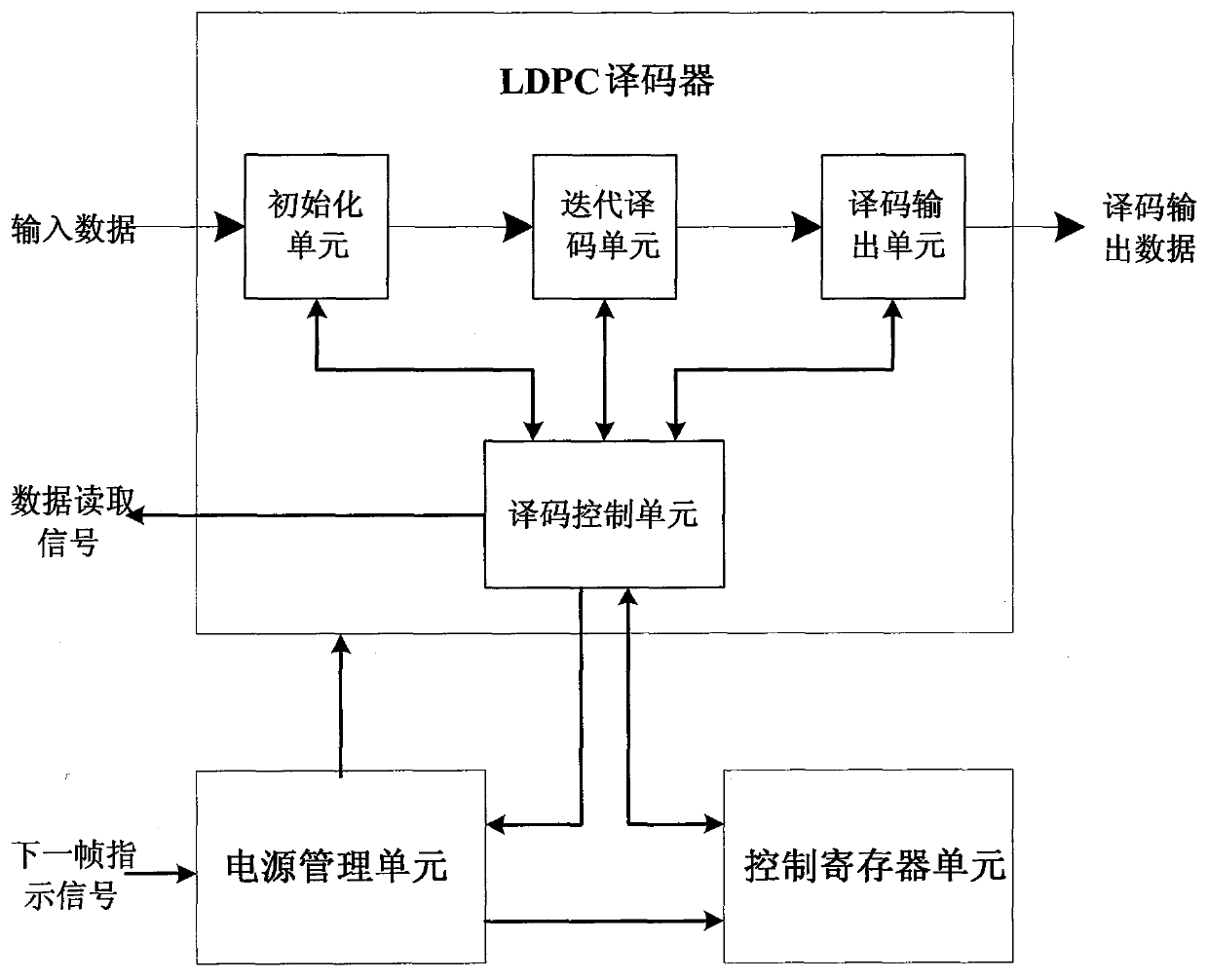

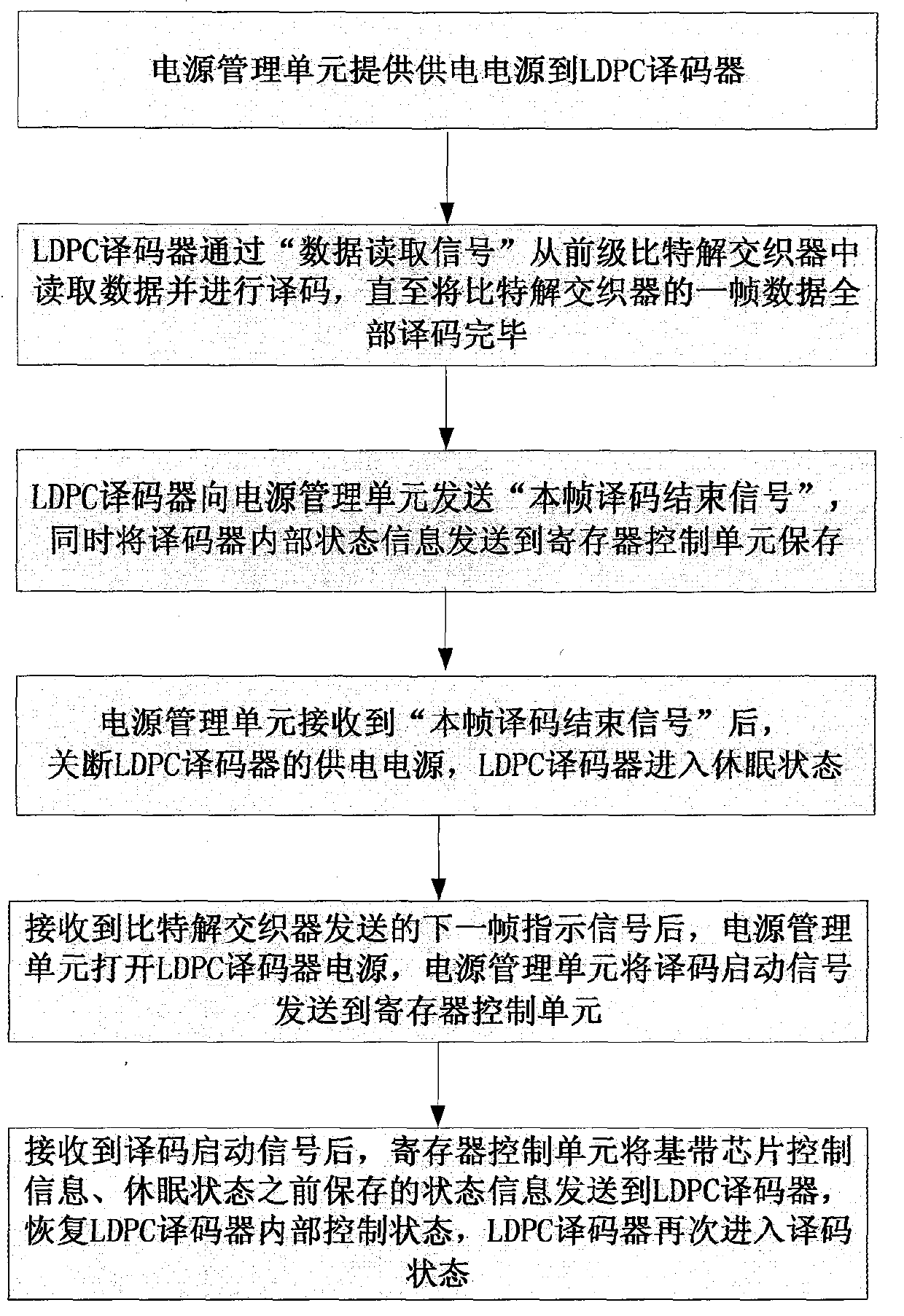

Low-power-consumption low density parity check code (LDPC) decoding device in China mobile multimedia broadcasting (CMMB) receiving machine and implementation method thereof

InactiveCN102316559AReduce leakage power consumptionReduce dynamic power consumptionPower managementEnergy efficient ICTLdpc decodingWork status

The invention provides a low-power-consumption low density parity check code (LDPC) decoding device in a China mobile multimedia broadcasting (CMMB) receiving machine, which consists of an LDPC decoder, a power supply control unit and a control register unit, wherein the LDPC decoder consists of an initialization unit, an iterative decoding unit, a decoding output unit and a decoding control unit, and the power supply control unit provides an electricity supply power supply for the LDPC decoder and controls the work state of the LDPC decoder, so the goal of saving dynamic and electricity leakage power consumption is reached. Simultaneously, the control register unit stores and provides the base band chip control information and the internal state information before the dormancy state of the LDPC decoder for the LDPC decoder. Simultaneously, the invention also provides an implementation method of the low-power-consumption LDPC decoding device. Through the device and the method, the decoder electricity leakage power consumption and the dynamic power consumption can be effectively reduced, so the power consumption of a receiving machine chip in the application can be reduced.

Owner:SHANGHAI HUAHONG INTEGRATED CIRCUIT

Low-power-consumption low density parity check code (LDPC) decoding device in China mobile multimedia broadcasting (CMMB) receiving machine and implementation method thereof

InactiveCN102316559BReduce leakage power consumptionReduce dynamic power consumptionPower managementEnergy efficient ICTElectricityProcessor register

The invention provides a low-power-consumption low density parity check code (LDPC) decoding device in a China mobile multimedia broadcasting (CMMB) receiving machine, which consists of an LDPC decoder, a power supply control unit and a control register unit, wherein the LDPC decoder consists of an initialization unit, an iterative decoding unit, a decoding output unit and a decoding control unit, and the power supply control unit provides an electricity supply power supply for the LDPC decoder and controls the work state of the LDPC decoder, so the goal of saving dynamic and electricity leakage power consumption is reached. Simultaneously, the control register unit stores and provides the base band chip control information and the internal state information before the dormancy state of the LDPC decoder for the LDPC decoder. Simultaneously, the invention also provides an implementation method of the low-power-consumption LDPC decoding device. Through the device and the method, the decoder electricity leakage power consumption and the dynamic power consumption can be effectively reduced, so the power consumption of a receiving machine chip in the application can be reduced.

Owner:SHANGHAI HUAHONG INTEGRATED CIRCUIT

Wafer-level electric leakage reducing ESD structure

PendingCN114597881ASmall footprintGuaranteed to workTransistorSolid-state devicesHemt circuitsFeedback circuits

The invention discloses a wafer-level electric leakage reducing ESD (Electro-Static Discharge) structure, which comprises a control circuit, a feedback circuit, a bleeder circuit and a clamping circuit which are packaged by adopting a wafer-level packaging process, wherein the first input end of the control circuit is connected with a power supply VCC1, the second input end of the control circuit is connected with a power supply VCC2, the first output end of the control circuit is sequentially connected with the feedback circuit, the bleeder circuit and the clamping circuit, and the second output end of the control circuit is connected with the feedback circuit; the output end of the feedback circuit is connected with the output end of the bleeder circuit; the output end of the bleeder circuit is connected with the first input end of the clamping circuit, and the second input end of the clamping circuit is connected with a power supply VDD. Through the control circuit, the feedback circuit, the bleeder circuit and the clamping circuit which are packaged by a wafer-level process, the occupied area of a chip can be effectively reduced, the stability of output voltage is improved, the safety and stability of the chip and the circuit after ESD (Electro-Static Discharge) occur are ensured, and meanwhile, the loss caused by electric leakage is reduced.

Owner:中国人民解放军96901部队23分队

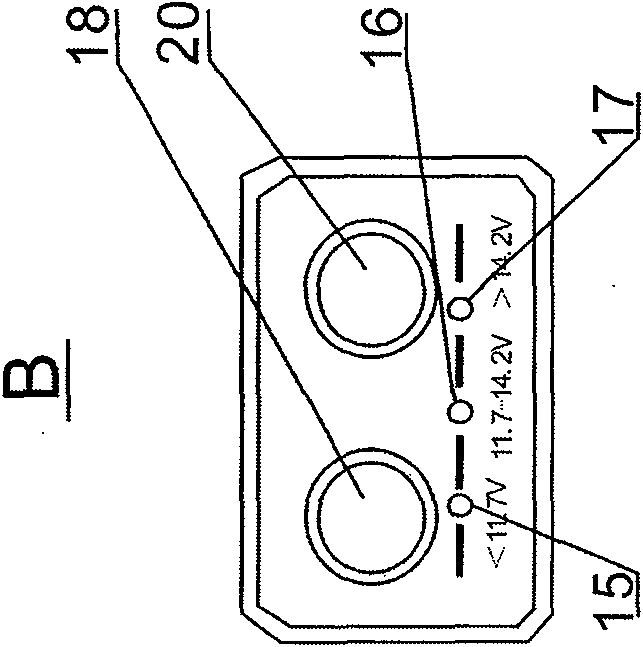

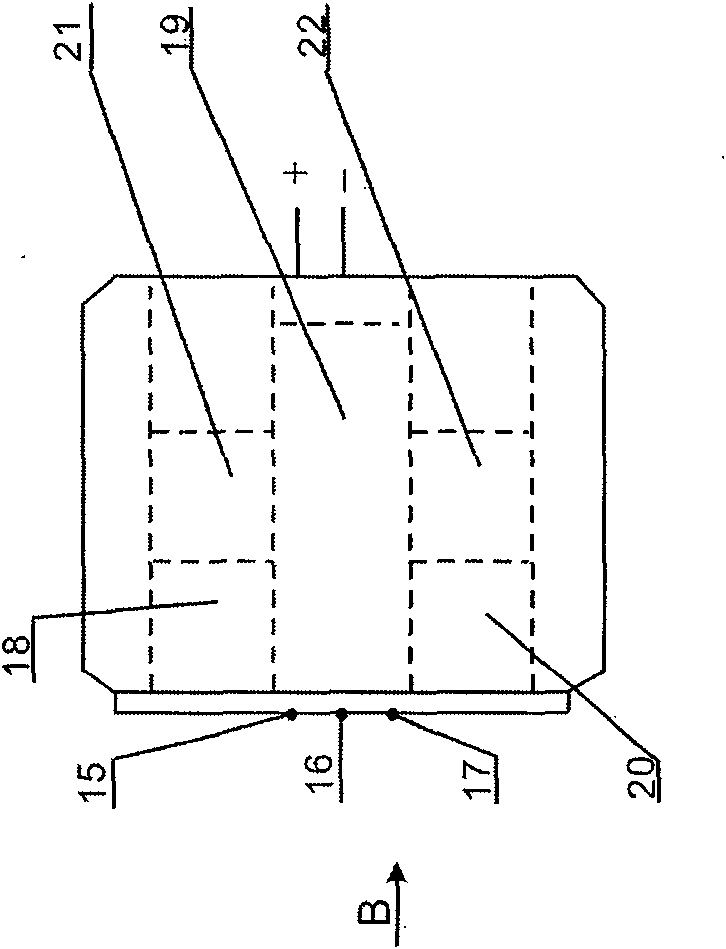

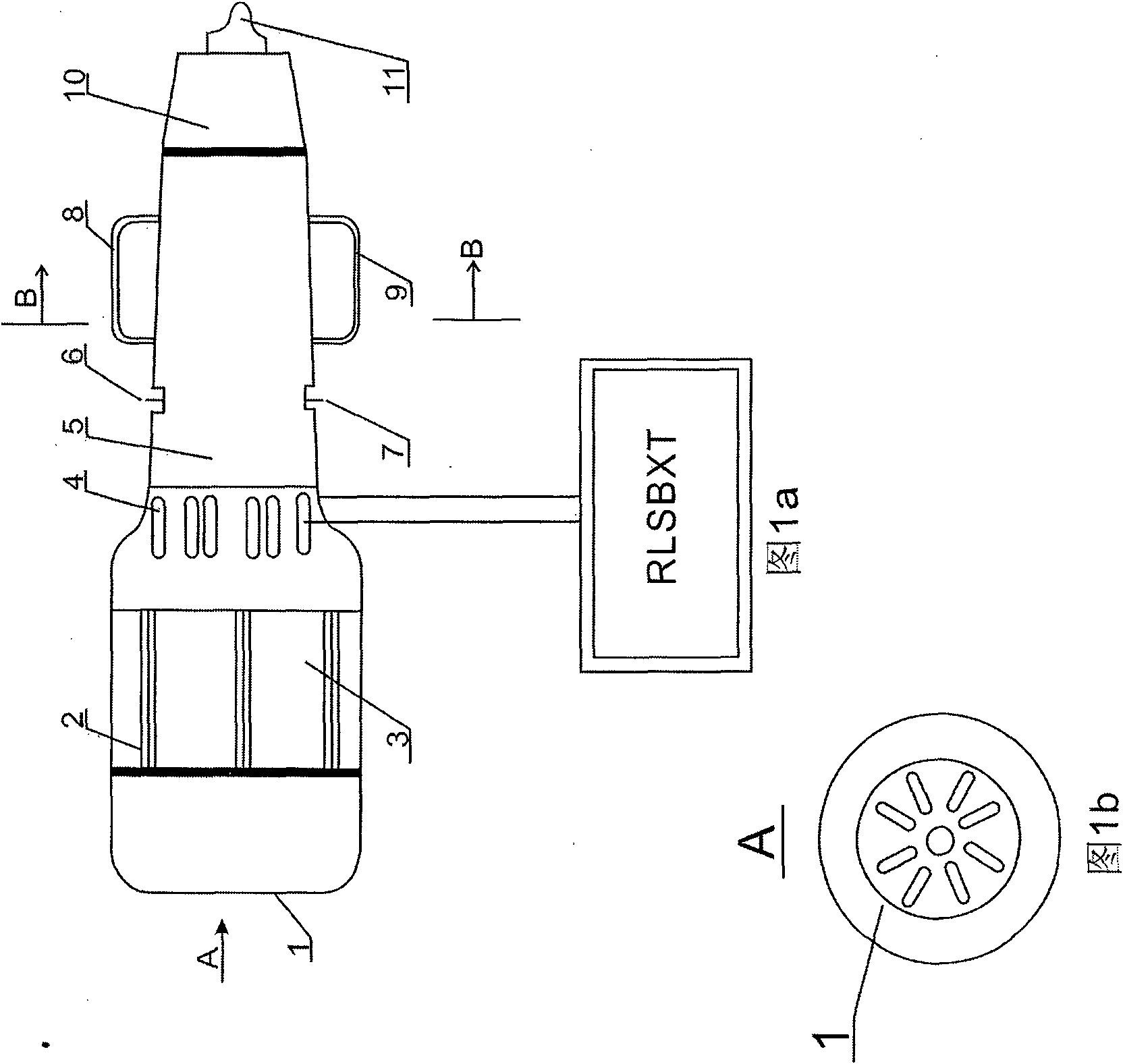

Automobile electronic safety device having dual energy and dual effect and being energy-saving and emission-reducing

ActiveCN102720620AConvenience trade-offEasy maintenanceAnti-theft devicesMachines/enginesFuel oilDual energy

An automobile electronic safety device having a dual energy and a dual effect and being energy-saving and emission-reducing relates to the field of energy-saving and emission-reducing automobile electronic safety and consists of a main machine and two auxiliary machines. The main machine comprises an outer round housing, an energy-saving control circuit board, a resistor, capacitors, diodes and switches. An anode of a control pole communicates with an anode cap of a tail end. A cathode communicates with a cathode spring on the external part of the housing. A tail part is inserted into any hole of a first auxiliary machine to communicate with the first auxiliary machine. Effect is upon a circuit to generate strong electric sparks to ignite fuel oil so that fuel saving and emission reduction can be realized. The first auxiliary machine has a power connector which is capable of automatic-tracking voltage detection and comprises a square housing, seven diodes of a control circuit, and resistors. Yellow, green, and red luminous tubes indicate that the voltage is low, normal and high. A control terminal communicates with an automobile output terminal. The first auxiliary machine is used to automatically track and display measured voltage to guarantee the security of the circuits during driving. A second auxiliary machine capable of face recognition comprises a long housing and a face-recognizing control circuit. A control circuit terminal communicates with the main machine. The second auxiliary machine is used to identify the identity of a car owner to guarantee the security of automobile assets. The main machine and the auxiliary machines can constitute an integral body as well as work separately and independently.

Owner:谢自泉 +2

Low power consumption design method for SRAM (static random-access memory) type FPGA (field-programmable gate array)

ActiveCN102609563BReduce leakage power consumptionTiming impactSpecial data processing applicationsStatic random-access memoryLow-power electronics

The invention provides a low power consumption design method for a SRAM (static random-access memory) type FPGA (field-programmable gate array), which includes steps: firstly, building a leakage power information graph according to structure and circuit information of the FPGA; secondly, evaluating leakage power of each MUX during wiring phase to obtain the leakage power; thirdly, importing the leakage power to wiring cost function to lower circuit leakage power. By implementing low power consumption design during the wiring phase and comprehensively considering delay consumption, congestion consumption and leakage power consumption of the circuit during the wiring process, timing performance of the circuit is hardly affected. By modifying circuit wiring manner to implement low power consumption design, the method is irrelevant with chip structure of the FPGA and suitable for current mainstream FPGA, processing of the FPGA chips is not affected and no extra area consumption is imported.

Owner:INST OF COMPUTING TECH CHINESE ACAD OF SCI

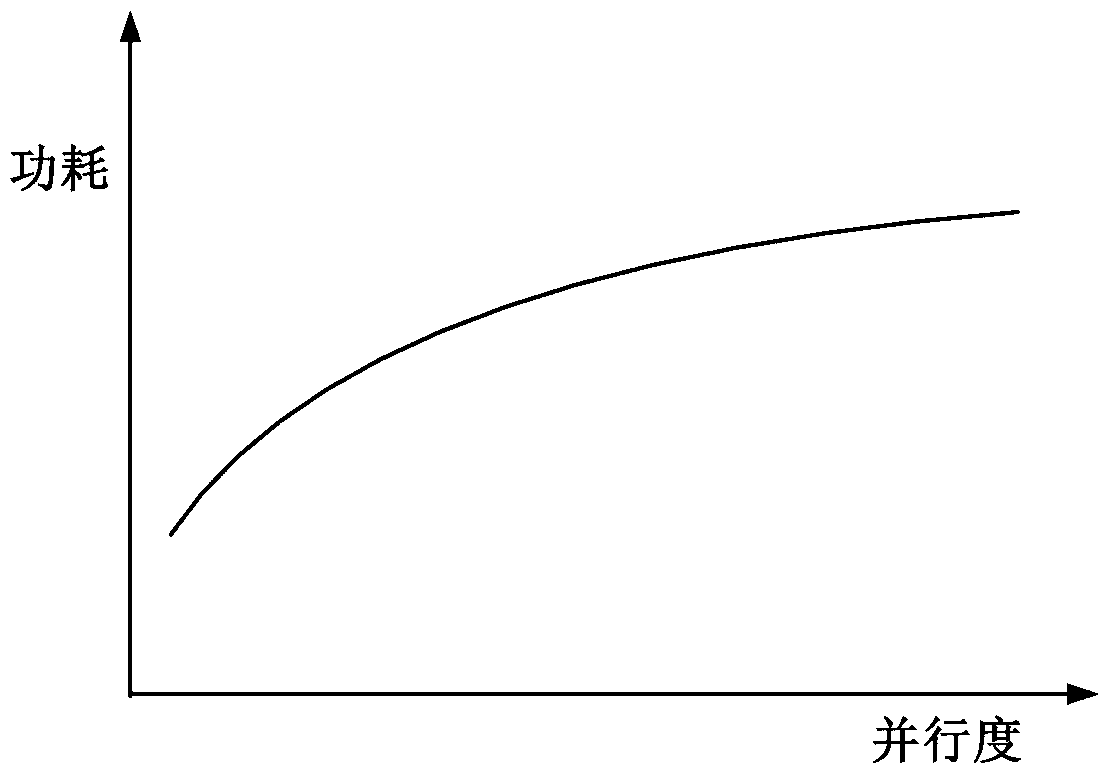

Parallelism degree adjustment algorithm for reducing power consumption of instruction-level parallel processor

InactiveCN106445678AReduce leakage power consumptionImprove energy efficiencyResource allocationEnergy efficient computingWork performanceLeakage power

The invention relates to a parallelism degree adjustment algorithm for reducing power consumption of an instruction-level parallelism (ILP) processor. The algorithm comprises the steps of analyzing hardware resources and parallelism degree demand quantity information of parts of an input application program by utilizing a compiler, and obtaining a control flow graph (CFG) and loop hierarchy trees (LHTs) of the application program; dividing the application program: cutting the application program into different regions; setting executive parallelism degrees of the regions according to the hardware resources, the parallelism degree demand quantities and energy efficiency of the regions, so that the parallelism degree can be adjusted and changed according to the demands of executive time in the whole program execution process; and re-scheduling the program by the compiler, scheduling the regions by using the set parallelism degrees, inserting a power gating instruction before the regions are executed, and turning off idle hardware resources to reduce electric leakage power consumption. According to the algorithm, the influence of electric leakage power consumption on working performance of the processor can be reduced and the utilization rate of the hardware resources in the ILP processor can be increased.

Owner:TIANJIN UNIV

A structure and method for reducing flash memory standby power consumption

ActiveCN101984492BRaise the base biasReduce standby power consumptionRead-only memoriesBit lineStandby power

Owner:SHANGHAI HUAHONG GRACE SEMICON MFG CORP

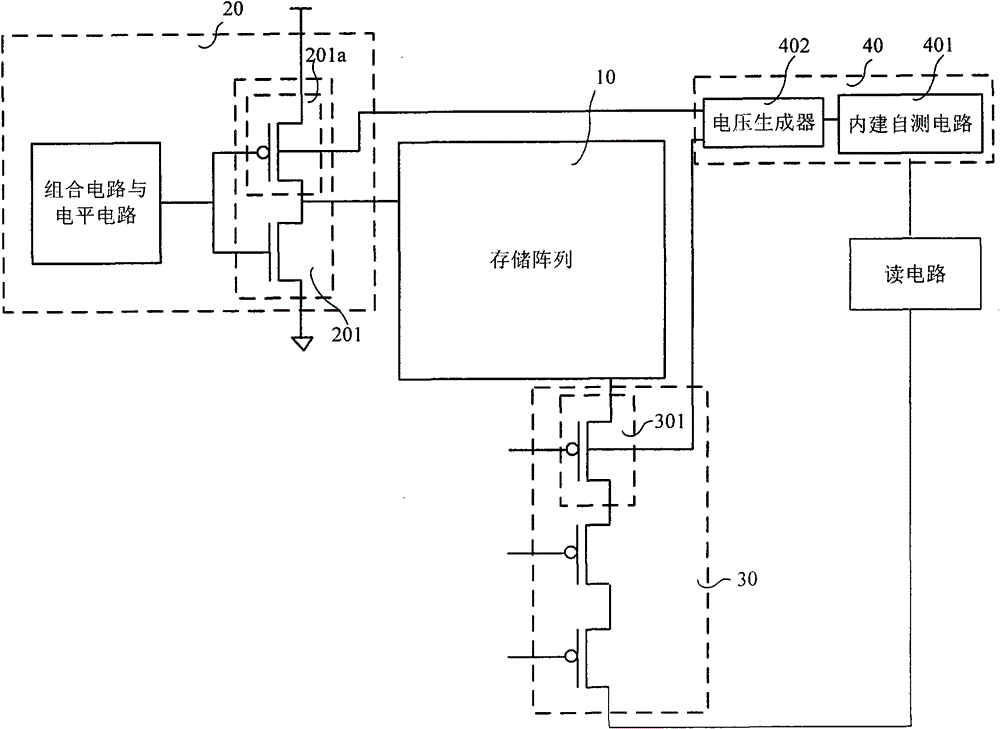

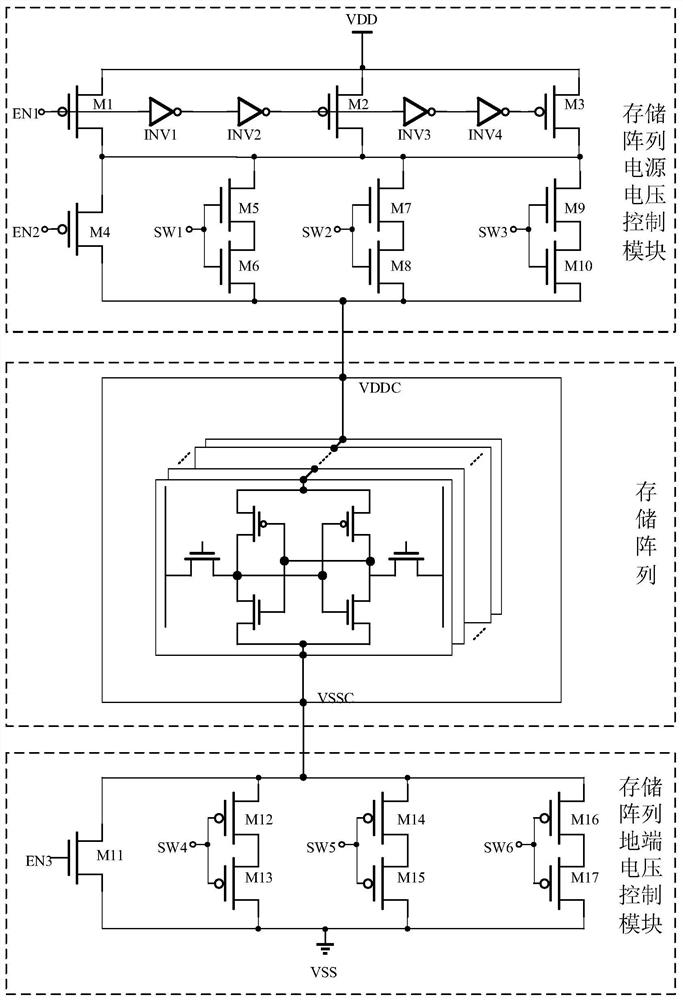

Circuit for reducing leakage current of SRAM storage array and control method

ActiveCN111863070ALower the actual data hold voltageReduce leakage power consumptionDigital storageStatic random-access memoryTerminal voltage

The invention discloses a circuit for reducing leakage current of an SRAM (Static Random Access Memory) storage array and a control method. The circuit comprises a storage array power supply voltage control module, a storage array ground terminal voltage control module and the storage array; the voltage of the power supply end and the voltage of the ground end of the storage array are controlled through the storage array power supply voltage control module and the storage array ground end control module, and the actual data holding voltage of the storage unit can be reduced, so that the electric leakage power consumption of the SRAM in a data holding state is reduced. The function of adjusting the data maintaining voltage value of the storage unit is realized by controlling different adjusting signals so as to meet different design requirements. According to the invention, the leakage current of the storage array of the SRAM in the number holding state can be effectively reduced, and in a storage system realized by the SRAM, a low-power-consumption scheme that the necessary SRAM holds data with low electric leakage overhead and the rest SRAMs completely turn off a power supply canbe realized.

Owner:NANJING LOW POWER IC TECH INST CO LTD

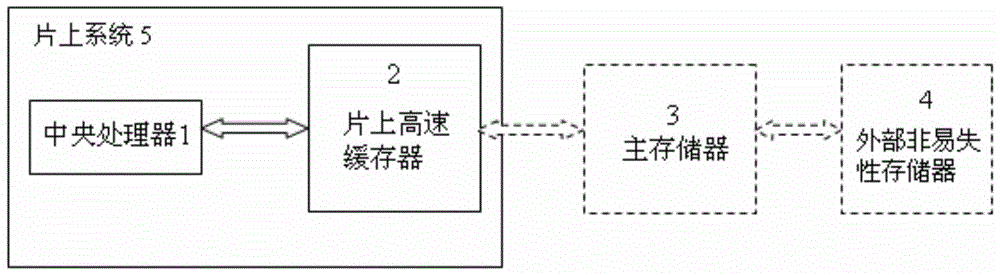

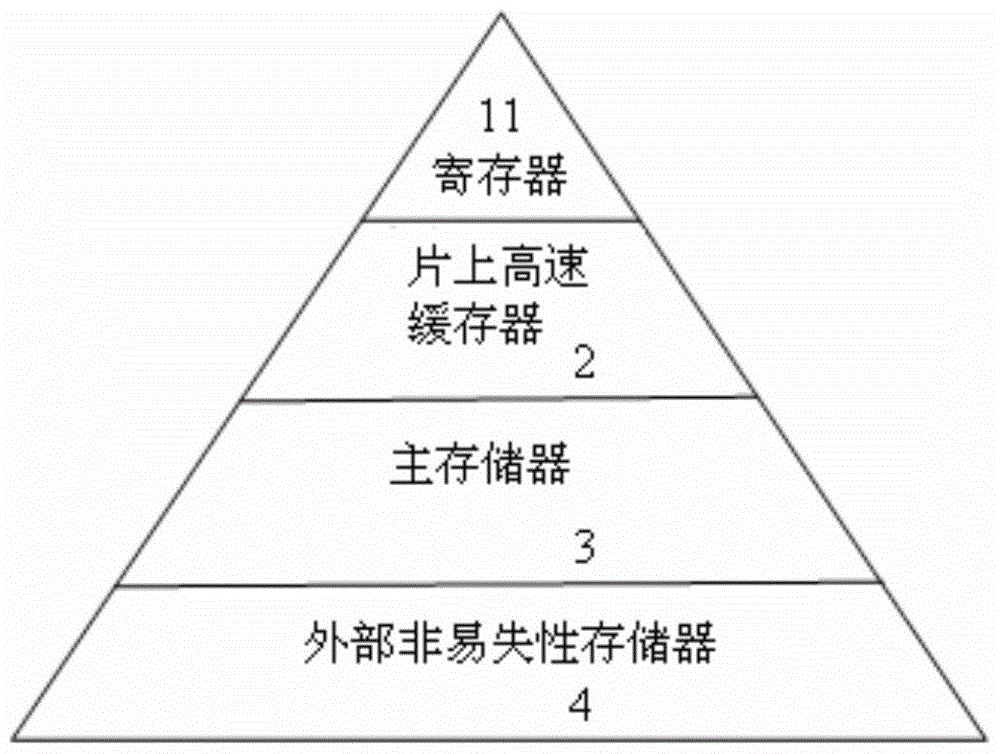

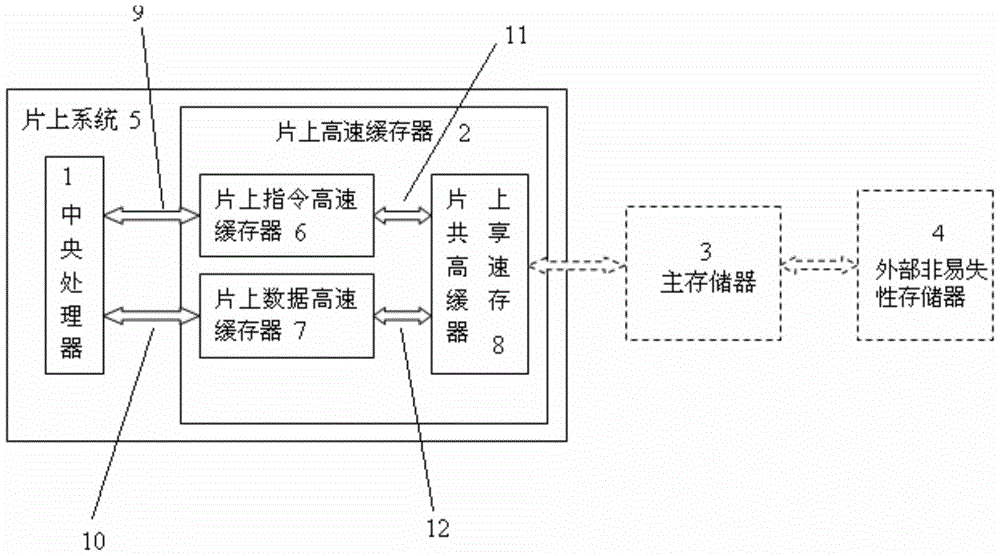

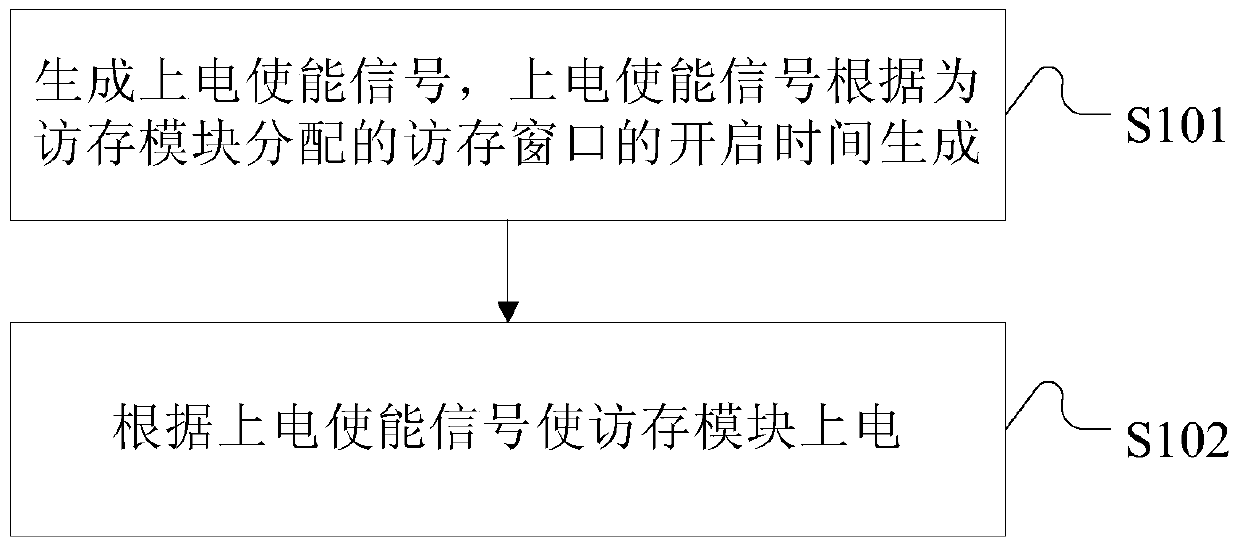

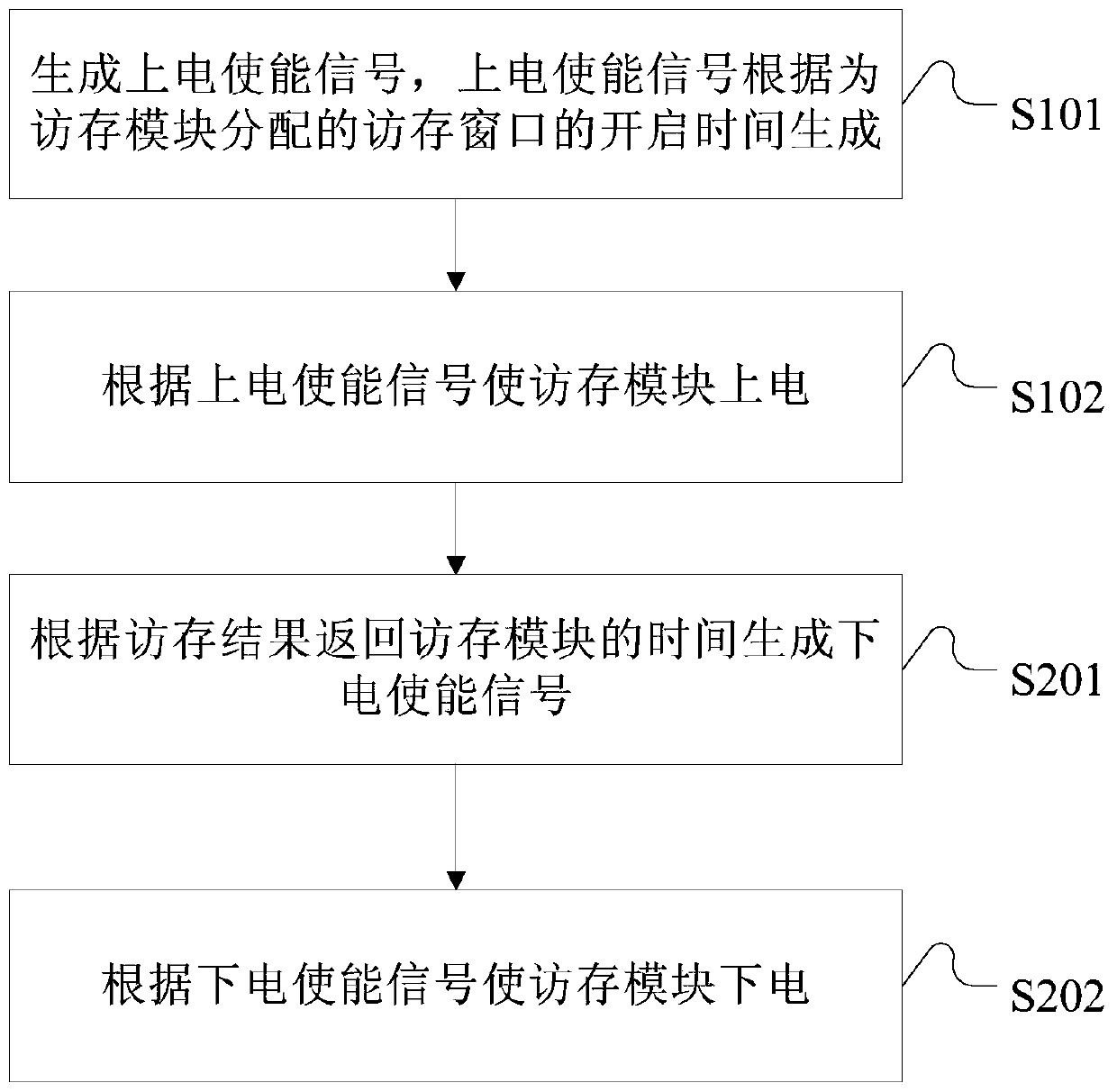

A fast-starting low-power computer system-on-chip with self-learning function

ActiveCN103593324BImprove experienceReduce startup timeGeneral purpose stored program computerProgram loading/initiatingInternal memoryOperational system

The invention relates to the technical field of computers, in particular to a computer system-on- chip. The quick-start and low-power-consumption computer system-on-chip with the self-learning function comprises a central processing unit and an on-chip mixed cache, and the central processing unit is connected with the on-chip mixed cache. The on-chip mixed cache comprises an on-chip nonvolatile memory, further comprises an on-chip cache and is connected with an out-chip main memory and an external high-capacity nonvolatile memory. The quick-start and low-power-consumption computer system-on-chip with the self-learning function further comprises a system monitoring statistics module, and the system monitoring statistics module is used for obtaining, configuring and loading operating system start-up information and / or heat application program information to the on-chip nonvolatile memory. The power-on time of an operating system and the starting time of a heat application program can be saved on the basis of keeping high performance of the system, and the power consumption produced when data are guided into an internal storage from the external high-capacity nonvolatile memory to be read by the central processing unit can be reduced.

Owner:SHANGHAI XINCHU INTEGRATED CIRCUIT

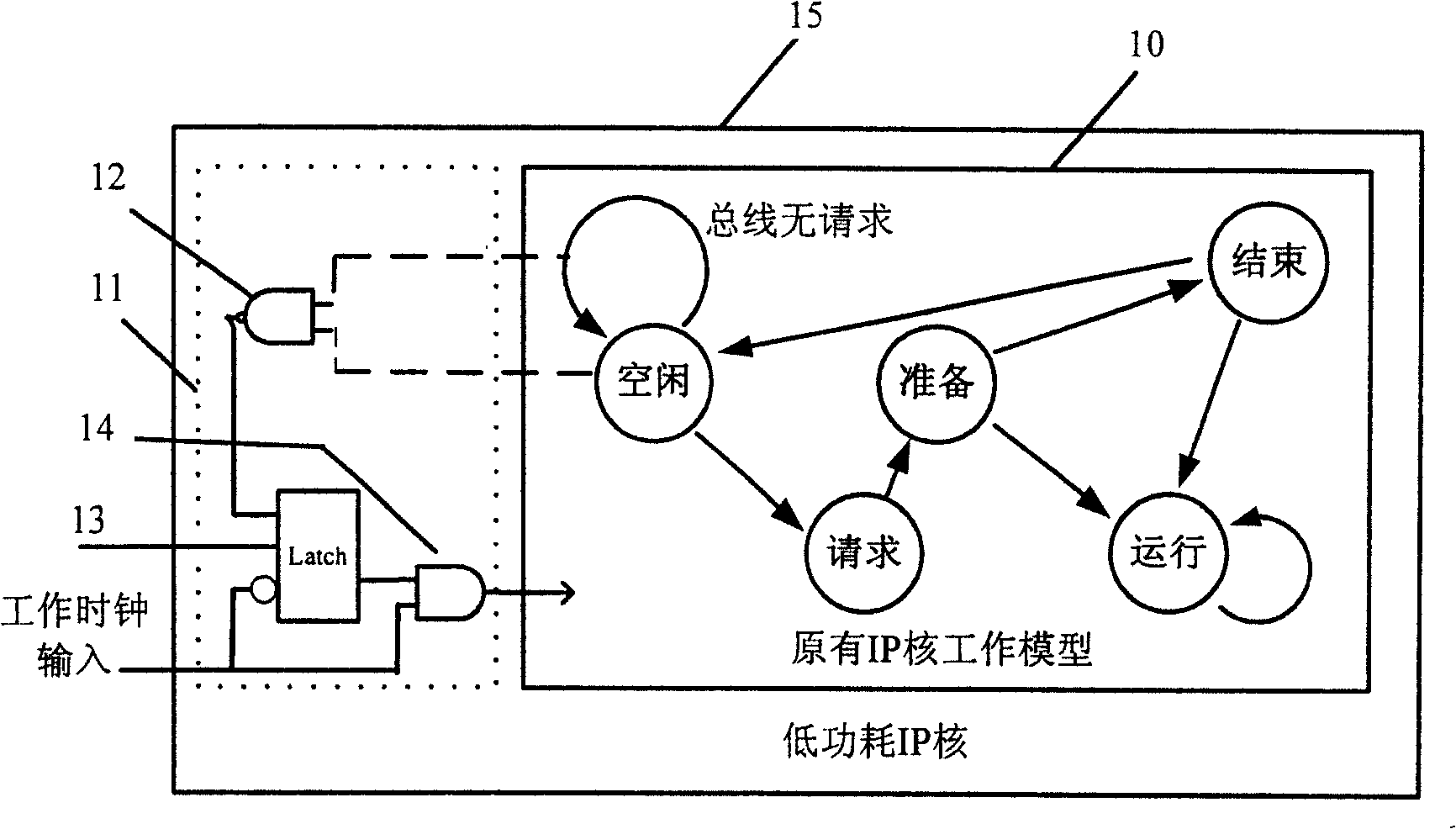

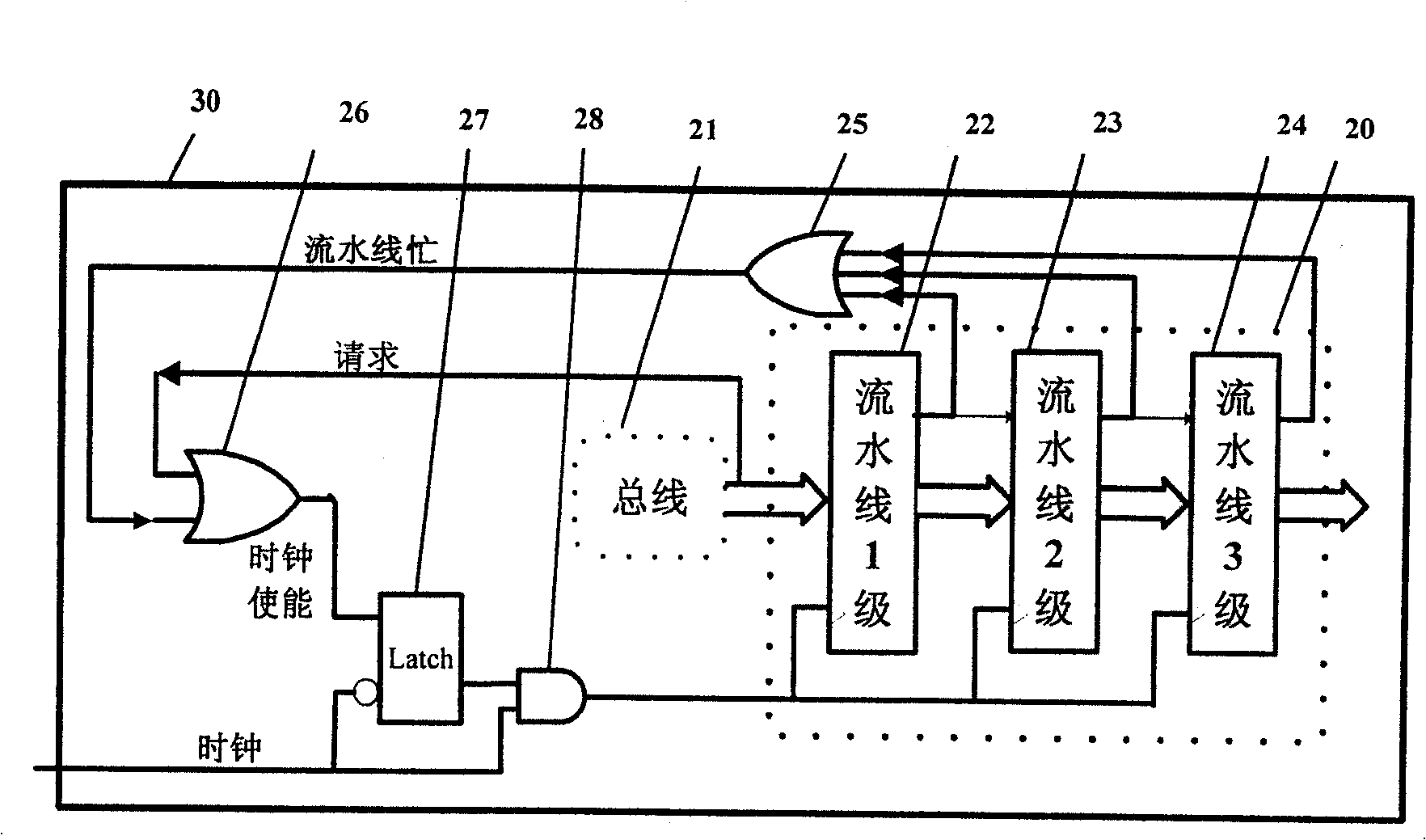

Power consumption reduction method for intellectual core and functional module for chip system

InactiveCN100442203CReduce dynamic power consumptionReduce leakage power consumptionPower supply for data processingComputer scienceLow power dissipation

The invention discloses a power decreasing method of various intellective property core and functional module in SoC, which comprises the following steps: a) dividing all states of original functional module to two specie-' free' state and ' working' state; b) providing a logic circuit; connecting to the original functional module; constructing new low power functional module; finishing the logic function with the logic circuit; keeping clock close if without request for the original functional module; opening the clock if with the request for the original functional module; entering the original functional module into the ' working' state; closing the clock till the original functional module in ' free' state without bus request. This invention decreases dynamic state and leaking power consumption of IP core and auto-switches power source of the IP core at the same time.

Owner:INST OF COMPUTING TECH CHINESE ACAD OF SCI

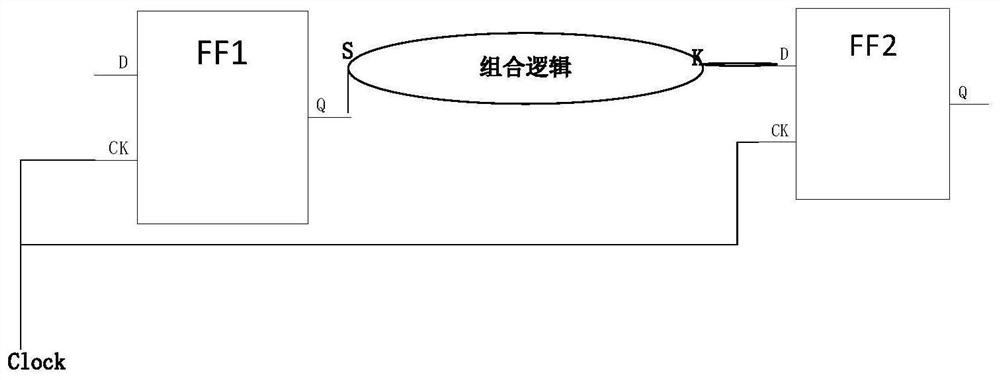

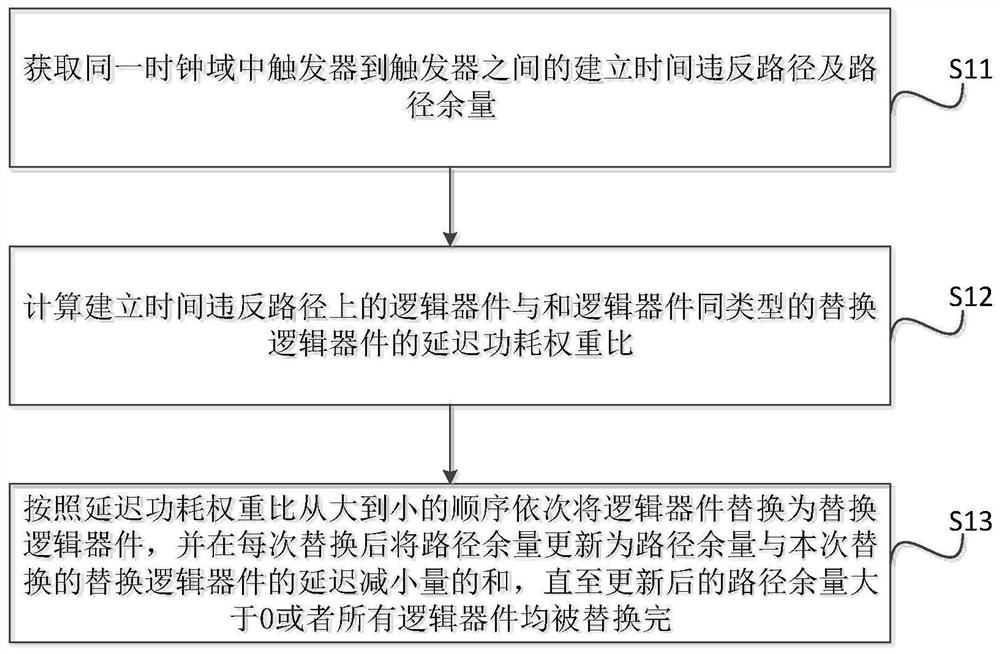

Method, device and system for correcting establishment time violation

PendingCN112564682AReduce leakage power consumptionImprove efficiency in fixing setup time violationsElectronic switchingLogisimControl theory

The invention discloses a method, device and system for correcting establishment time violation, and the method comprises the steps: sequentially replacing logic devices with replacement logic devicesaccording to delay power consumption weight ratios in a descending order when the logic devices on an establishment time violation path are replaced; and updating the path margin to the sum of the path margin and the delay reduction amount of the replaced logic device after each replacement until the updated path margin is greater than 0 or all logic devices are replaced. Visibly, on the basis ofthe technology of replacing the logic devices of the same type, the power consumption of replacing the logic devices is also considered, and the larger the delay power consumption weight ratio is, the larger the delay gain obtained after the logic devices are replaced is, so that the increased electric leakage power consumption is less; visibly the device replacement is carried out according to the descending order of the delay power consumption weight ratios, so that the increase of the leakage power consumption can be reduced on the basis of short correction and establishment time, and theefficiency of violation of the correction and establishment time is improved.

Owner:SHENZHEN DAPU MICROELECTRONICS CO LTD

A Parallelism Adjustment Algorithm to Reduce Power Consumption of Instruction-Level Parallel Processors

InactiveCN106445678BReduce leakage power consumptionImprove energy efficiencyResource allocationEnergy efficient computingControl flowParallel processing

The invention relates to a parallelism degree adjustment algorithm for reducing power consumption of an instruction-level parallelism (ILP) processor. The algorithm comprises the steps of analyzing hardware resources and parallelism degree demand quantity information of parts of an input application program by utilizing a compiler, and obtaining a control flow graph (CFG) and loop hierarchy trees (LHTs) of the application program; dividing the application program: cutting the application program into different regions; setting executive parallelism degrees of the regions according to the hardware resources, the parallelism degree demand quantities and energy efficiency of the regions, so that the parallelism degree can be adjusted and changed according to the demands of executive time in the whole program execution process; and re-scheduling the program by the compiler, scheduling the regions by using the set parallelism degrees, inserting a power gating instruction before the regions are executed, and turning off idle hardware resources to reduce electric leakage power consumption. According to the algorithm, the influence of electric leakage power consumption on working performance of the processor can be reduced and the utilization rate of the hardware resources in the ILP processor can be increased.

Owner:TIANJIN UNIV

A Design Optimization Method for Instruction Level Parallel Processor with Low Power Consumption

InactiveCN105929928BReduce leakage power consumptionImprove energy efficiencyPower supply for data processingEnergy efficient computingWork performanceLow-power electronics

The invention relates to a low-power design optimization method for an instruction-level parallel (ILP) processor. The method comprises the steps of analyzing a hardware resource and parallelism demand information of each part of an input application program by utilizing a compiler, and obtaining basic blocks of the application program as well as a control flow graph (CFG) and loop hierarchy trees (LHTs), which are formed by the basic blocks; identifying regional cores; expanding a region, combining the residual basic blocks in the region, finding out the regional cores directly connected with the residual basic blocks, comparing executive frequencies of edges connecting the regional cores, finding out the edge with the maximum executive frequency, and combining the basic block connected with the maximum edge in the regional cores until the residual basic blocks do not exist; and re-scheduling the application program, scheduling each region by using the set parallelism, inserting a power gating instruction before executing each region, and turning off idle hardware resources to reduce electric leakage power consumption. According to the method, the influence of the electric leakage power consumption on the working performance of the processor can be reduced and the utilization rate of the hardware resources in the ILP processor can be increased.

Owner:TIANJIN UNIV

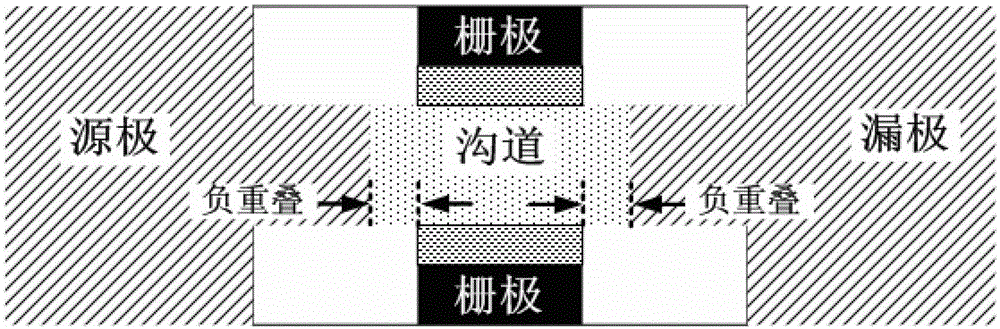

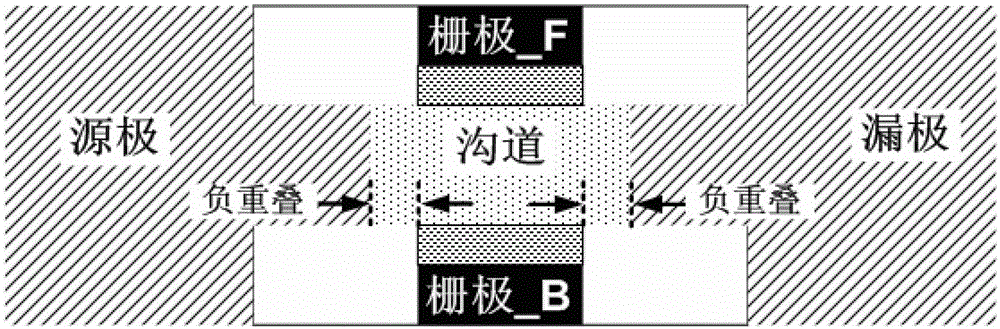

Static random access memory with asymmetric transistors and its control method

ActiveCN103489914BEnhanced read stabilityImprove data writing performanceDigital storageSemiconductor devicesStatic random-access memoryNon symmetric

The invention discloses a non-symmetric transistor, a static random access memory with the non-symmetric transistor, and a control method of the static random access memory. The non-symmetric transistor comprises a first doped region at a first end of a transistor and a second doped region at a second end of the transistor, with the second end being opposite to the first end in a first direction, and further comprises a channel region between the first doped region and the second doped region, and a grid electrode disposed on the channel region. The first doped region and the second doped region are doped with impurities of first type. The magnitude of the conducting current from the first end to the second end of the transistor is different from that from the second end to the first end. According to the invention, the data reading stability is improved, the data writing ability is improved and the electric leakage power consumption is reduced in the data access process.

Owner:THE HONG KONG UNIV OF SCI & TECH

Circuit and control method for reducing leakage current of sram storage array

ActiveCN111863070BLower the actual data hold voltageReduce leakage power consumptionDigital storageTerminal voltageHemt circuits

The invention discloses a circuit and a control method for reducing the leakage current of an SRAM storage array, comprising a storage array power supply voltage control module, a storage array ground terminal voltage control module and a storage array; The terminal control module realizes the control of the voltage of the power supply terminal and the ground terminal of the storage array, which can reduce the actual data retention voltage of the storage unit, thereby reducing the leakage power consumption of the SRAM in the data retention state. And the function of adjusting the data retention voltage value of the memory cell is realized by controlling different adjustment signals to meet different design requirements. The invention can effectively reduce the leakage current of the storage array in the data retention state of the SRAM, and in the storage system realized by the SRAM, the necessary SRAM can keep the data with low leakage overhead, and the other SRAMs can completely turn off the power.

Owner:NANJING LOW POWER IC TECH INST CO LTD

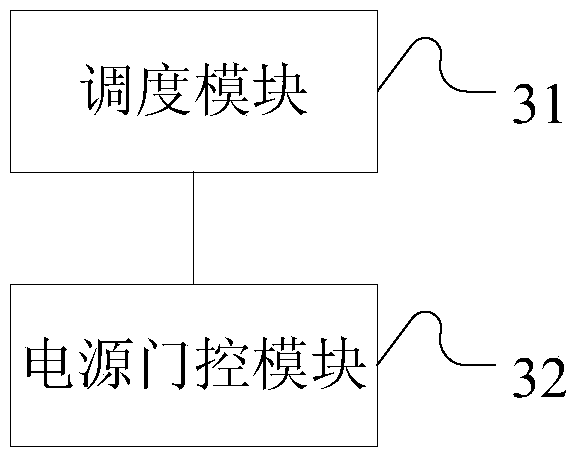

Power gating method and device

ActiveCN103677213BReduce leakage power consumptionPower supply for data processingElectricityIdle time

Owner:LOONGSON TECH CORP

Feedthrough signal transmission device/method and related feedthrough signal transmission circuit

InactiveCN106301340BReduce leakage power consumptionLogic circuit interface arrangementsElectricityControl cell

The present invention relates to a feed-through signal transmission device / method and a related feed-through signal transmission circuit. The device comprises feed-through signal transmission circuits, each feed-through signal transmission circuit includes at least one subcircuit, wherein when the subcircuit executes the feed-through signal transmission, the subcircuit keeps the power-on state, and the subcircuit includes a relay for feed-through normal opening and a normally opening control cell. When the subcircuit executes the feed-through signal transmission, the power-on state of the subcircuit is kept, wherein the subcircuits of the feed-through signal transmission circuit are located at the position of the single silicic chip areas based on the grids. The feed-through signal transmission device / method and the related feed-through signal transmission circuit can perform cutting-off according to the requirement so as to greatly reduce the electric leakage power loss.

Owner:MEDIATEK INC

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com