Wafer-level electric leakage reducing ESD structure

A wafer-level, resistive technology, applied to circuits, emergency protection circuit devices for limiting overcurrent/overvoltage, transistors, etc. problems, to achieve the effect of suppressing sub-threshold current, ensuring ESD performance, and reducing circuit power consumption

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

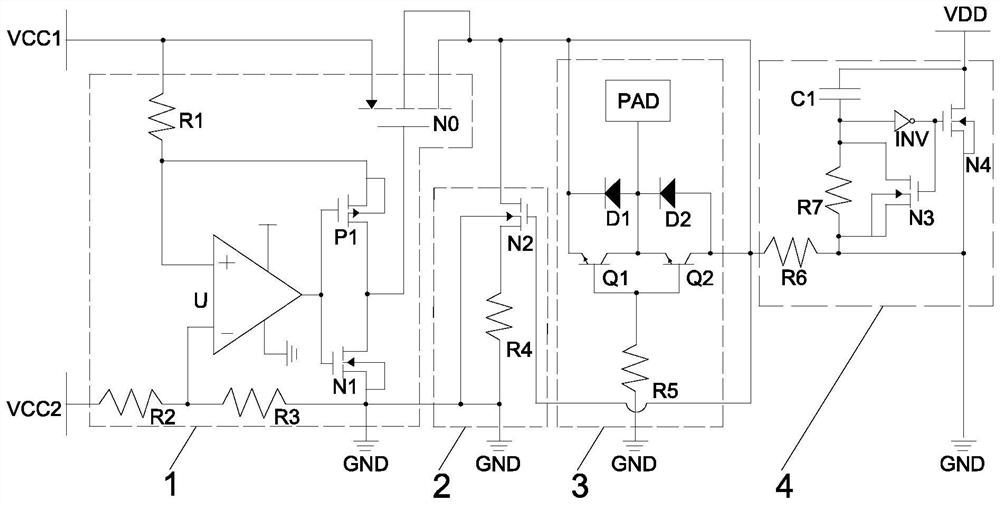

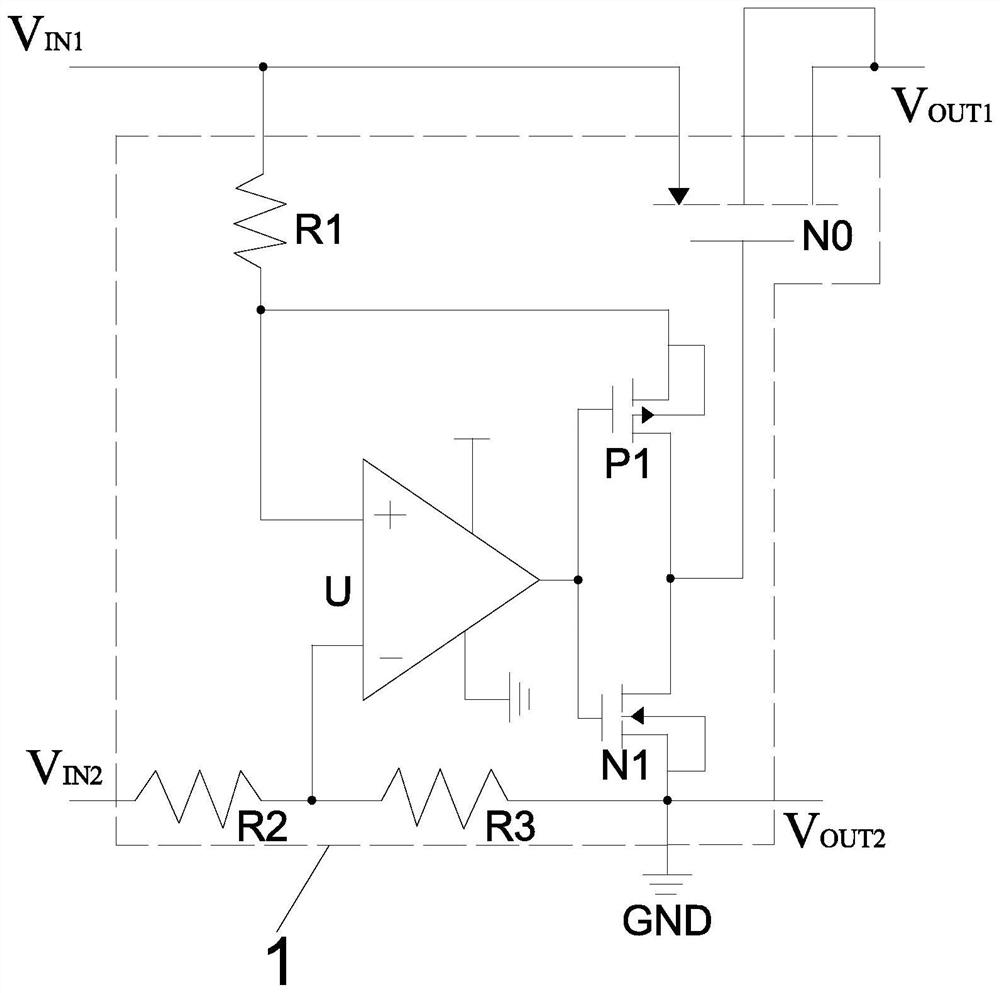

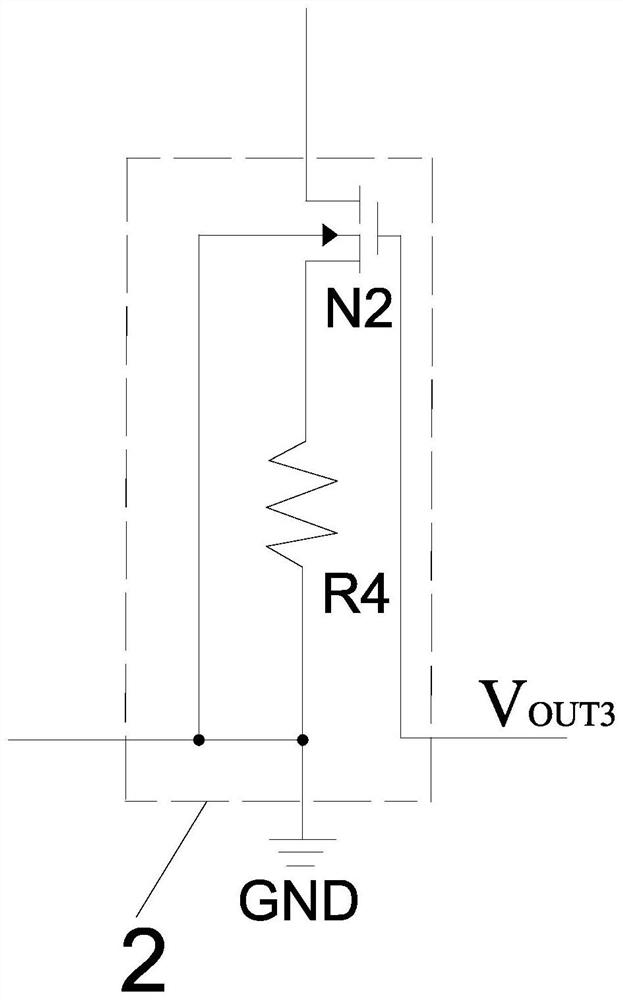

[0027] In order to further illustrate the various embodiments, the present invention provides accompanying drawings, which are part of the disclosure of the present invention, and are mainly used to illustrate the embodiments, and can be used in conjunction with the relevant descriptions in the specification to explain the operation principles of the embodiments. For these, those of ordinary skill in the art will understand other possible implementations and the advantages of the present invention. Components in the figures are not drawn to scale, and similar component symbols are generally used to represent similar components.

[0028] According to an embodiment of the present invention, an ESD structure with reduced leakage at the wafer level is provided.

[0029] The present invention will now be further described with reference to the accompanying drawings and specific embodiments, such as Figure 1-Figure 5 As shown, the wafer-level ESD structure for reducing leakage acco...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More