Small-size SoC ultra-low power consumption control circuit and method

An ultra-low power consumption, control circuit technology, applied in the field of system-on-chip, can solve the problems of minimizing power consumption, affecting user experience, slow wake-up speed, etc., achieving low leakage power consumption, eliminating logic dynamic power consumption, and accelerating wake-up effect of speed

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

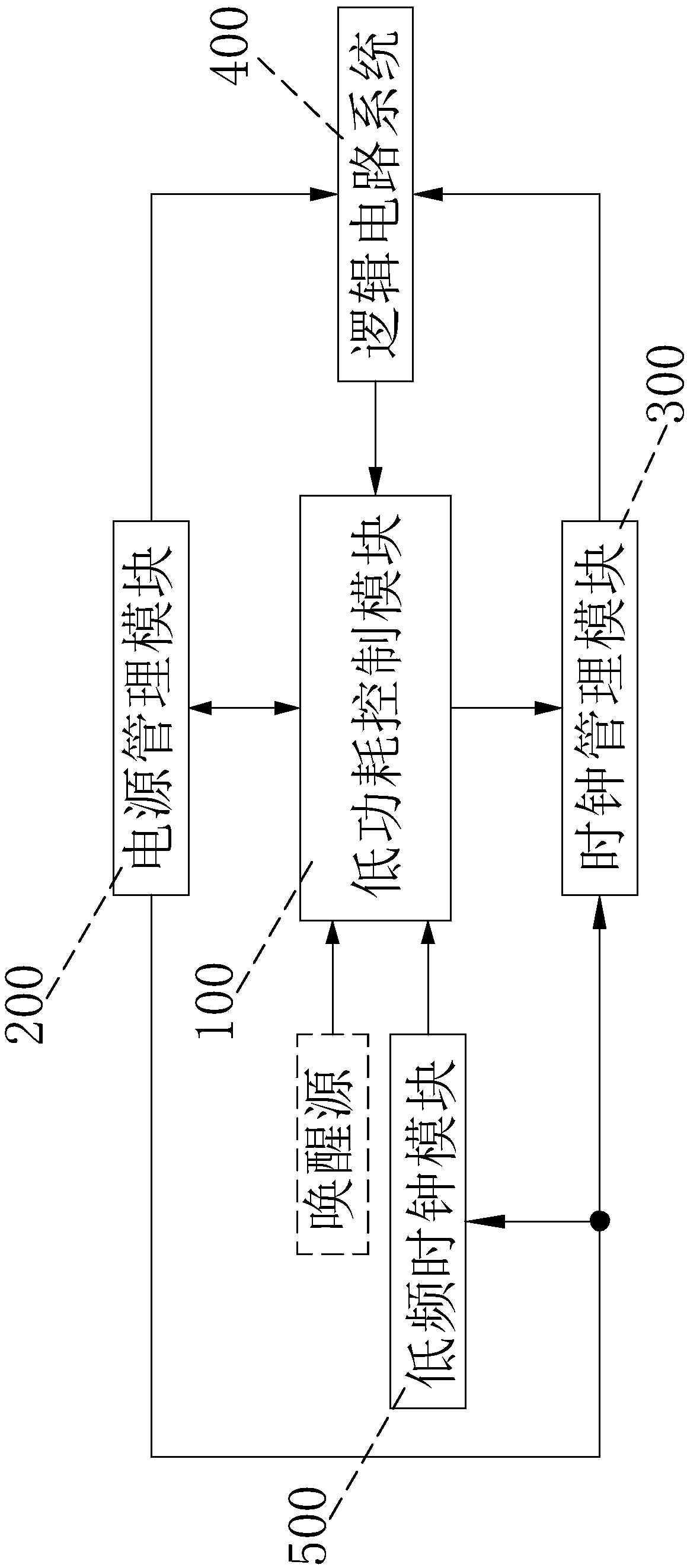

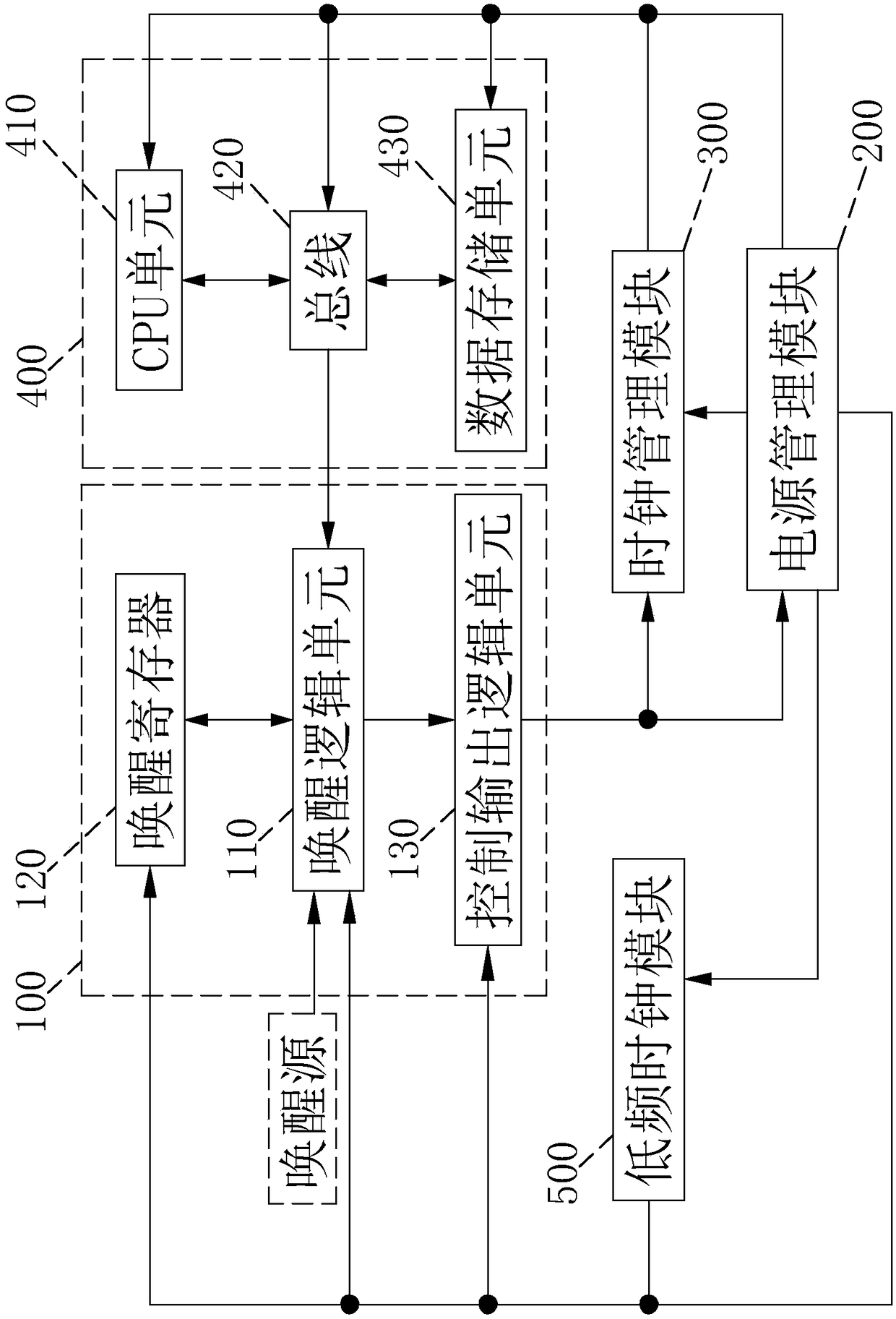

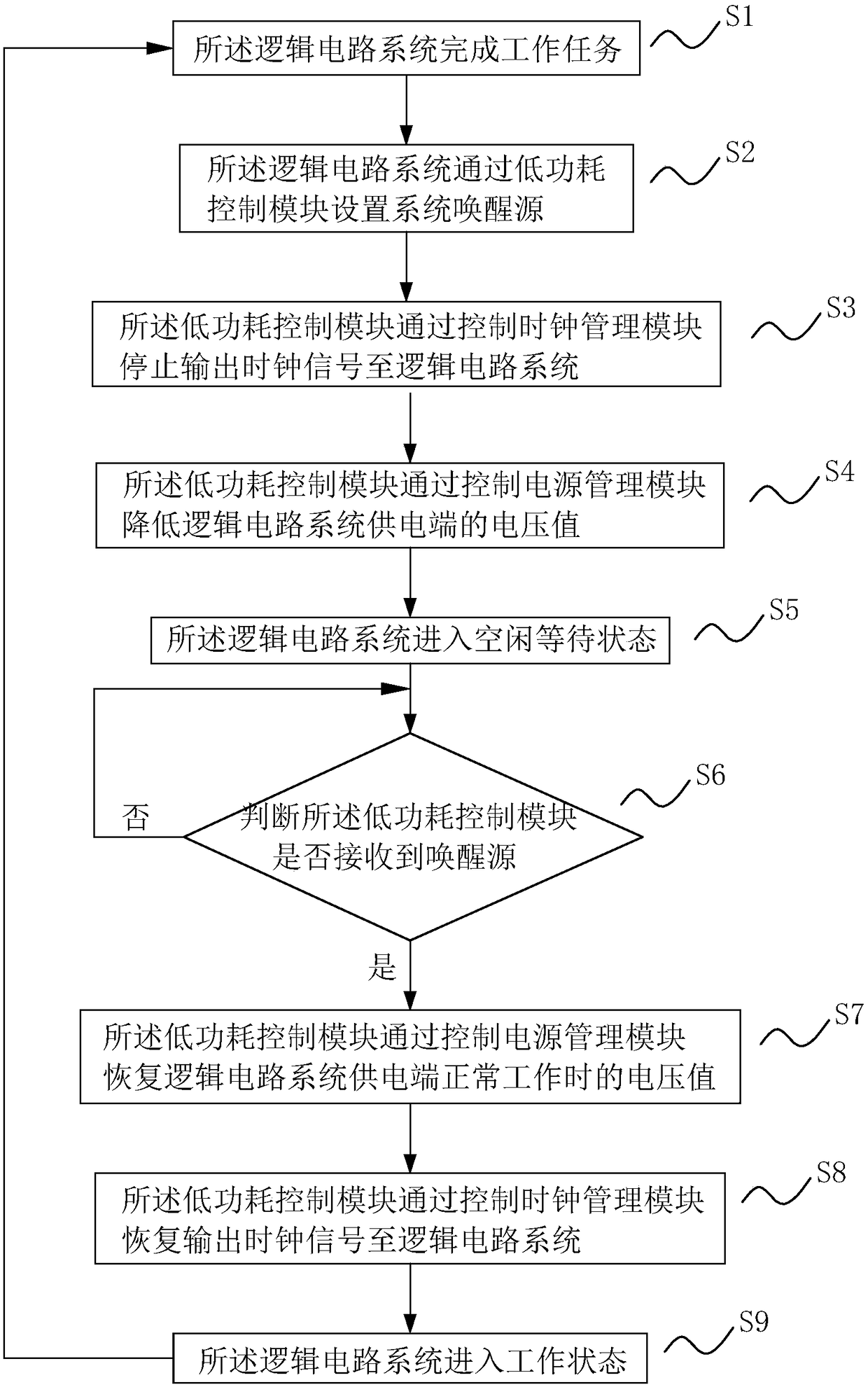

[0027] refer to figure 1 , a basic circuit schematic diagram of a small SoC ultra-low power consumption control circuit of the present invention, including a logic circuit system 400, a low power consumption control module 100, a power management module 200, a clock management module 300 and a low frequency clock module 500, the The input end of the low power consumption control module 100 is connected to the logic circuit system 400, and the output end of the low power consumption control module 100 is respectively connected to the power management module 200 and the clock management module 300, and the logic circuit system 400, the low power consumption The power supply terminals of the control module 100, the clock management module 300 and the low-frequency clock module 500 are all connected to the power management module 200, the clock signal terminal of the logic circuit system 400 is connected to the clock management module 300, and the low-power control module 100 The ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More