Parallelism degree adjustment algorithm for reducing power consumption of instruction-level parallel processor

A processor, instruction-level technology, applied in the field of low-power design optimization algorithms, which can solve problems such as large extra energy consumption, not so high expectations for speed, and attracting their attention.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

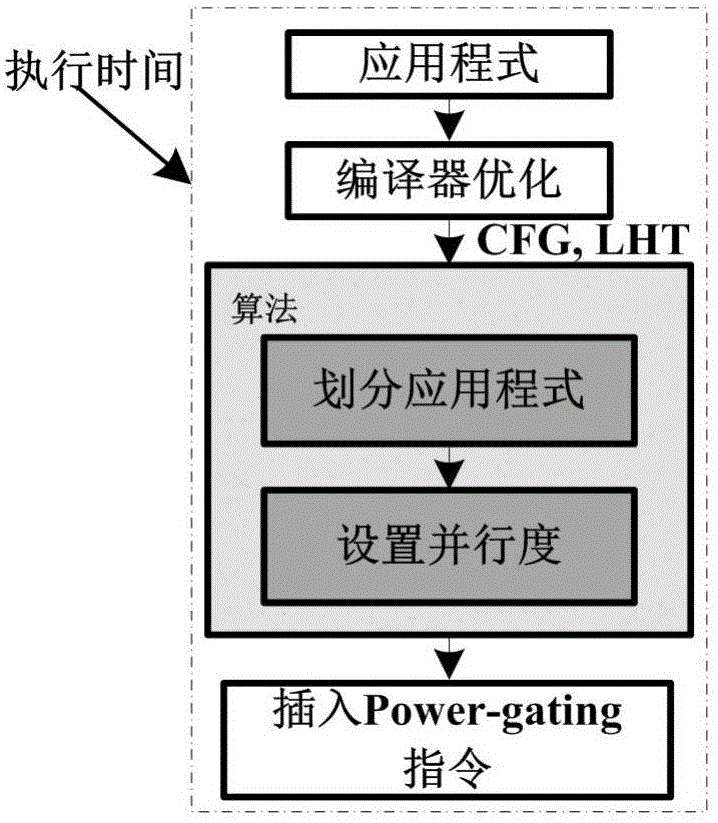

[0021] The present invention utilizes relevant compiler optimization algorithms to analyze application program execution time, hardware demand, and parallelism demand, and adjusts the parallelism of each area, so that the ILP processor can execute different application programs according to the execution time. Limit, "automatically" adjust the degree of parallelism, and ultimately achieve the highest energy efficiency and the lowest leakage power consumption.

[0022] figure 1 The workflow of the compiler in the whole solution is shown, and the main technical solutions are as follows:

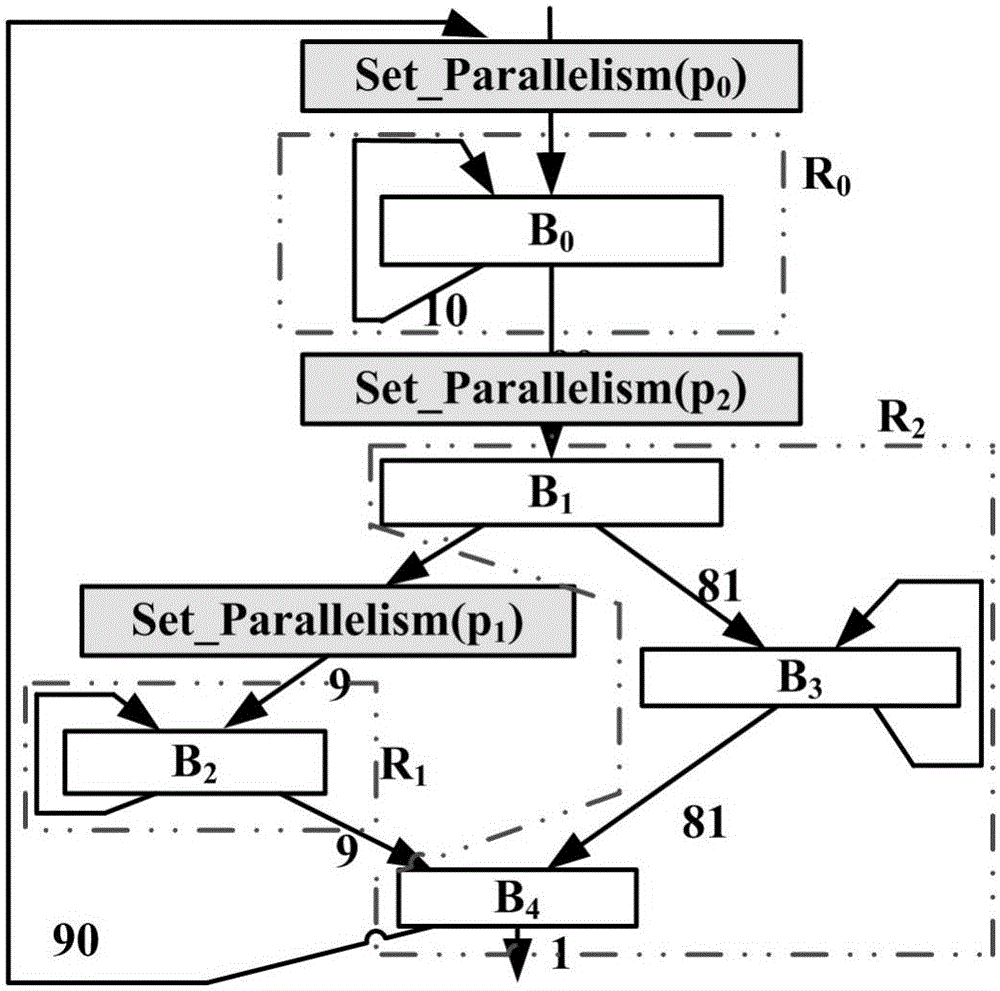

[0023] (1) Use the compiler to analyze information such as hardware resources and parallelism requirements of each part of the input application program, and obtain the control flow graph (Control Flow Graph, CFG) and loop hierarchy trees (LoopHierarchy Trees, LHTs) of the application program ;

[0024] (2) Divide the application program and divide the application program into different areas...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com