Low power consumption design method for SRAM (static random-access memory) type FPGA (field-programmable gate array)

A design method and low-power technology, applied in computing, special data processing applications, instruments, etc., can solve the problem of large impact on timing, affect circuit timing performance, and not further consider leakage power consumption, access logic and bypass logic and other issues to achieve the effect of reducing leakage power consumption

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0044] In order to make the objectives, technical solutions and advantages of the present invention clearer, the present invention will be further described in detail below with reference to the accompanying drawings. It should be understood that the specific embodiments described herein are only used to explain the present invention, but not to limit the present invention.

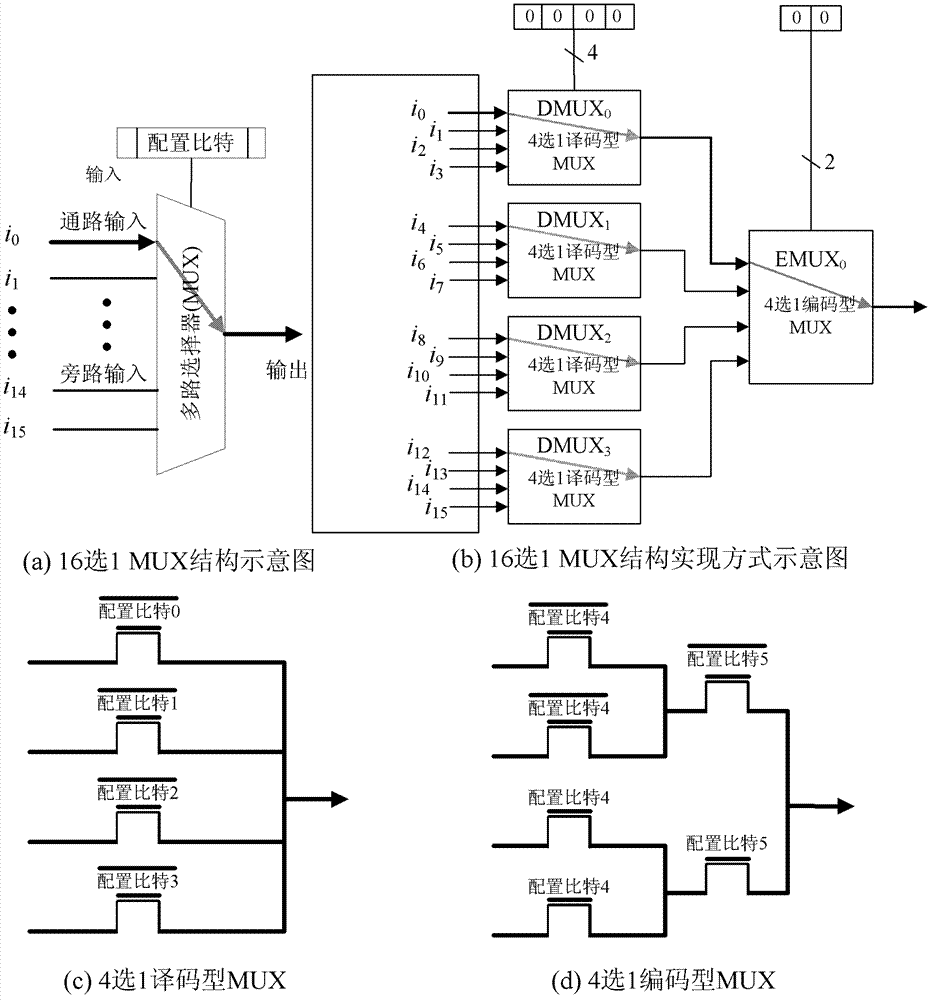

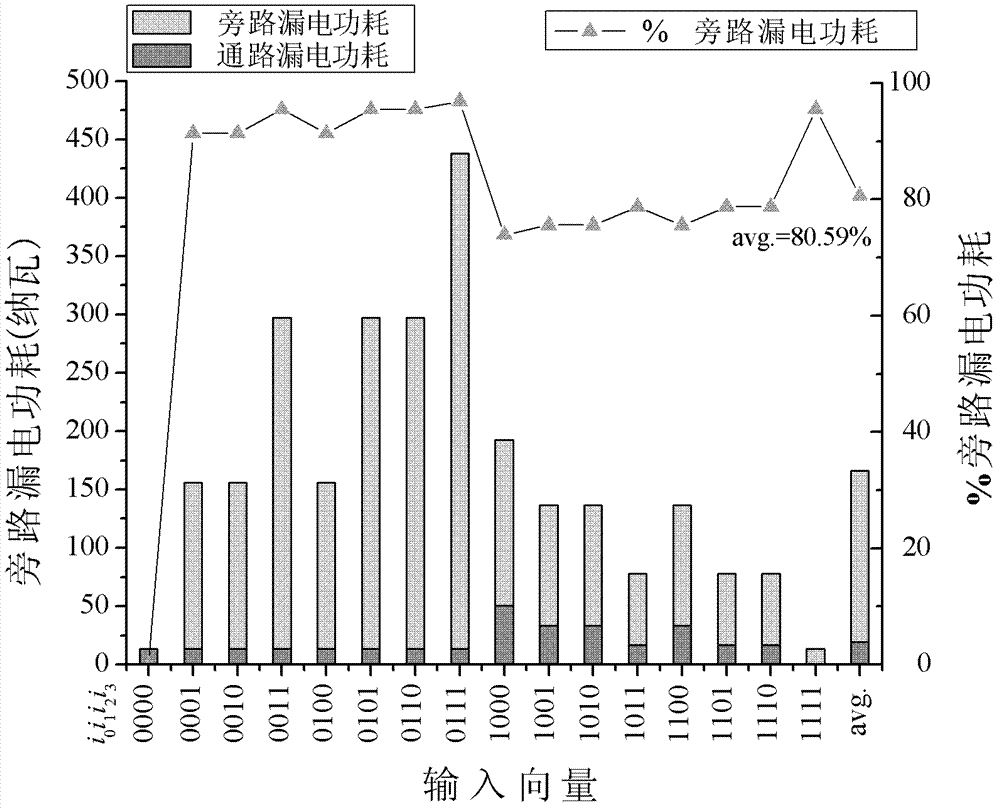

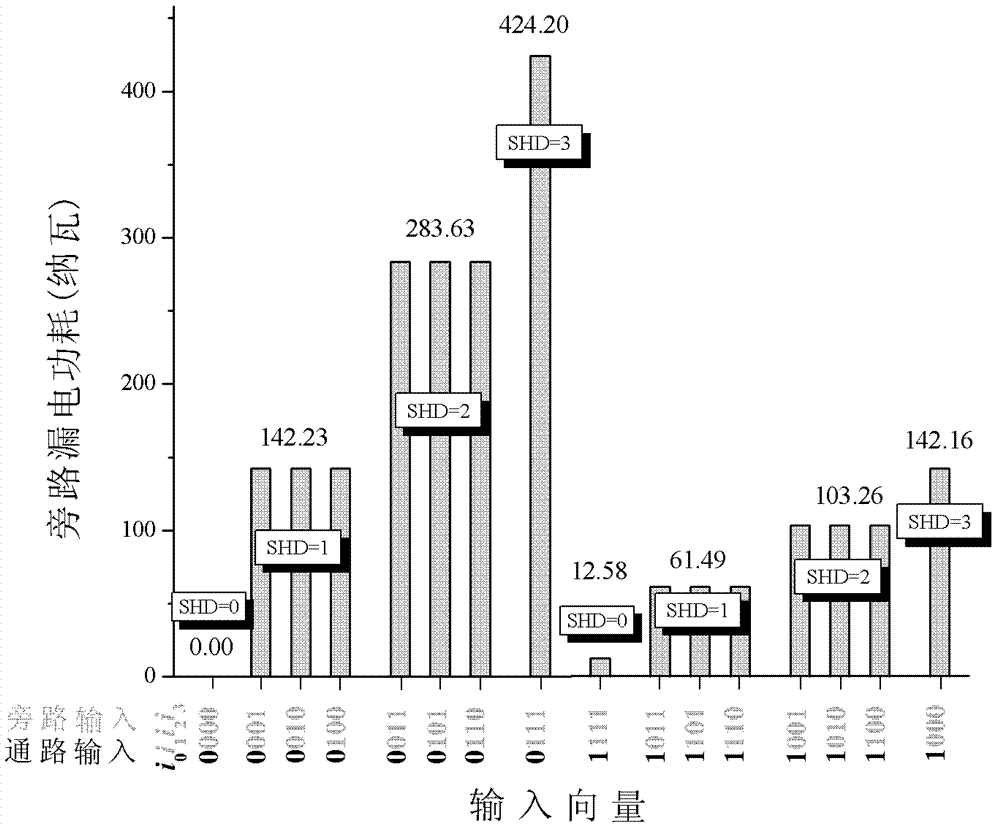

[0045] The SRAM-type FPGA is mainly composed of configurable logic modules and wiring resources. Configurable logic modules include look-up tables and flip-flops, etc., to realize the logic function of the circuit; connection resources include line segments of different lengths and switching modules connecting each line segment. The connection relationship between each line segment is realized by configuring the MUX (multiplexer) in the switching module. In the process of circuit implementation, the signal is connected from one input end of the MUX to the output end of the MUX, which is called a channel,...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com