Binary image lossless compression and decompression IP core based on FPGA and application

A binary image, lossless compression technology, applied in the direction of image communication, electrical components, etc., can solve the problem of occupying more CPU resources, achieve good compression effect, fast decompression speed, and good application prospects

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

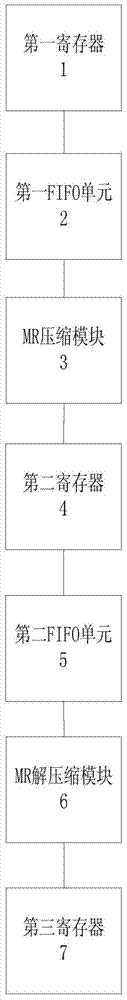

[0020] Please refer to figure 1 , an FPGA-based binary image lossless compression and decompression IP core and its application.

[0021] An FPGA-based binary image lossless compression and decompression IP core, which includes,

[0022] a register, the register is used to store binary image data;

[0023] FIFO unit, the FIFO unit is used to read the binary image data in the register;

[0024] MR compression module, the compression module reads the original binary image data in the register through the FIFO unit, and compresses the original binary image data read;

[0025] MR decompression module, the decompression module reads the compressed binary image data in the register through the FIFO unit, and decompresses the read compressed binary image data. The MR compression module is implemented by VHDL language, wherein the MR code is a two-dimensional code, the first line of the MR code adopts MH code, and the second line of the MR code is compressed according to the data o...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More