Integrated circuit high-voltage pin connectivity testing method

A technology of connectivity testing and high-voltage pins, which is applied in the direction of measuring electricity, measuring devices, measuring electrical variables, etc., can solve the problems that high-voltage pins cannot be tested, and achieve the effect of complete mid-test technology

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

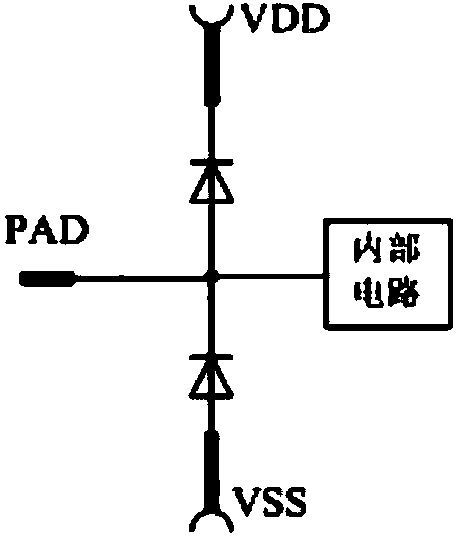

[0017] In order to make the object, technical solution and advantages of the present invention more clear, the present invention will be further described in detail below in conjunction with the accompanying drawings and embodiments. It should be understood that the specific embodiments described here are only used to explain the present invention, not to limit the present invention.

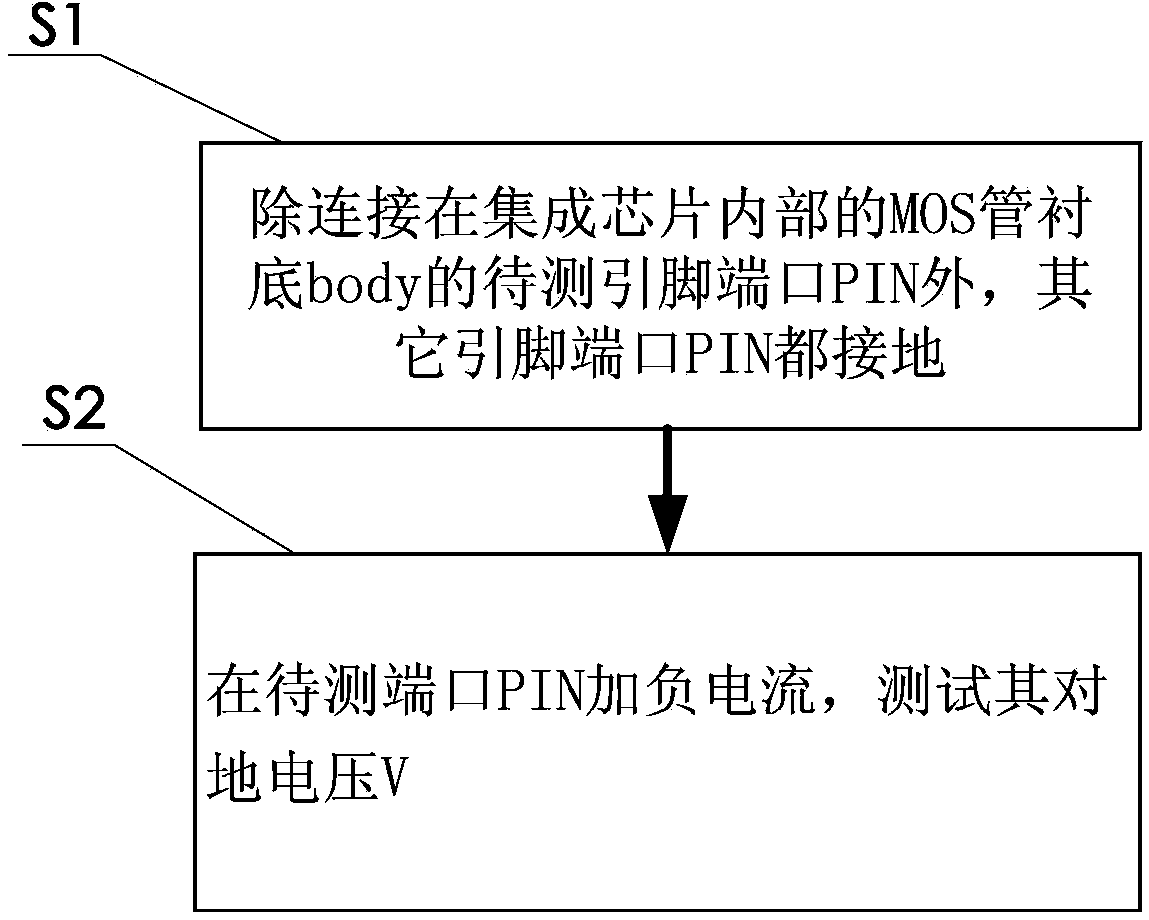

[0018] figure 1 A flow chart of a method for testing the continuity of an integrated circuit high-voltage pin according to the present invention is shown.

[0019] refer to figure 1 ,Such as figure 1 As shown, a method for testing the continuity of an integrated circuit high voltage pin comprises the following steps:

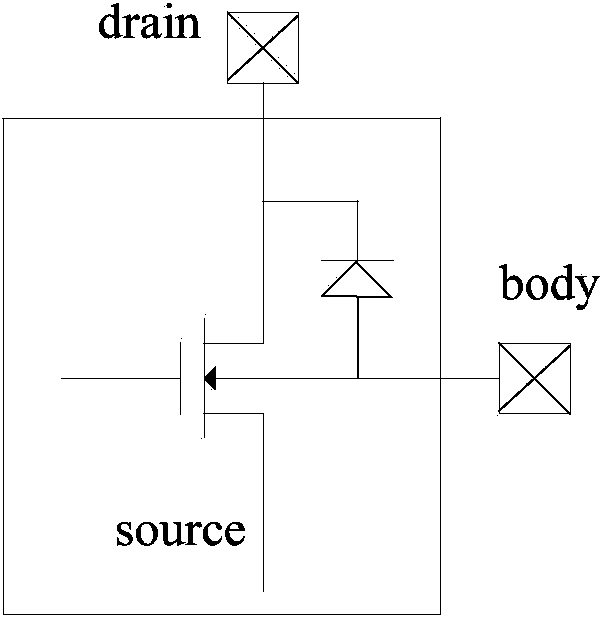

[0020] S1, except for the pin port PIN to be tested connected to the MOS tube substrate body inside the integrated chip, all other pin port PINs are grounded;

[0021] S2, apply a negative current to the port PIN to be tested, and test its ground voltage V.

[0022] The step ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com