Chip arrangement method for improving chip simultaneous testing

A chip and chipset technology, applied in the direction of measuring electricity, measuring devices, measuring electrical variables, etc., can solve the problems of long test time, difficult to make probe cards, long test time, etc., and achieve the effect of reducing test costs

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0021] The chip arrangement method for improving chip simultaneous testing of the present invention comprises the steps of:

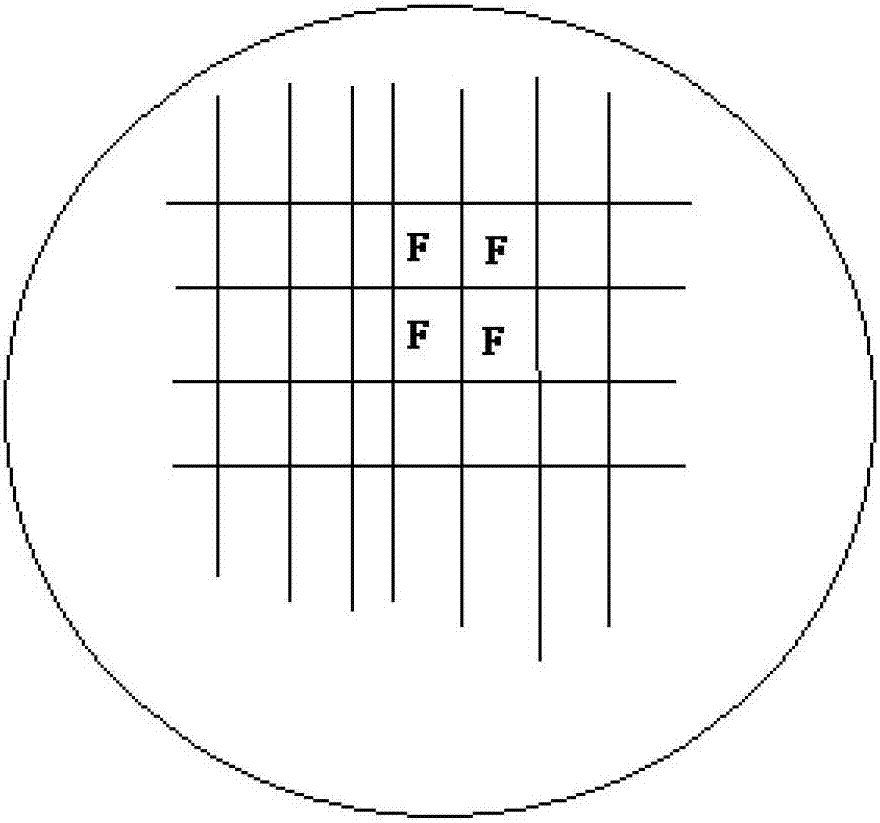

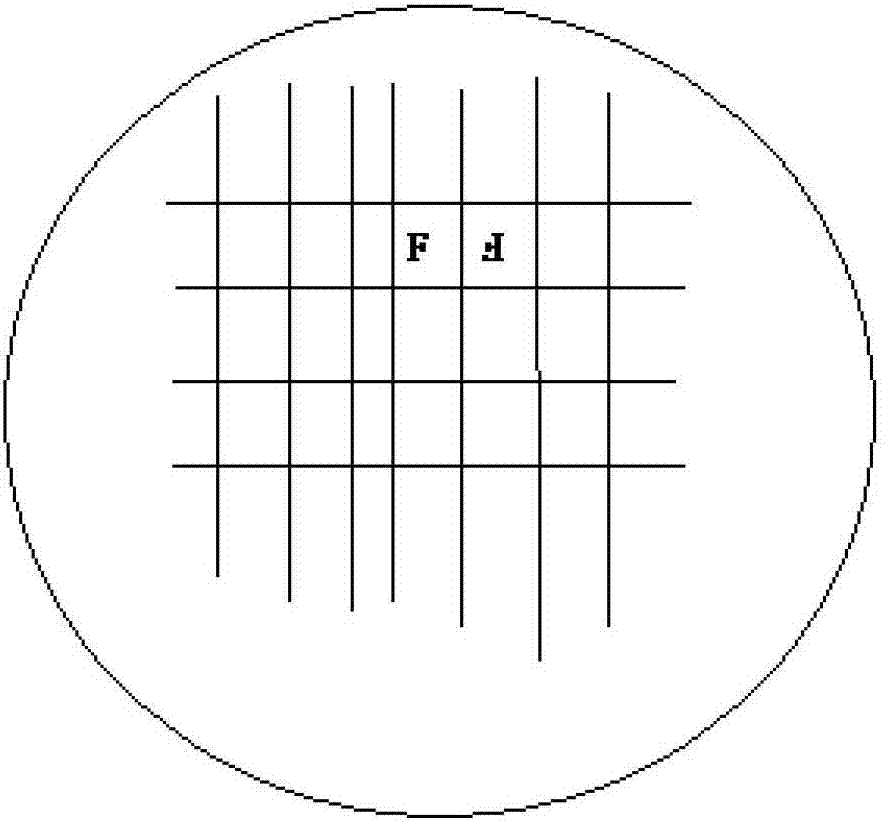

[0022] 1) Place the chip on the silicon wafer according to the mapping method (such as the symmetrical rotation method) (such as figure 2 shown);

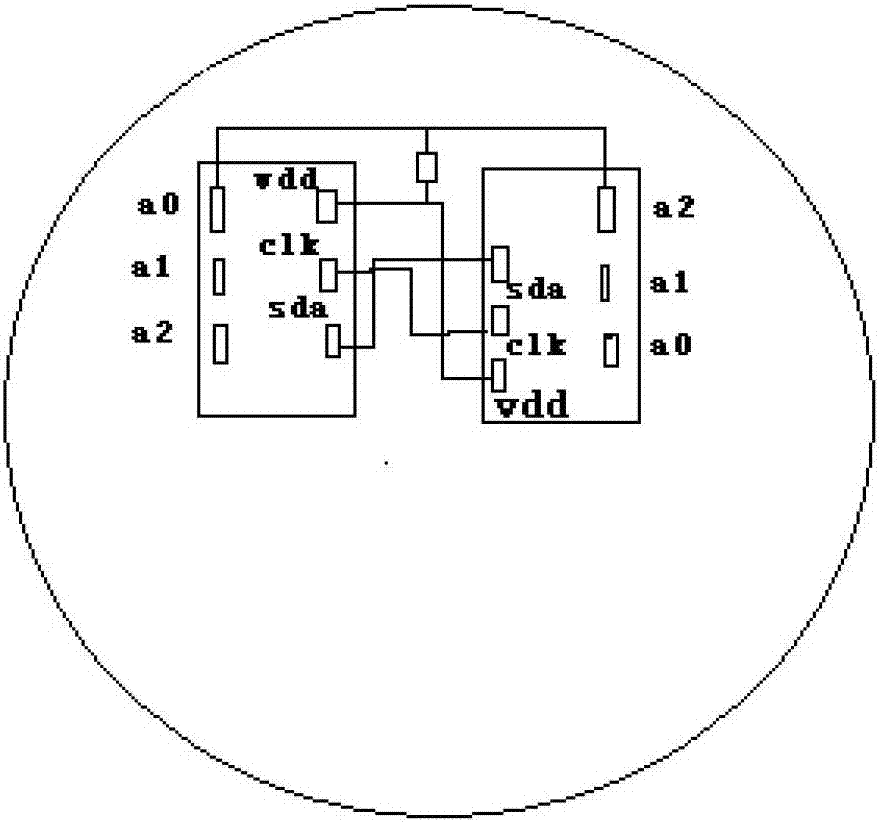

[0023] 2) Connect the PADs of adjacent chips together to form a chipset, for example, as image 3 As shown, through the connection of two chips, the two chips are combined into a chipset;

[0024] 3) The probe card only needs to use the chip set connected together as a whole chip (large chip), and when the probe pricks the needle, only one of the chips in the chip set that constitutes step 2) is pricked;

[0025] 4) Set the address lines of each chip in a chipset to different levels, and the chip address lines are connected to different connections (that is, the chip address lines are connected in different ways);

[0026] 5) Send different instructions through different address information of the chip (...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More