Asynchronous chip simultaneous test method

An asynchronous, chip technology, used in digital circuit testing, electronic circuit testing, etc., can solve the problems of small number of simultaneous tests and long data processing time, and achieve the effect of increasing the number of simultaneous tests, saving test costs, and shortening test time.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

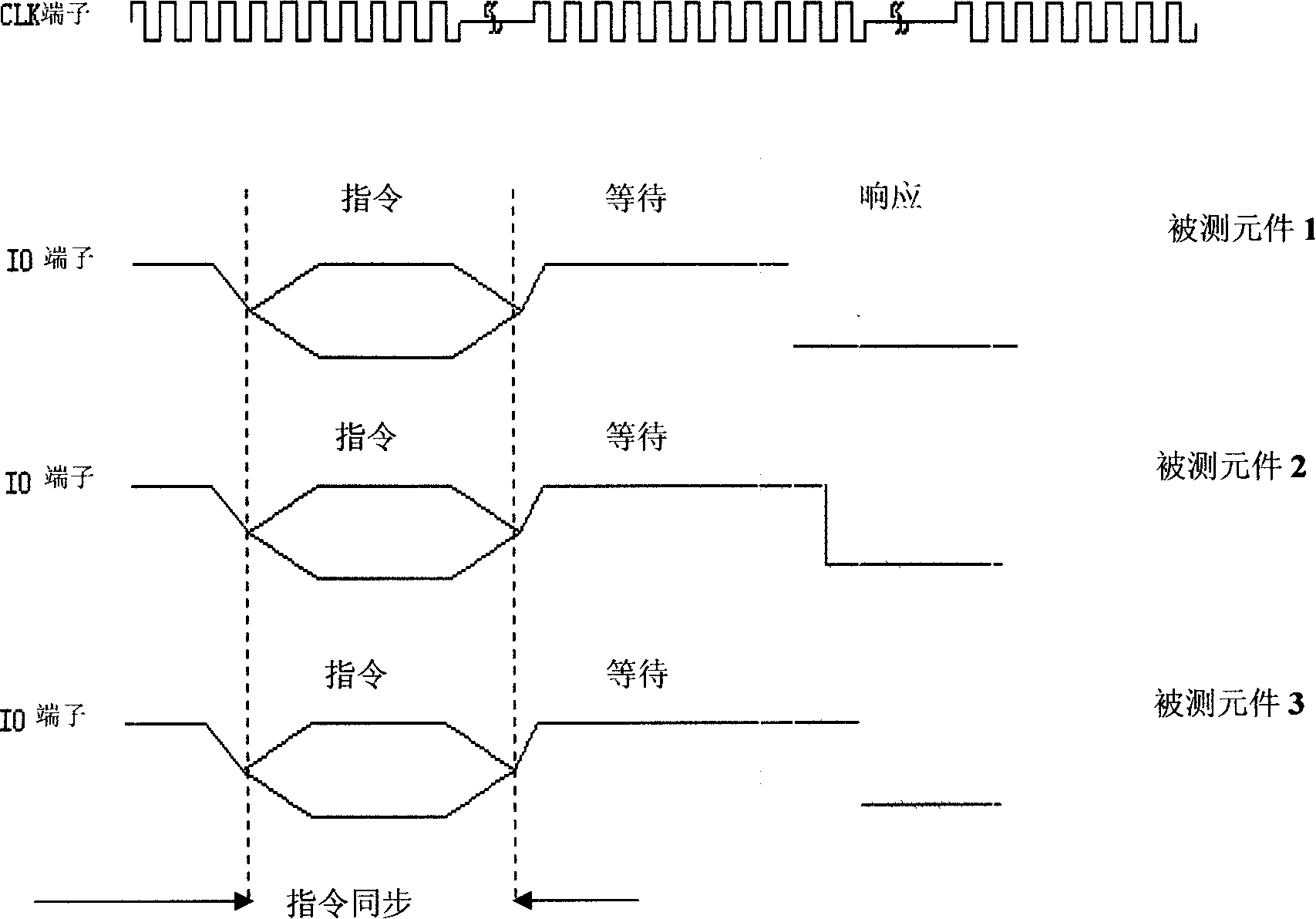

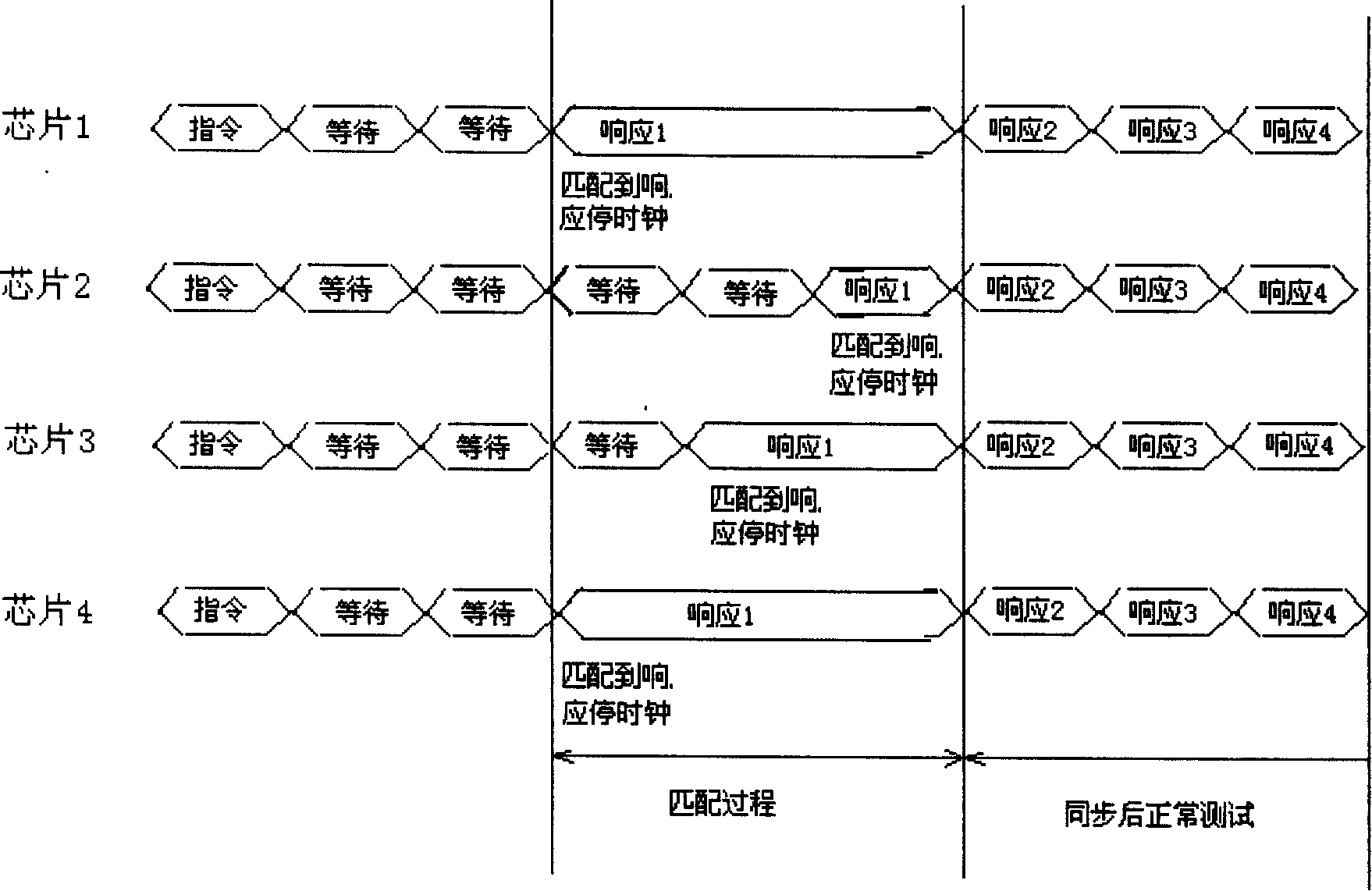

[0011] First, match the first output of the asynchronous signal when testing multiple chips at the same time. For example, in the IS7816 protocol, when responding to 9000H, first match the "0" of the first clock output of the first start bit, such as figure 1 As shown, when chip 1 matches the first bit of data, the state of the test channel remains unchanged, mainly keeping the clock signal unchanged.

[0012] At this time, due to the stop of the clock signal, the chip 1 under test cannot output the next data. When the tester matches all the output first bit signals of chip 2, chip 3, and chip 4 within a certain period of time, it continues to run the test vector. Chips that have not been matched during this period of time will be treated as unqualified, while other matched chips have been kept in sync at this time, as long as they are compared sequentially.

[0013] If the product test of ISO7816 protocol communication is required, the synchronous control of multiple asynchr...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More