Hot redundancy interlocking subsystem and main and standby switching method thereof

A master-standby switching and subsystem technology, applied in the field of interlocking architecture, can solve problems such as the inability to eliminate software common-mode faults, and achieve the effect of avoiding performance defects and eliminating common-mode faults

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0025] The present invention will be further described below in conjunction with accompanying drawing.

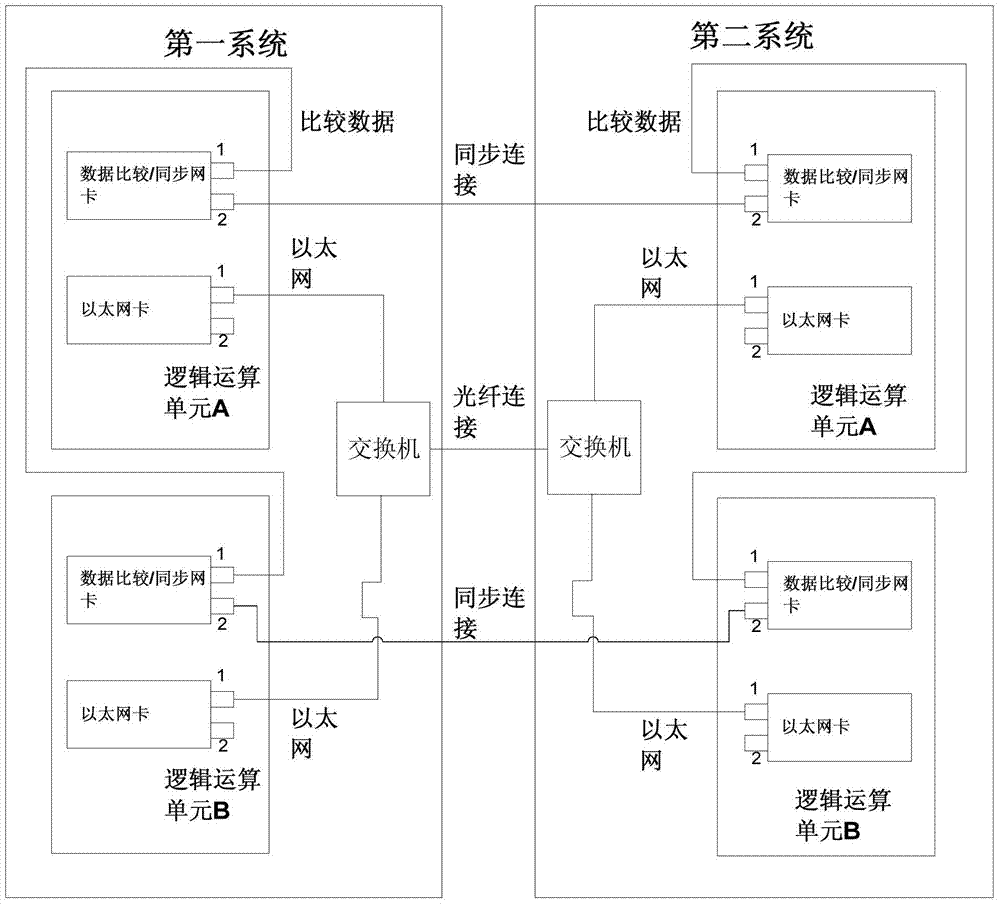

[0026] see figure 1 , the thermal redundancy interlocking subsystem of the present invention includes the same first system and second system,

[0027] The first system and the second system are connected synchronously to compare the I / O status and received information, and perform hot redundancy switching. Both the first system and the second system include a switch, and two CPUs with heterogeneous hardware (ie figure 1 In the logic operation unit A, logic operation unit B). The two CPUs run two sets of different software with differences to realize system synchronization and hot standby switching. In this embodiment, the two CPUs are respectively Intel and Cyrex products, and their running speeds and main frequencies are different, and each unit runs software compiled by different compilers.

[0028] figure 1 , each CPU includes: data comparison / synchronization netwo...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More