Wafer manufacturing scheduling method and scheduling system in semiconductor integrated circuit production

An integrated circuit and scheduling system technology, applied in the field of wafer manufacturing scheduling method and scheduling system in the production of semiconductor integrated circuits, can solve the problem that the subjective judgment of production managers has great influence, affects production efficiency, product date, and cannot effectively control product delivery. problems such as the urgency of the goods to achieve the effect of improving production efficiency

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0017] In order to further understand the technical content of the present invention, specific embodiments are given and described as follows in conjunction with the accompanying drawings.

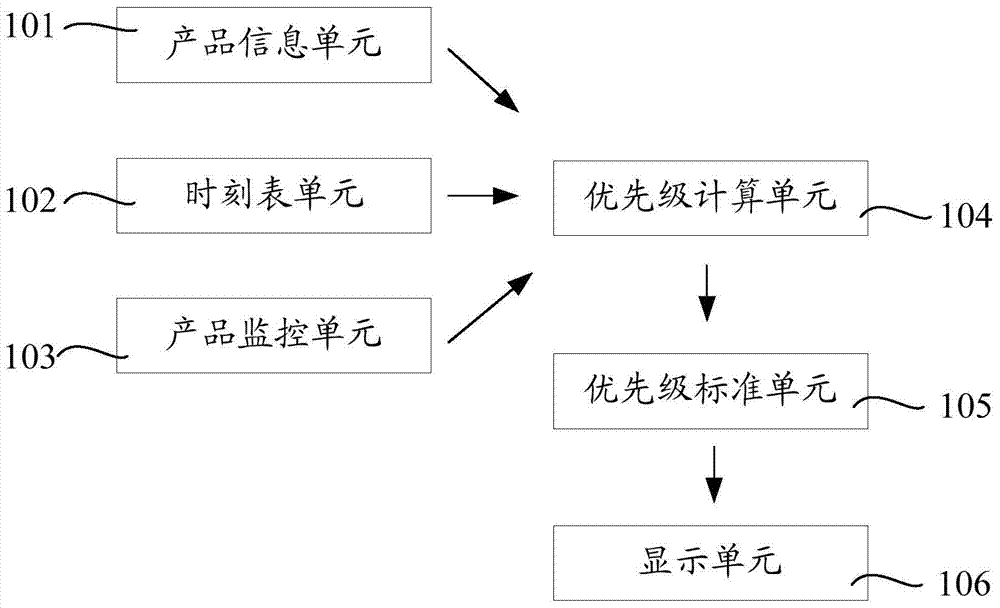

[0018] see figure 1 The schematic diagram of the structure of the scheduling system in the production of semiconductor integrated circuits is shown, and the scheduling system in the production of semiconductor integrated circuits includes a product information unit 101, a time table unit 102, a product monitoring unit 103, and a priority calculation unit connected to the software and hardware of the application computer. Unit 104 , priority standard unit 105 , and display unit 106 .

[0019] The product information recording unit 101 is used to store relevant data of the process flow corresponding to different products, for example, including the number of stations that the product needs to pass through, the theoretical process time of each station, the number of layers required for photol...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More