A distributed data synchronous acquisition device and method

A distributed data and synchronous acquisition technology, applied in signal transmission systems, instruments, electrical signal transmission systems, etc., to achieve the effect of expanding the scope of application, expanding the number of points to be measured, and stabilizing performance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

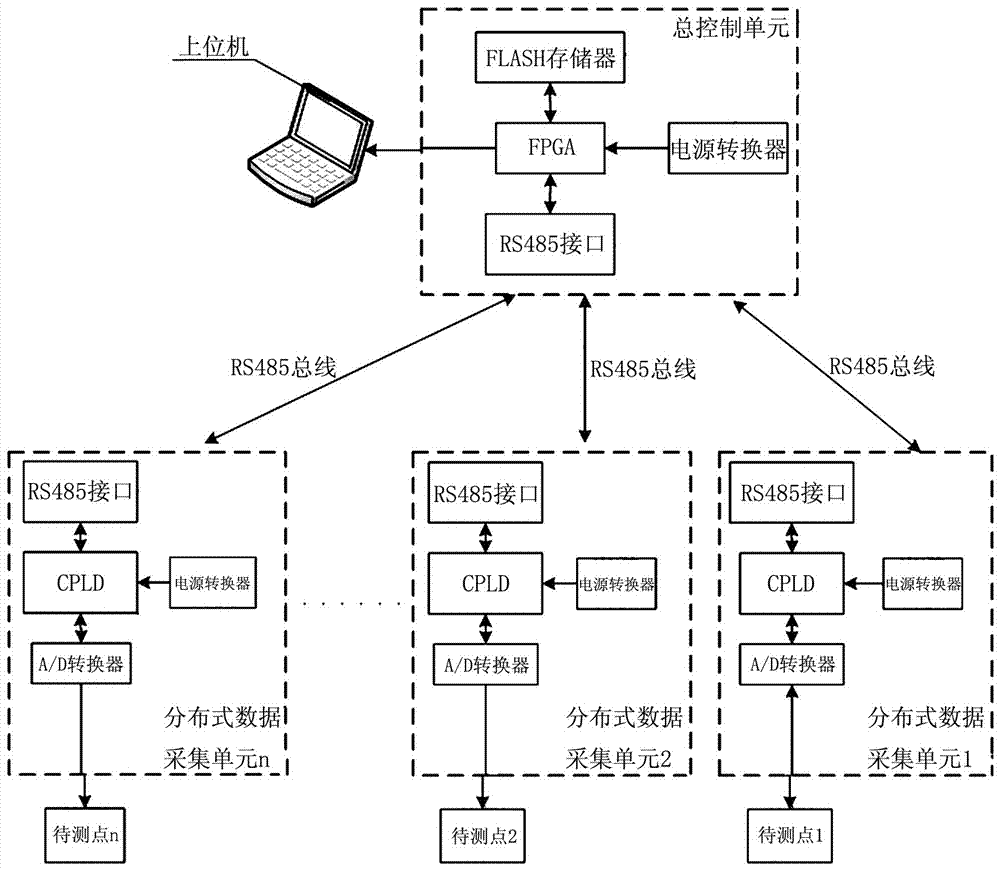

[0016] A distributed data synchronous acquisition device, comprising a host computer, a total control unit, an RS485 bus, and a distributed data acquisition unit;

[0017] The total control unit includes an FPGA, a FLASH memory, a power converter, and an RS485 interface;

[0018] The number of the distributed data acquisition units is n; each distributed data acquisition unit includes a CPLD, an A / D converter, a power converter, and an RS485 interface;

[0019] Wherein, the output end of the FPGA is connected with the input end of the upper computer; the FLASH memory is connected bidirectionally with the FPGA; the output end of the power converter of the total control unit is connected with the input end of the FPGA; the RS485 interface of the total control unit is bidirectionally connected with the FPGA; n A / D converters are connected to n CPLDs in one-to-one correspondence with two-way connections; the output terminals of the power converters of n distributed data acquisitio...

Embodiment 2

[0026] A distributed data synchronous acquisition device, comprising a host computer, a total control unit, an RS485 bus, and a distributed data acquisition unit;

[0027] The total control unit includes an FPGA, a FLASH memory, a power converter, and an RS485 interface;

[0028] The number of the distributed data acquisition units is n; each distributed data acquisition unit includes a CPLD, an A / D converter, a power converter, and an RS485 interface;

[0029] Wherein, the output end of the FPGA is connected with the input end of the upper computer; the FLASH memory is connected bidirectionally with the FPGA; the output end of the power converter of the total control unit is connected with the input end of the FPGA; the RS485 interface of the total control unit is bidirectionally connected with the FPGA; n A / D converters are connected to n CPLDs in one-to-one correspondence with two-way connections; the output terminals of the power converters of n distributed data acquisitio...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More