Quantitative analysis method for heavy-ion single-particle multi-bit upset effect of device

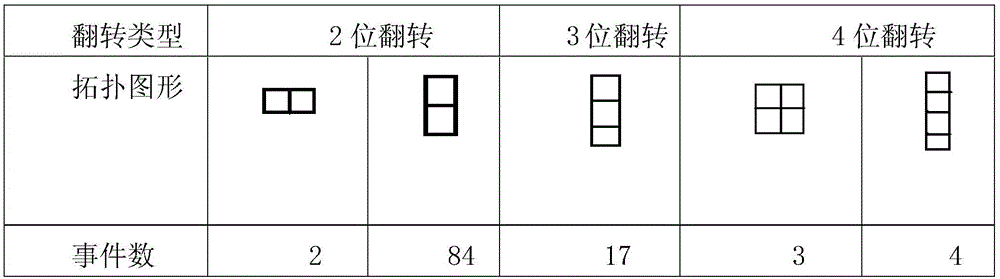

A multi-bit flip effect, single-particle flip technology, applied in instruments, special data processing applications, electrical digital data processing, etc. Can not objectively reflect the storage unit and other issues

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0060] specific implementation

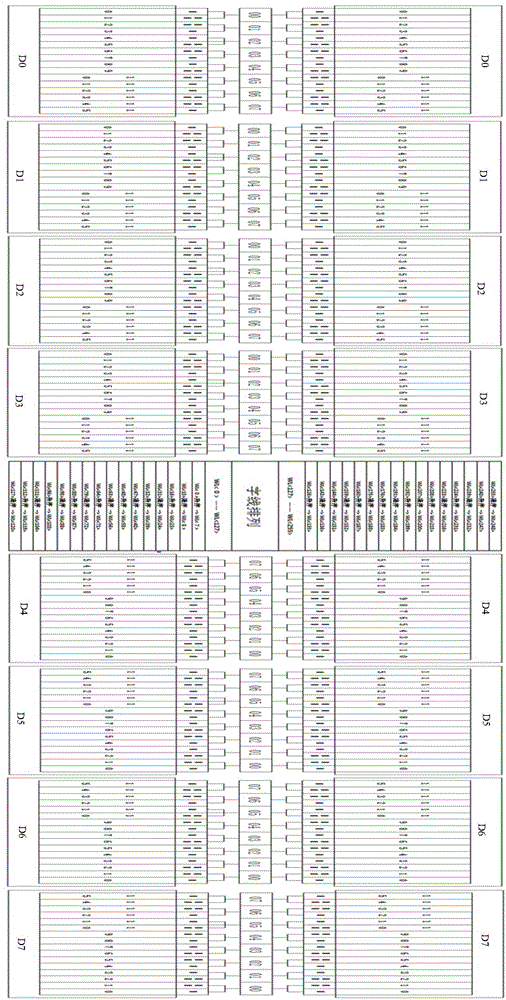

[0061] Taking a certain static memory H328X circuit as an example, the specific implementation of the present invention will be described in detail in conjunction with the accompanying drawings. H328X is a synchronous single-port SRAM circuit with a storage capacity of 32K×8 bits and a total of 256Kbit. The following example is only used to illustrate the present invention , but not to limit the scope of the present invention.

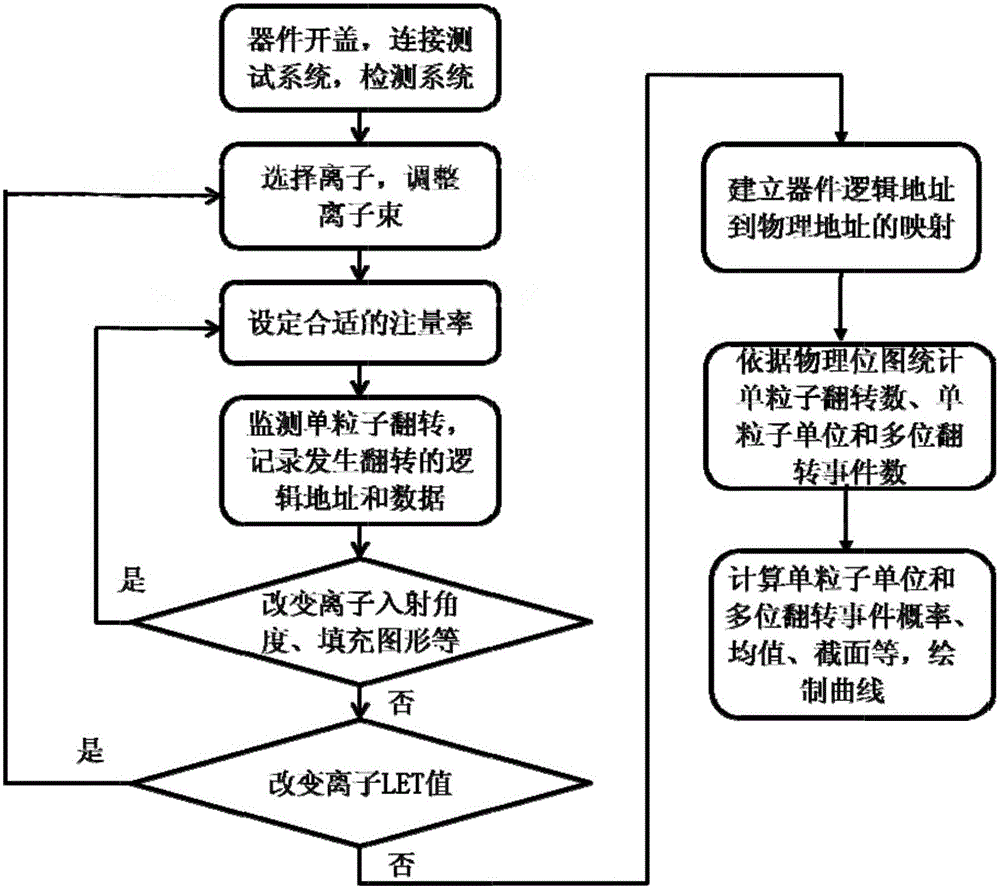

[0062] figure 1 It is a flow chart of the quantitative analysis method for the heavy ion single event multi-position flipping effect of the device of the embodiment of the present invention, combined with figure 1 , to describe this method in detail.

[0063] (1) Before the test, the sample is opened and the functional parameters are tested. After the test is passed, the sample is inserted on the PCB irradiation board, fixed at the test position by the sample holder, and aligned and positioned. Connect the test syste...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More