A Method of Optimizing the Power Consumption of Three-valued FPRM Circuit Using Exhaustive Method

An exhaustive method and circuit technology, applied in the direction of electrical digital data processing, special data processing applications, instruments, etc., can solve the problems of multi-valued RM circuit power consumption optimization technology that has not been studied.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

[0038] Embodiment one: a kind of ternary FPRM circuit power consumption optimization method utilizing exhaustive method, comprises the steps:

[0039] ①Establish the power consumption estimation model of the ternary FPRM circuit:

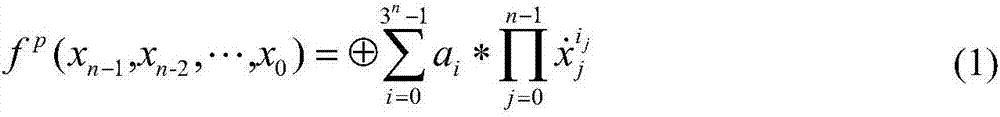

[0040] ①-1 The three-valued FPRM circuit is expressed as the following form using the three-valued FPRM logic function:

[0041]

[0042] Among them, n is the function f p (x n-1 ,x n-2 ,...,x 0 ), the number of variables for x n-1 ,x n-2 ,...,x 0 represents the function f p (x n-1 ,x n-2 ,...,x 0 ) of n input variables, p represents the function f p (x n-1 ,x n-2 ,...,x 0 ) polarity, the polarity p is expressed as p in n-bit ternary form n-1 p n-2 …p 0 ,p j ∈{0,1,2}, j=0,1,2,...,n-1, ⊕ means multi-input modulo 3 addition operation, ∑ is the accumulation symbol, the symbol "*" means the multiplication sign, i=0,1 ,2,…,3 n -1, i is expressed as i in n-digit ternary form n-1 i n-2 …i 0 , i j ∈{0,1,2},a i is the FPRM coeffic...

Embodiment 2

[0062] Embodiment two: a kind of ternary FPRM circuit power consumption optimization method utilizing exhaustive method, comprises the following steps:

[0063] ①Establish the power consumption estimation model of the ternary FPRM circuit:

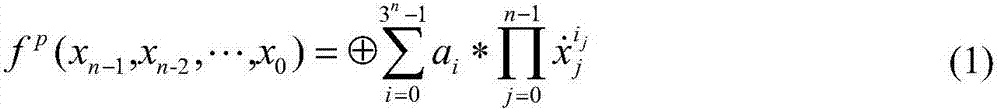

[0064] ①-1 The three-valued FPRM circuit is expressed as the following form using the three-valued FPRM logic function:

[0065]

[0066] Among them, n is the function f p (x n-1 ,x n-2 ,...,x 0 ), the number of variables for x n-1 ,x n-2 ,...,x 0 represents the function f p (x n-1 ,x n-2 ,...,x 0 ) of n input variables, p represents the function f p (x n-1 ,x n-2 ,...,x 0 ) polarity, the polarity p is expressed as p in n-bit ternary form n-1 p n-2 …p 0 ,p j ∈{0,1,2}, j=0,1,2,...,n-1, ⊕ means multi-input modulo 3 addition operation, ∑ is the accumulation symbol, the symbol "*" means the multiplication sign, i=0,1 ,2,…,3 n -1, i is expressed as i in n-digit ternary form n-1 i n-2 …i 0 , i j ∈{0,1,2},a i is the FP...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com