Multi-threshold low-power-consumption optimization method based on number of critical paths and sensitivity

A technology of critical path and optimization method, applied in electrical digital data processing, special data processing applications, instruments, etc., can solve problems such as high method complexity, unsatisfactory power consumption optimization effect, and weak priority index representation ability. Low method complexity, significant power optimization effect, and feature-rich effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

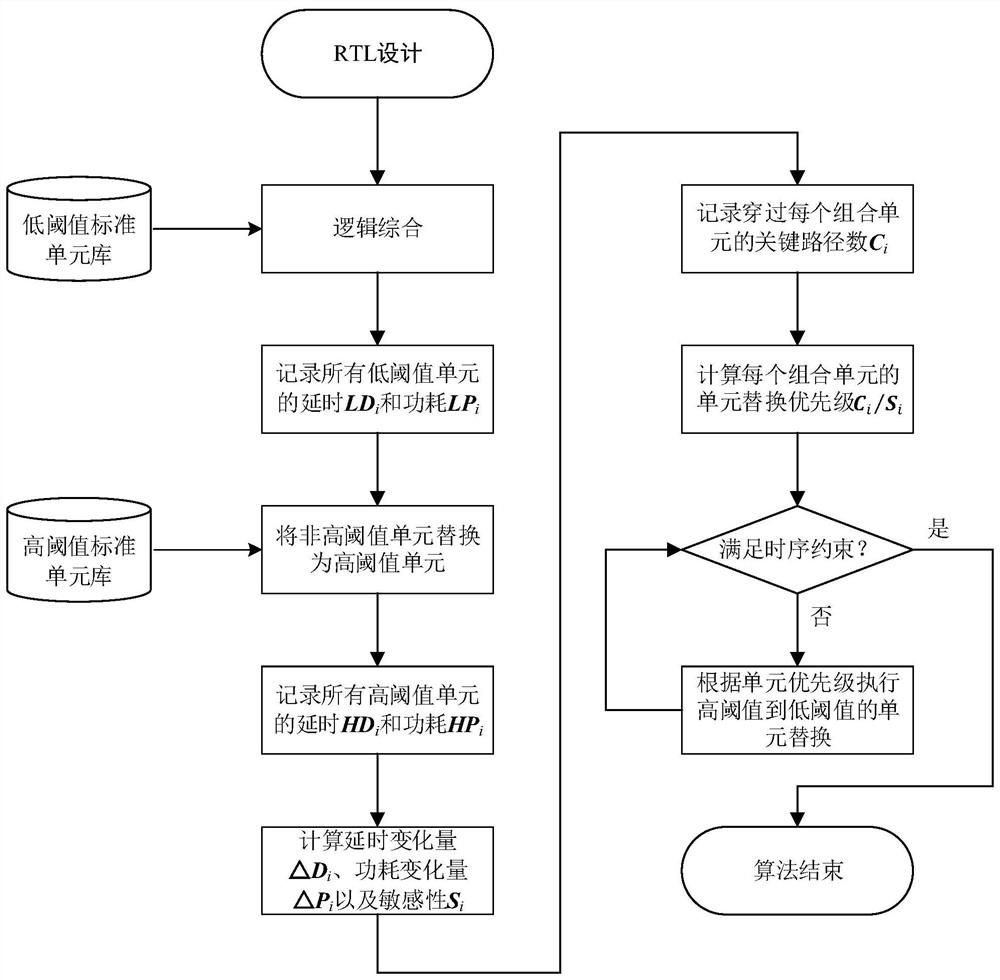

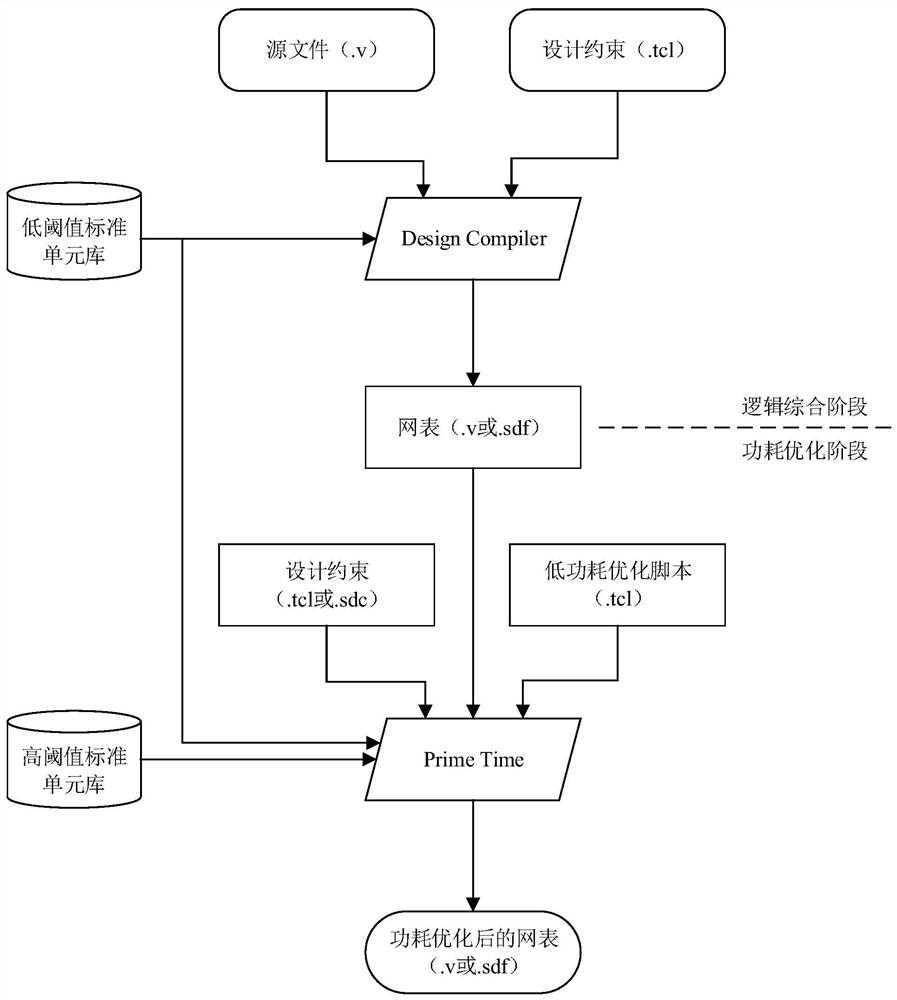

[0038] This embodiment provides a multi-threshold low-power optimization method based on the number of critical paths and sensitivities. The method first performs logic synthesis on the RTL design based on the low-threshold cell library and design constraint files, thereby obtaining the circuit netlist , power optimization is based on the circuit netlist.

[0039] After obtaining the circuit netlist, record the delay LD of each low-threshold combinational logic unit i and power dissipation LP i , and then replace all low-threshold combinational logic units with high-threshold combinational logic units, and record the delay HD of each high-threshold combinational logic unit i and Power Dissipation HP i , calculate the delay change ΔD of each combinational logic unit before and after the unit replacement operation i , power consumption variation ΔP i and sensitivity S i , where ΔD i =HD i -LD i , ΔP i = HP i -LP i , i = 1, 2, 3, . . .

[0040] Then record the numbe...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More