A Method for Optimum Polarity Search of Power Consumption in Ternary FPRM Circuit

A search method and power consumption technology, applied in the direction of error correction/detection using linear codes, data representation error detection/correction, error correction/detection using block codes, etc. conducting research, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

[0059] Embodiment one: a kind of ternary FPRM circuit power consumption optimal polarity searching method comprises the following steps:

[0060] ①Establish the power consumption estimation model of the ternary FPRM circuit:

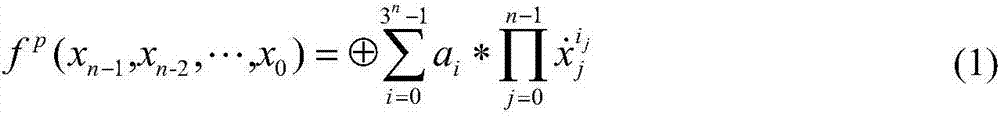

[0061]①-1 The three-valued FPRM circuit is expressed as the following form using the three-valued FPRM logic function:

[0062]

[0063] Among them, n is the function f p (x n-1 ,x n-2 ,...,x 0 ), the number of input variables, x n-1 ,x n-2 ,...,x 0 represents the function f p (x n-1 ,x n-2 ,...,x 0 ) of n input variables, p represents the function f p (x n-1 ,x n-2 ,...,x 0 ), the polarity p is expressed as p in ternary form n-1 p n-2 …p 0 ,p j ∈{0,1,2}, j=0,1,2,...,n-1, Indicates the modulo 3 addition operation, ∑ is the accumulation symbol, the symbol "*" is the multiplication operation symbol, and the subscript i=0,1,2,...,3 n -1, i is represented as i in ternary form n-1 i n-2 …i 0 , a i is the FPRM coefficient; a i ∈{0,...

Embodiment 2

[0094] Embodiment two: a kind of ternary FPRM circuit power consumption optimum polarity search method, comprises the following steps:

[0095] ①Establish the power consumption estimation model of the ternary FPRM circuit:

[0096] ①-1 The three-valued FPRM circuit is expressed as the following form using the three-valued FPRM logic function:

[0097]

[0098] Among them, n is the function f p (x n-1 ,x n-2 ,...,x 0 ), the number of input variables, x n-1 ,x n-2 ,...,x 0 represents the function f p (x n-1 ,x n-2 ,...,x 0 ) of n input variables, p represents the function f p (x n-1 ,x n-2 ,...,x 0 ), the polarity p is expressed as p in ternary form n-1 p n-2 …p 0 ,p j ∈{0,1,2}, j=0,1,2,...,n-1, Indicates the modulo 3 addition operation, ∑ is the accumulation symbol, the symbol "*" is the multiplication operation symbol, and the subscript i=0,1,2,...,3 n -1, i is represented as i in ternary form n-1 i n-2 …i 0 , a i is the FPRM coefficient; a i ∈{0,1...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com