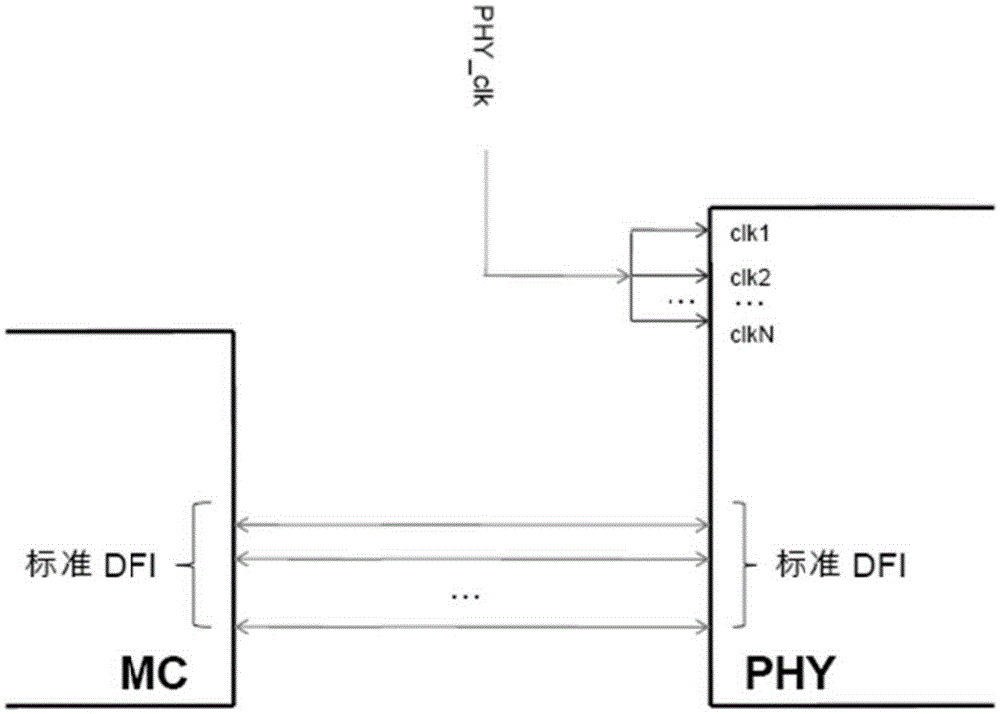

DDR controller low-power control circuit based on DFI interface

A technology for controlling circuits and controllers, which is applied in the direction of instruments, static memory, digital memory information, etc., and can solve the problem that dynamic power consumption cannot be controlled

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

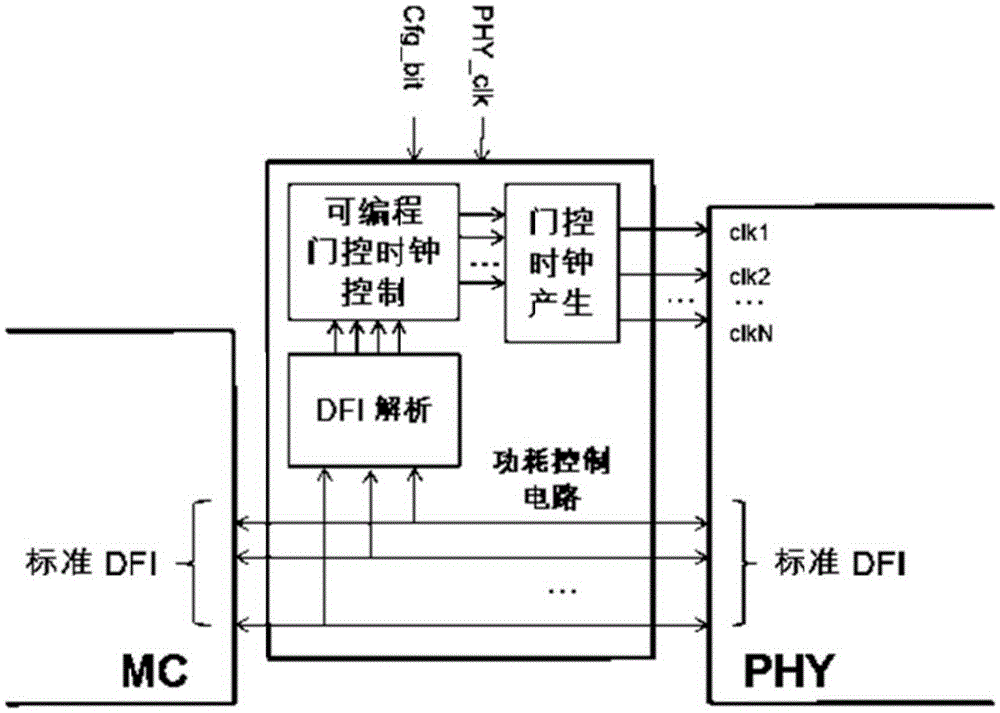

[0017] See figure 2 Shown is a preferred embodiment of the present invention. The power consumption control circuit is inserted between the DDR control logic and the DDRPHY in the DDR controller; the input end of the power consumption control circuit is connected to the DFI interface of the DDR control logic to obtain the DFI signal. The power consumption control circuit does not change the connection signal between the original DDR control logic and DDRPHY. The input end of the power consumption control circuit is also connected to the input clock signal PHY_clk that the system originally supplied to DDRPHY and the configuration signal Cfg_bit of the system; the output end of the power consumption control circuit is connected to DDRPHY.

[0018] The typical structure of the power control circuit includes a DFI analysis module, a programmable gated clock control module, and a gated clock generation module. The input terminal of the DFI analysis module is connected to the DFI o...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com