Chip testing and sorting method

A chip testing and sorting technology, applied in the direction of measuring electricity, measuring devices, measuring electrical variables, etc., can solve problems such as FAIL, misclassified results, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

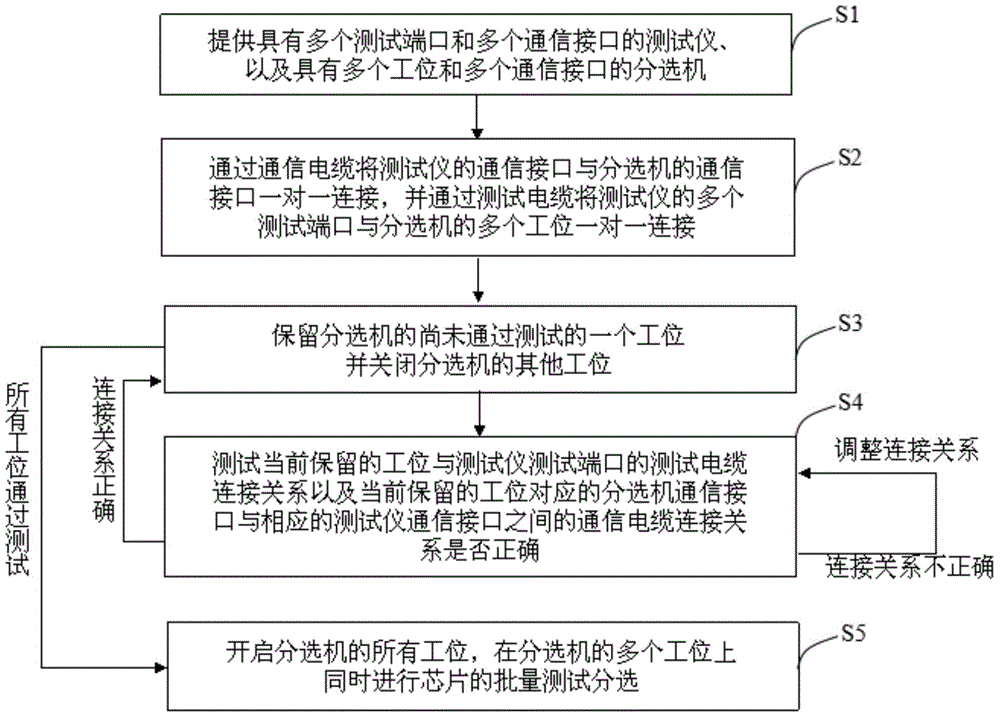

[0030] The specific embodiments of the present invention will be described in detail below in conjunction with the accompanying drawings.

[0031] image 3 It is a flowchart of a chip testing and sorting method provided by the present invention, and the chip testing and sorting method includes the following steps S1-S5.

[0032] S1. Provide a tester with multiple test ports and multiple communication interfaces, and a sorter with multiple stations and multiple communication interfaces.

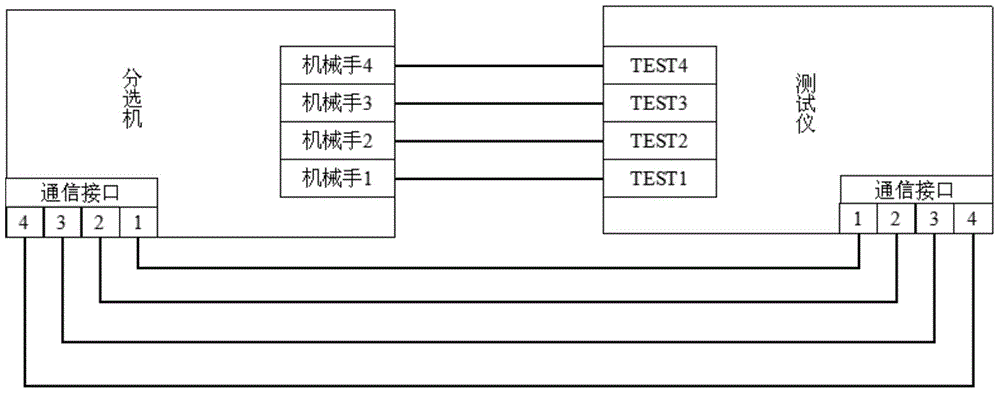

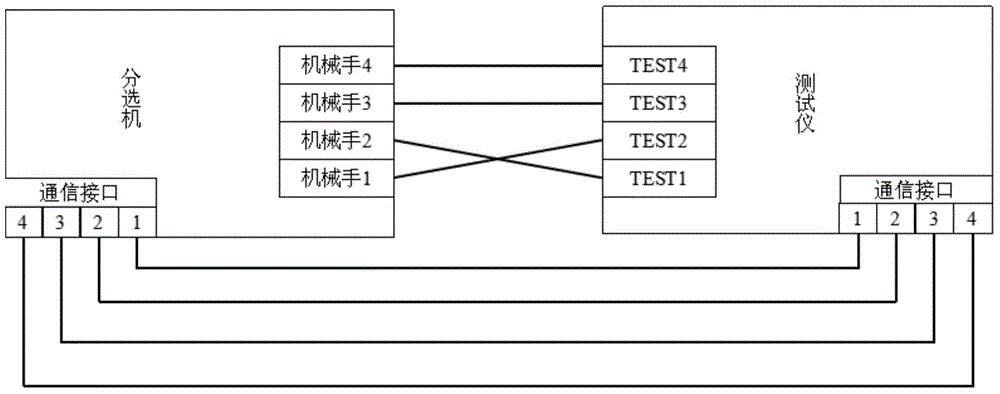

[0033] Please also see Figure 4 , in this embodiment, the tester 10 provided by S1 includes four test ports TEST1, TEST2, TEST3, TEST4 and a plurality of communication interfaces 101, 102, 103, 104; the sorter 20 provided by S1 includes four communication interfaces 201 , 202, 203, 204 and four stations. In this embodiment, each station of the sorter 20 is a manipulator for grabbing the chips to be tested, and the four stations of the sorter 20 are manipulator 1 , manipulator 2 , manipulat...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More