On-chip SET pulse testing method based on dynamic input vector

A technology of dynamic input and pulse testing, applied in the direction of pulse characteristic measurement, monitoring pulse chain mode, measuring device, etc., can solve the problem of difficult analysis of integrated circuit soft error rate and achieve accurate results

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

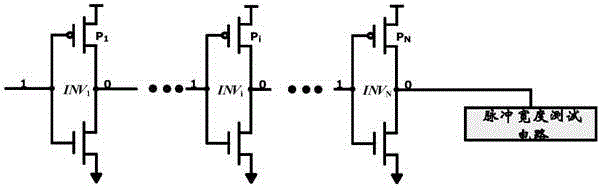

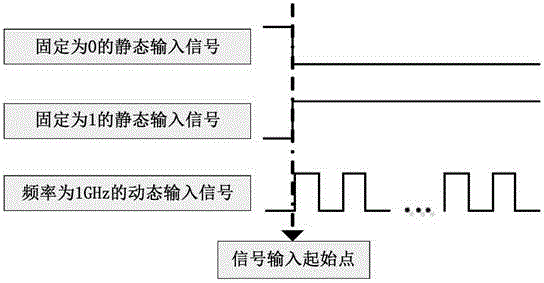

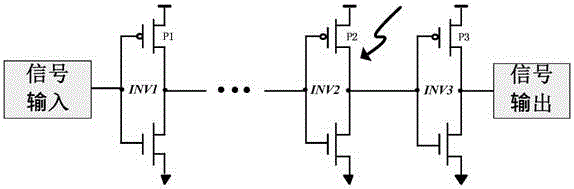

[0029] figure 1 It is a logic structure diagram of the SET pulse test circuit currently used internationally in the background art. At present, the common SET pulse width test circuit in the world is composed of a SET pulse generation circuit composed of an inverter chain composed of N-level inverters, and a pulse width test circuit. The i-level inverter is recorded as INV i , i is an integer, 1≤i≤N. The process of testing the SET pulse width is to figure 1 The input is fixed at 0 or 1 (that is, the static input vector is used to test the on-chip SET pulse, see figure 2 A static input signal fixed at 0, a static input signal fixed at 1). However, in a real circuit, the input is constantly changing (that is, the input is dynamically changing, and the maximum frequency of change is the clock frequency, such as figure 2 As shown by the dynamic input signal with a frequency of 1GHz), the dynamic input signal in the real circuit is constantly changing between 0 and 1.

[003...

PUM

Login to view more

Login to view more Abstract

Description

Claims

Application Information

Login to view more

Login to view more - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap