Split-path fused multiply-accumulate operation using first and second sub-operations

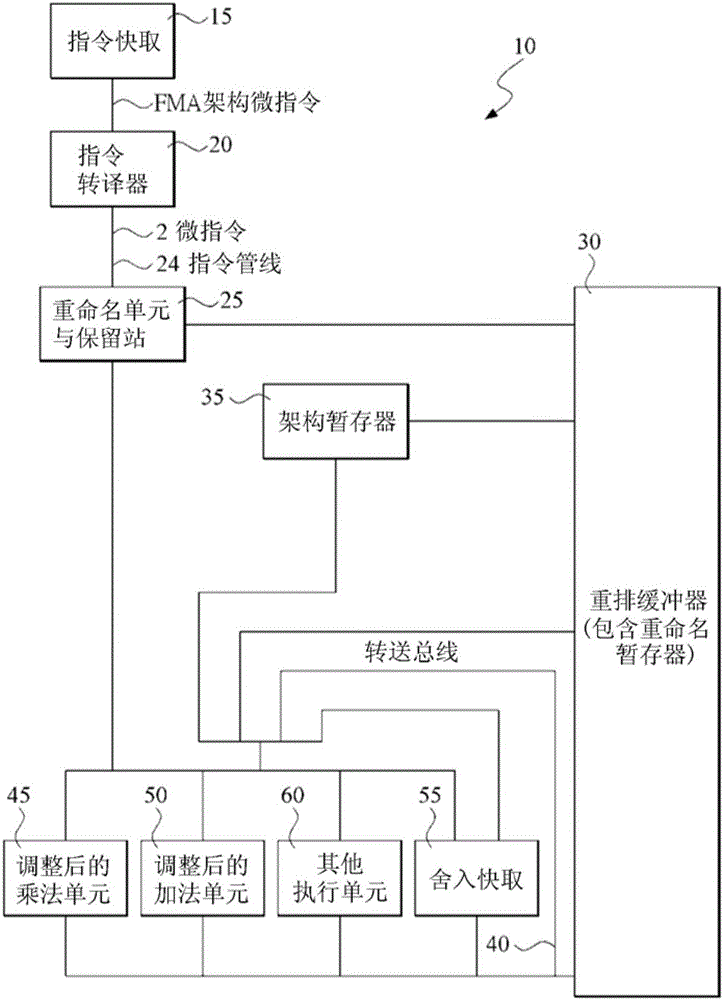

A partial product and product technology, applied in the field of microprocessor design integrating floating-point product-accumulate operations, which can solve problems such as limited improvement, failure to fully achieve FMA design goals, and increased setup costs.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

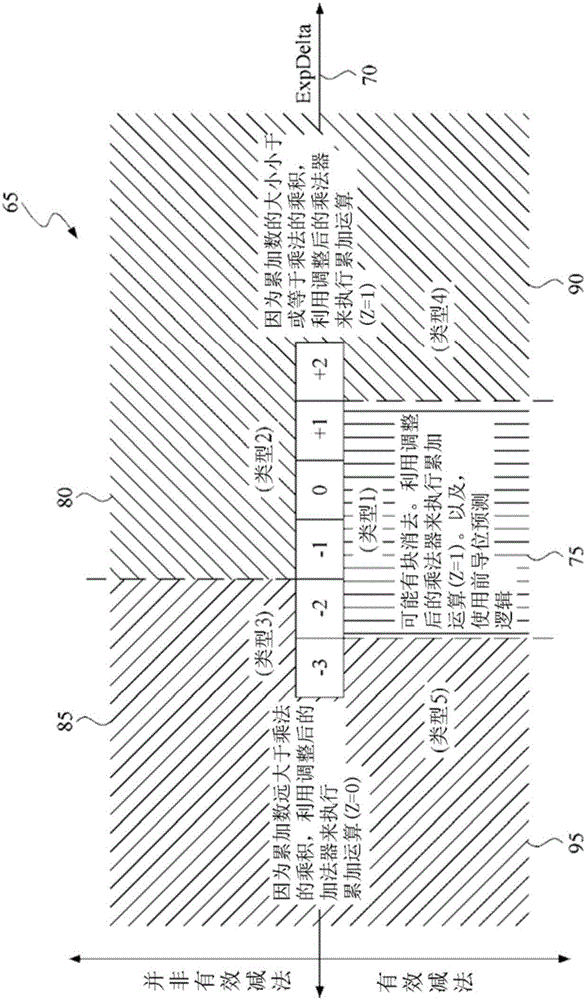

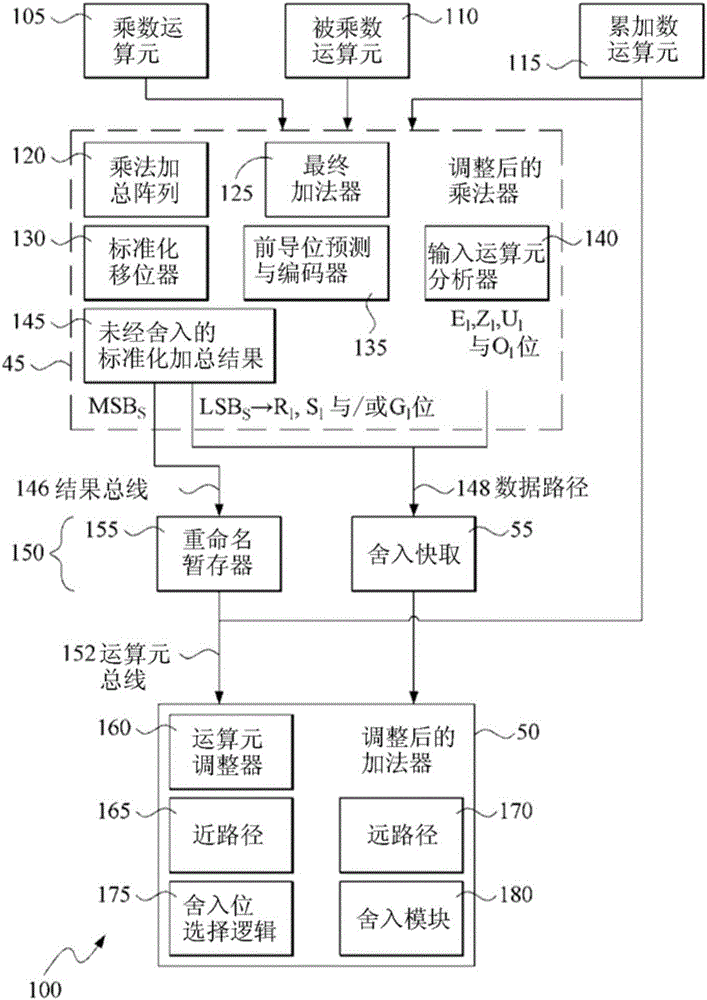

Method used

Image

Examples

other Embodiment approach

[0332] In other implementations, the rounding cache can be an addressable register bit, a content-accessible memory, a queue storage space, or a mapping function.

other Embodiment approach

[0333] Other embodiments may provide multiple independent hardware or execution units to execute the first microinstruction, and / or provide multiple independent hardware or execution units to execute the second microinstruction. Likewise, these embodiments may also provide multiple round caches for different source code instruction streams or data streams, or various embodiments of multi-core computer processors, if advantageous.

[0334] This implementation is for superscalar, non-sequential instruction dispatch, but other implementations can also be used for in-order instruction dispatch, for example, by removing instructions from the instruction cache and providing them to the data forwarding network. Distributed from the provided multiplication unit to a separate addition unit. The instantiation of the classification of FMA operations by the present invention, and the minimal amount of hardware adjustments required by the present invention, also have advantages in sequenti...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More