Implementation method of multi-core timer and multi-core system

An implementation method and multi-core system technology, applied in the field of multi-core timer implementation and multi-core system, can solve problems such as low timer efficiency and uneven multi-core load, so as to avoid information loss and delay, improve timing efficiency and system stability, Solve the effect of overloading

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

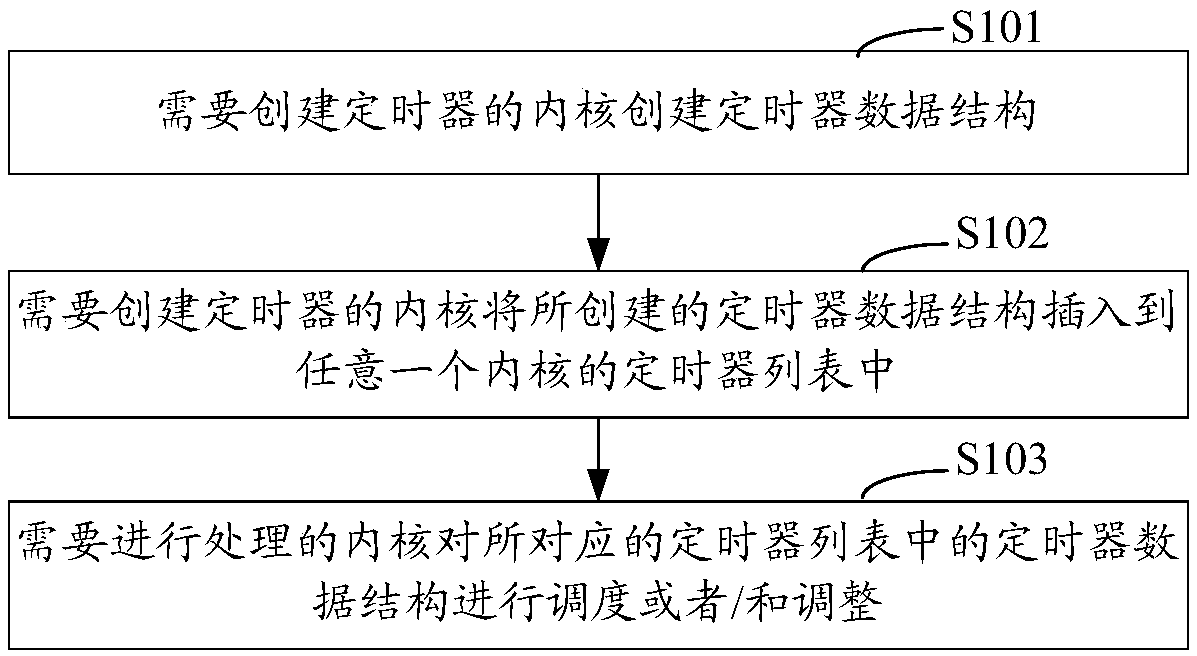

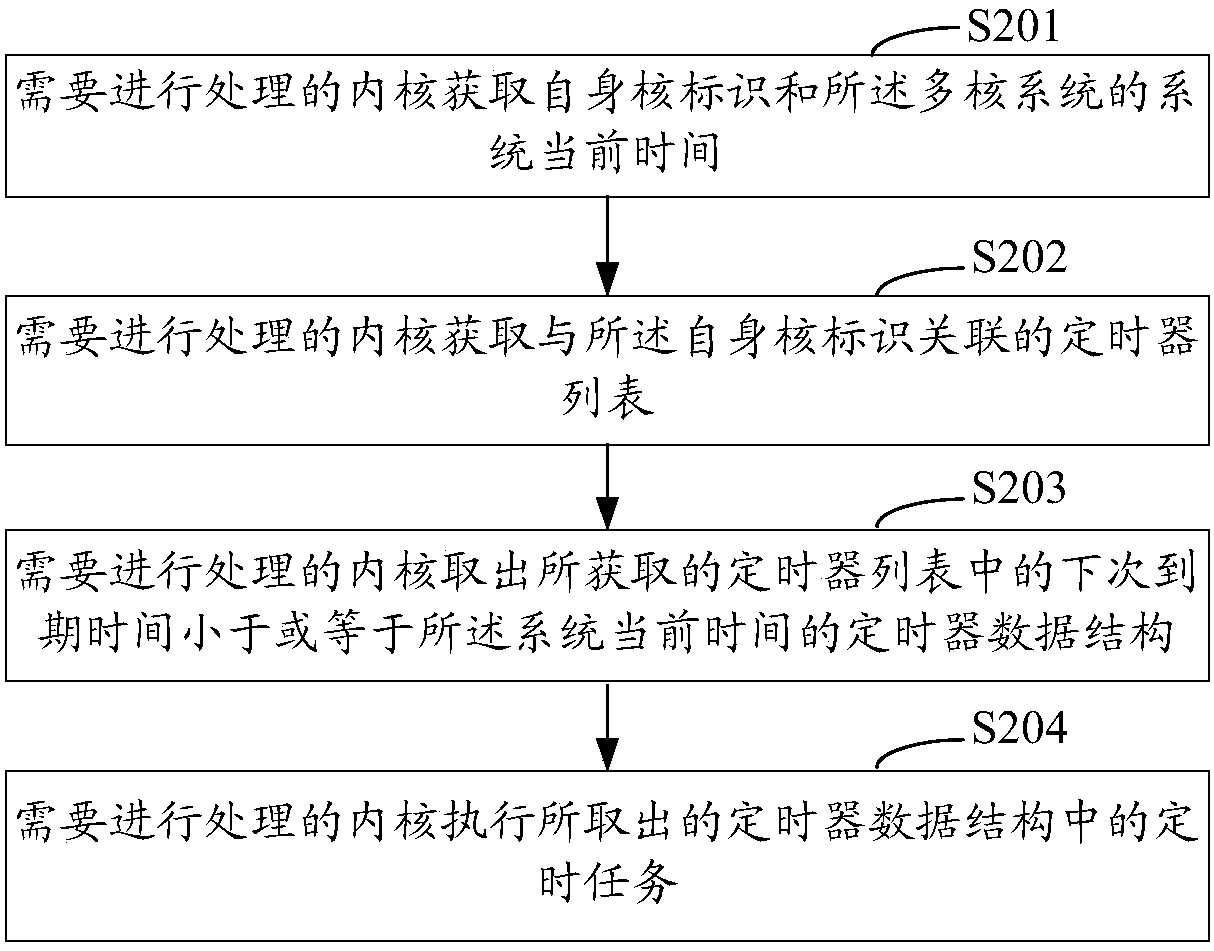

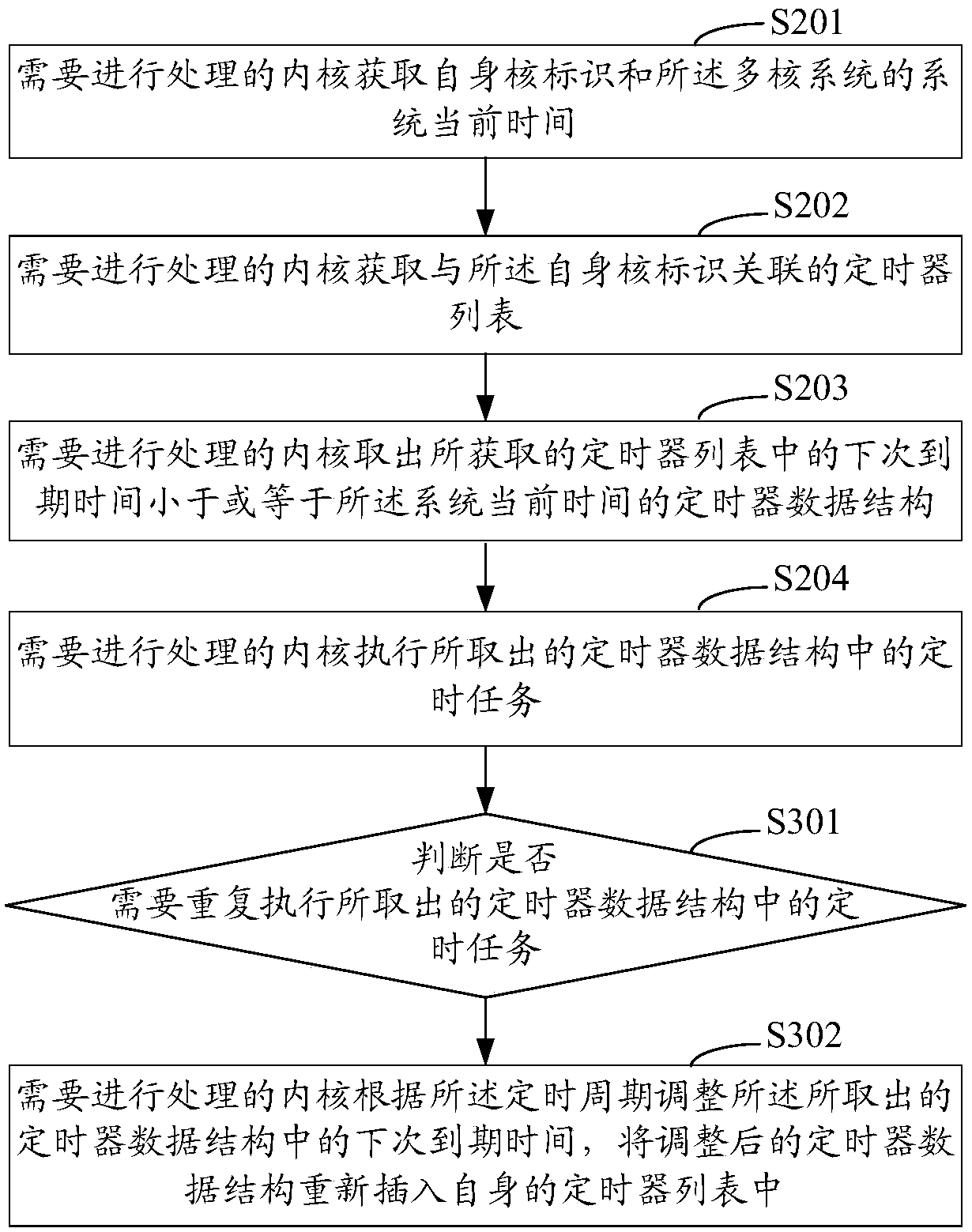

[0028] Embodiment 1 of the present invention provides a method for implementing a multi-core timer, figure 1 It is a schematic diagram of the implementation process of the multi-core timer implementation method in Embodiment 1 of the present invention Figure 1 , in this embodiment, a timer list with the same number of cores as the multi-core system is pre-configured, wherein each core corresponds to one timer list, such as figure 1 As shown, the multi-core timer implementation method in this embodiment includes:

[0029] Step S101: the kernel that needs to create a timer creates a timer data structure;

[0030] Here, the need to create a timer is any core in the multi-core system that currently needs to create a timer;

[0031] Here, the timer data structure is a storage structure of timer data (or called timer related information), which is used to save timer related information;

[0032] Step S102: The kernel that needs to create a timer inserts the created timer data st...

Embodiment 2

[0073] Based on the first embodiment above, the second embodiment of the present invention provides a multi-core system, see Figure 5 As shown, it is a schematic diagram of the composition and structure of the multi-core system in Embodiment 2 of the present invention Figure 1 ;like Figure 5 As shown, the multi-core system in this embodiment includes multiple cores 50, and each core 50 in the multiple cores 50 is respectively configured with a timer list, and each core 50 in the multiple cores 50 includes:

[0074] A creation unit 501, configured to create a timer data structure;

[0075] Insertion unit 502, for inserting the timer data structure created by creation unit 501 into the timer list of any kernel;

[0076] The processing unit 503 is configured to process the timer data structure in the corresponding timer list.

[0077] In one of the embodiments, the timer data structure is used to save timer-related information, and the timer-related information includes the...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More