A hardware implementation circuit of fft butterfly operation supporting complex multiplication

A complex number multiplication and butterfly operation technology, which is applied in the field of FFT butterfly operation hardware implementation circuit, can solve the problems of short development time, high power consumption, and difficulty in DSP chips, so as to reduce standardized operations, reduce hardware overhead, The effect of reducing the calculation delay

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

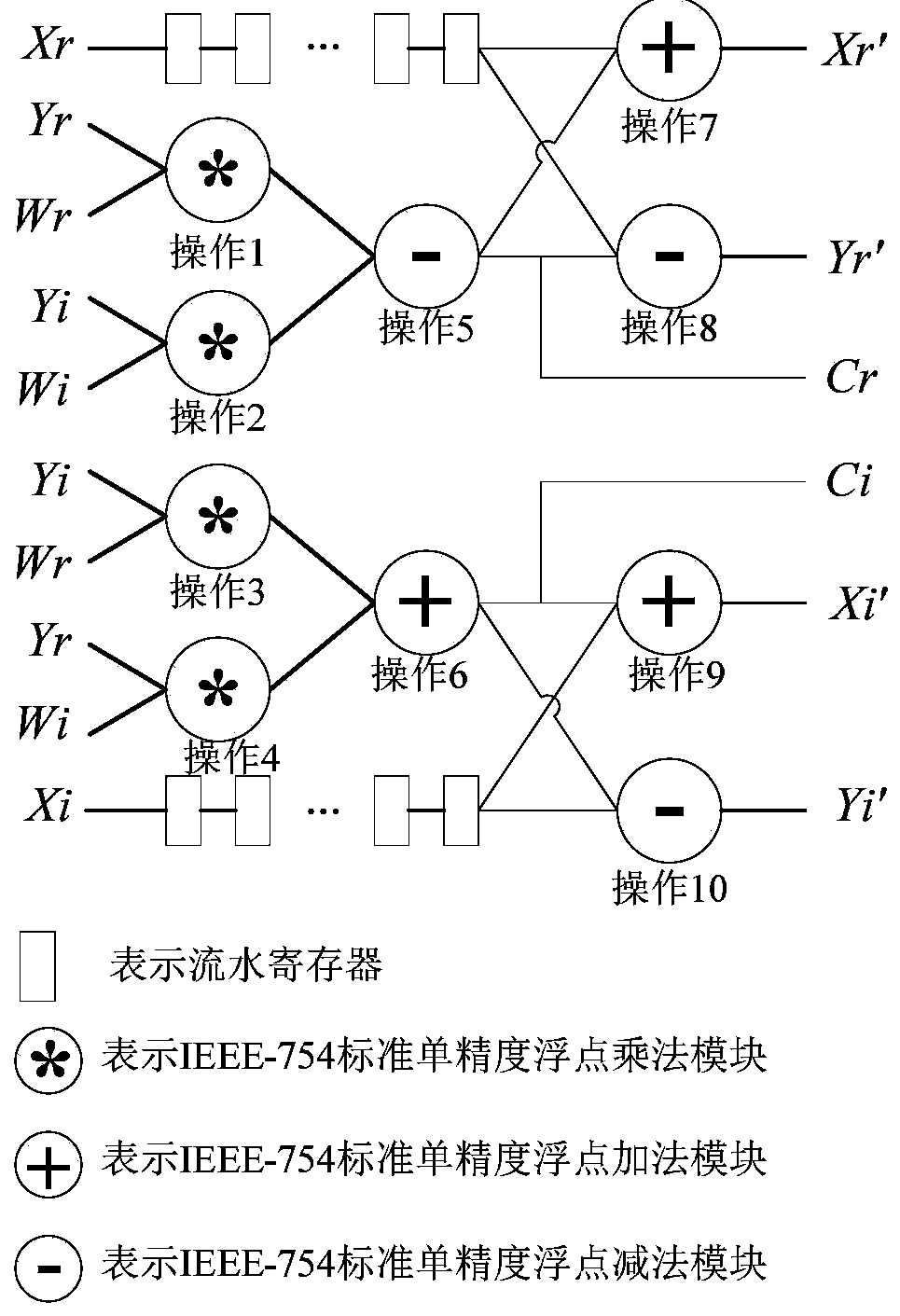

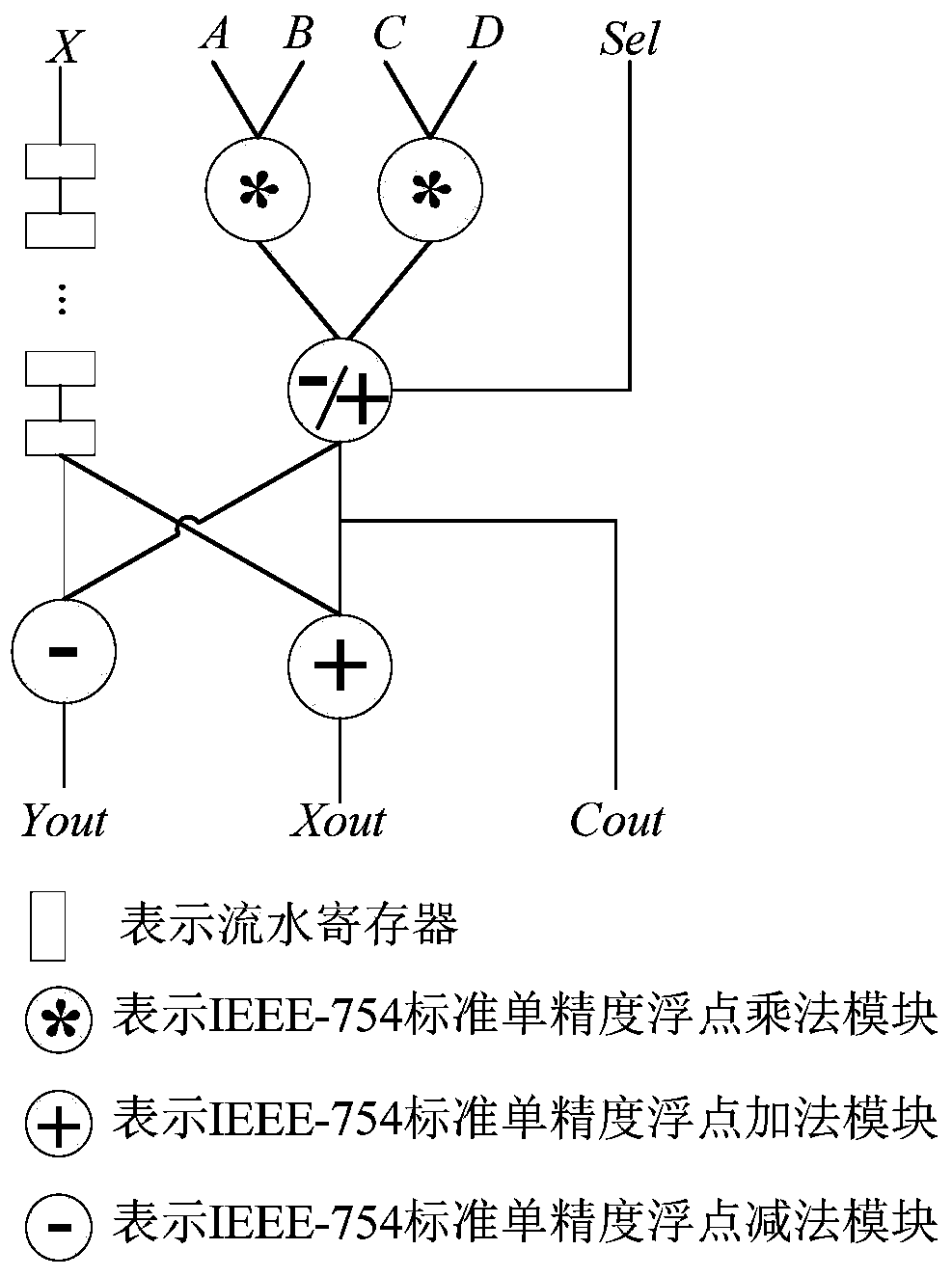

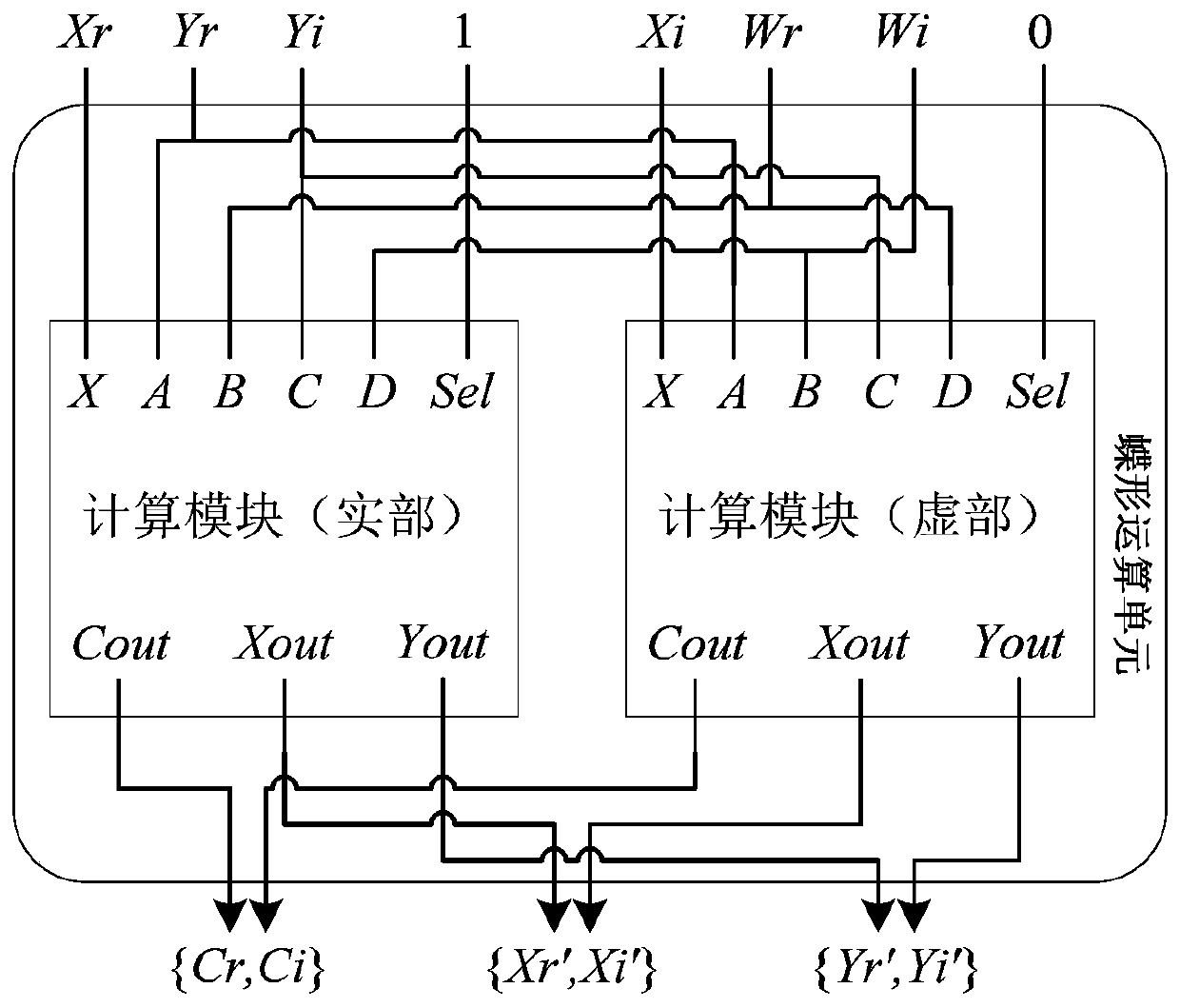

Method used

Image

Examples

Embodiment Construction

[0024] The present invention will be further described in detail below in conjunction with the accompanying drawings and specific embodiments.

[0025] For large-scale FFT calculations, the Cooly-Tukey FFT algorithm is usually used. The Cooly-Tukey FFT algorithm adopts the idea of divide and conquer, and uses two-dimensional FFT simulation to realize a large-scale one-dimensional FFT (N). For N=N 1 *N 2 FFT of points can be done with N 2 N 1 Point and N 1 N 2 Point FFT algorithm to achieve, the iterative formula is as follows:

[0026]

[0027] where 0≤k 1 1 , 0≤k 2 2 .

[0028] Its calculation steps can be divided into the following:

[0029] Step 1, column direction FFT: perform N 2 times N 1 Point FFT operation, that is, perform N 2 The following formula:

[0030]

[0031] Step 2, compensation twiddle factor: multiply the result of step 1 by the compensation twiddle factor

[0032] Step 3, FFT in the row direction: on the basis of step 2, perform N...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More