A Simple Non-PLL Video Synchronization Method

A video synchronization, phase-locked loop technology, applied in the direction of pulse modulation TV signal transmission, etc., can solve problems such as unsuitable vibration

Inactive Publication Date: 2014-08-20

LUOYANG INST OF ELECTRO OPTICAL EQUIP OF AVIC

View PDF0 Cites 0 Cited by

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

The main reason is that the VC0 of the chip requires external adjustable inductors and capacitors to achieve frequency multiplication, requires stable circuit parameters, and is not suitable for vibration and wide temperature working conditions

Method used

the structure of the environmentally friendly knitted fabric provided by the present invention; figure 2 Flow chart of the yarn wrapping machine for environmentally friendly knitted fabrics and storage devices; image 3 Is the parameter map of the yarn covering machine

View moreImage

Smart Image Click on the blue labels to locate them in the text.

Smart ImageViewing Examples

Examples

Experimental program

Comparison scheme

Effect test

Embodiment

the structure of the environmentally friendly knitted fabric provided by the present invention; figure 2 Flow chart of the yarn wrapping machine for environmentally friendly knitted fabrics and storage devices; image 3 Is the parameter map of the yarn covering machine

Login to View More PUM

Login to View More

Login to View More Abstract

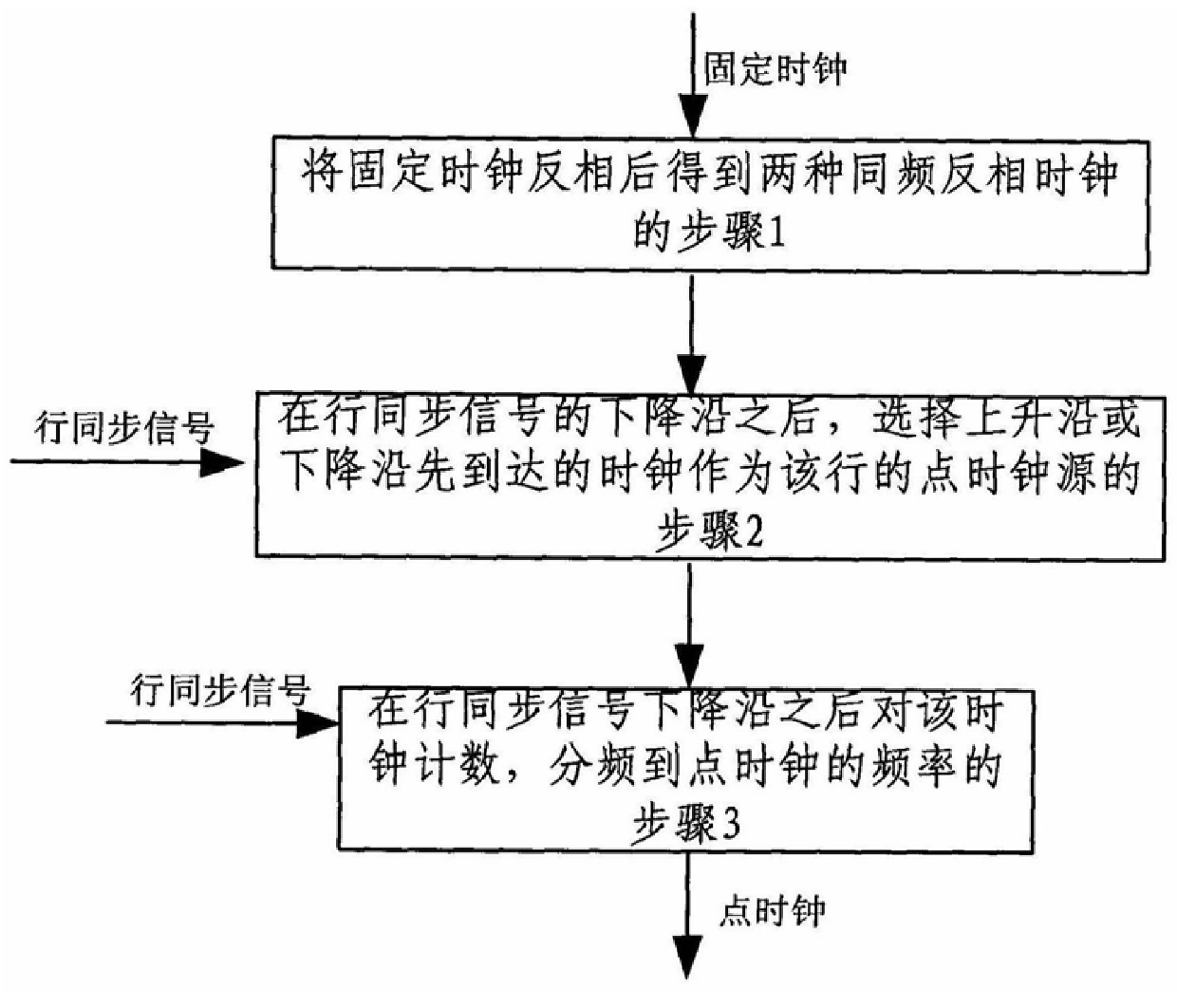

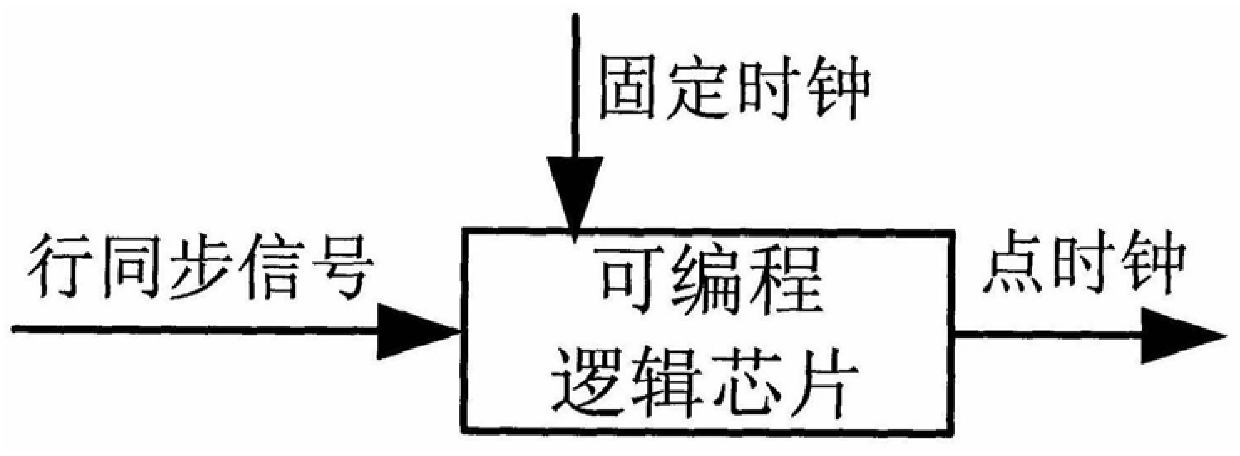

The invention belongs to electronic design technology, and relates to a simple non-phase-locked loop video synchronization method in the composite video digitization function. The technical solution of the present invention is: (1) the step of obtaining two kinds of inverting clocks with the same frequency after inverting the fixed clock; (2) after the falling edge of the horizontal synchronization signal, select the clock whose rising edge or falling edge arrives first The step of being the dot clock source of the line; (3) the step of counting the clock after the falling edge of the line synchronization signal, dividing the frequency to the dot clock frequency, and outputting the dot clock. The present invention abandons the long-standing traditional idea that the dot clock is generated by the multiplication and phase-locking of the line synchronization signal when the analog-to-digital conversion is performed on the composite analog video signal. It is generated in a non-phase-locked state, but its error is guaranteed to be within the allowable range, and the synchronization effect is also achieved.

Description

A Simple Non-PLL Video Synchronization Method technical field The invention belongs to electronic design technology, and relates to a simple non-phase-locked loop video synchronization method in the composite video digitization function. Background technique To realize the digitization function of composite analog video, it is necessary to generate a point clock that triggers sampling. Currently, there are two schemes for generating a point clock that triggers sampling. A video front-end processing chip with a phase-locking function is used to directly input video signals to obtain digital signals such as synchronization signals, video data, and point clocks for subsequent processing. The control of this type of chip is complicated, and communication settings are required after power-on, and the sampling rate cannot be adjusted. The other is a solution using discrete chips, including synchronous separation and multiplier locking. We have found in practice that the mult...

Claims

the structure of the environmentally friendly knitted fabric provided by the present invention; figure 2 Flow chart of the yarn wrapping machine for environmentally friendly knitted fabrics and storage devices; image 3 Is the parameter map of the yarn covering machine

Login to View More Application Information

Patent Timeline

Login to View More

Login to View More Patent Type & Authority Patents(China)

IPC IPC(8): H04N7/56

Inventor 郑鑫

Owner LUOYANG INST OF ELECTRO OPTICAL EQUIP OF AVIC