Methods and apparatus for a multiple master bus protocol

A bus and protocol technology, applied in the field of multi-master bus protocol devices, can solve problems such as incompatibility

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

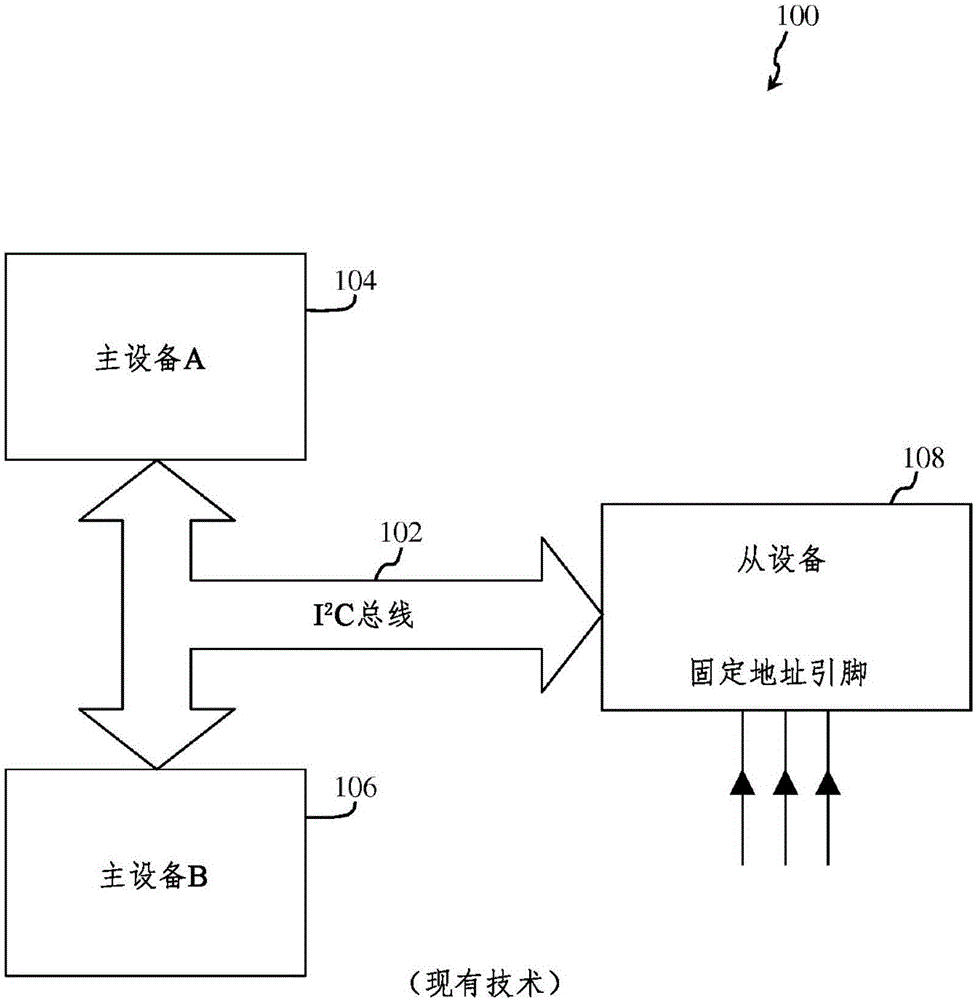

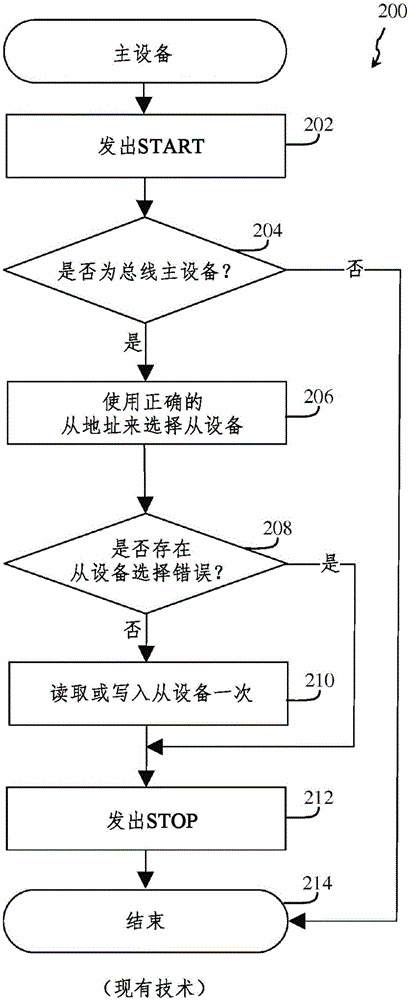

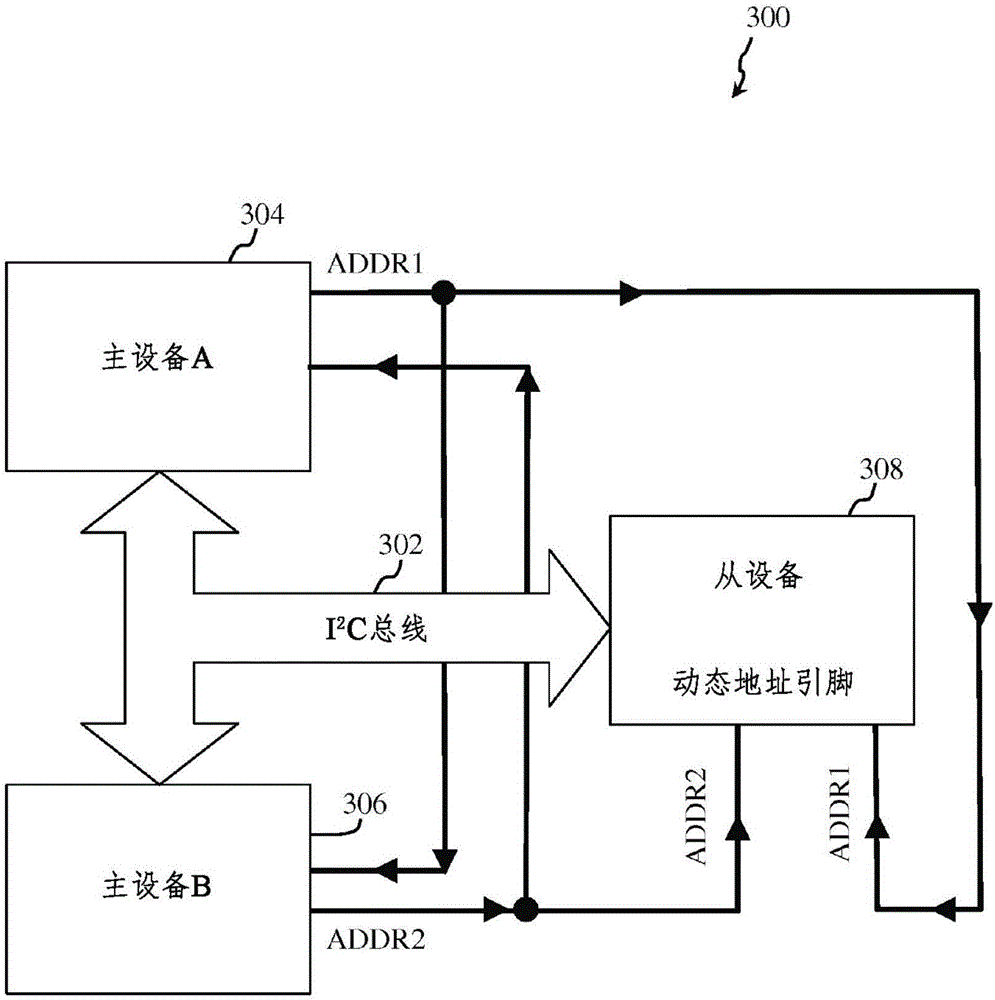

[0014] Embodiments of the present invention provide the following improved type I 2 C multi-master bus monopoly method and apparatus: the method and apparatus enable, without interfering with slave-related transactions carried out by other masters, 2 Multiple, non-interruptible slave-related transactions are performed on the C bus. Standard I 2 The C specification provides for enabling one of multiple masters to obtain access to the I 2 An arbitration method for control of the C-bus, but does not provide any means for the master to maintain exclusive control, eg, to complete multiple transactions (eg, read-modify-write transactions) without interrupting the sequence. The present invention enables a master (e.g., microcontroller) to retain exclusive access to a slave (e.g., memory) for multiple consecutive transactions in a manner that does not compete with other masters' access to the slave (e.g., memory) . Note that the term "single transaction" used here means a single r...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More