Processor Chip Emulator

An emulator and processor technology, applied in the field of emulators, can solve problems such as unfavorable development, debugging and testing, affecting development efficiency, functional differences between emulators and actual chips, etc., to improve development and debugging efficiency, and facilitate development and debugging. Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

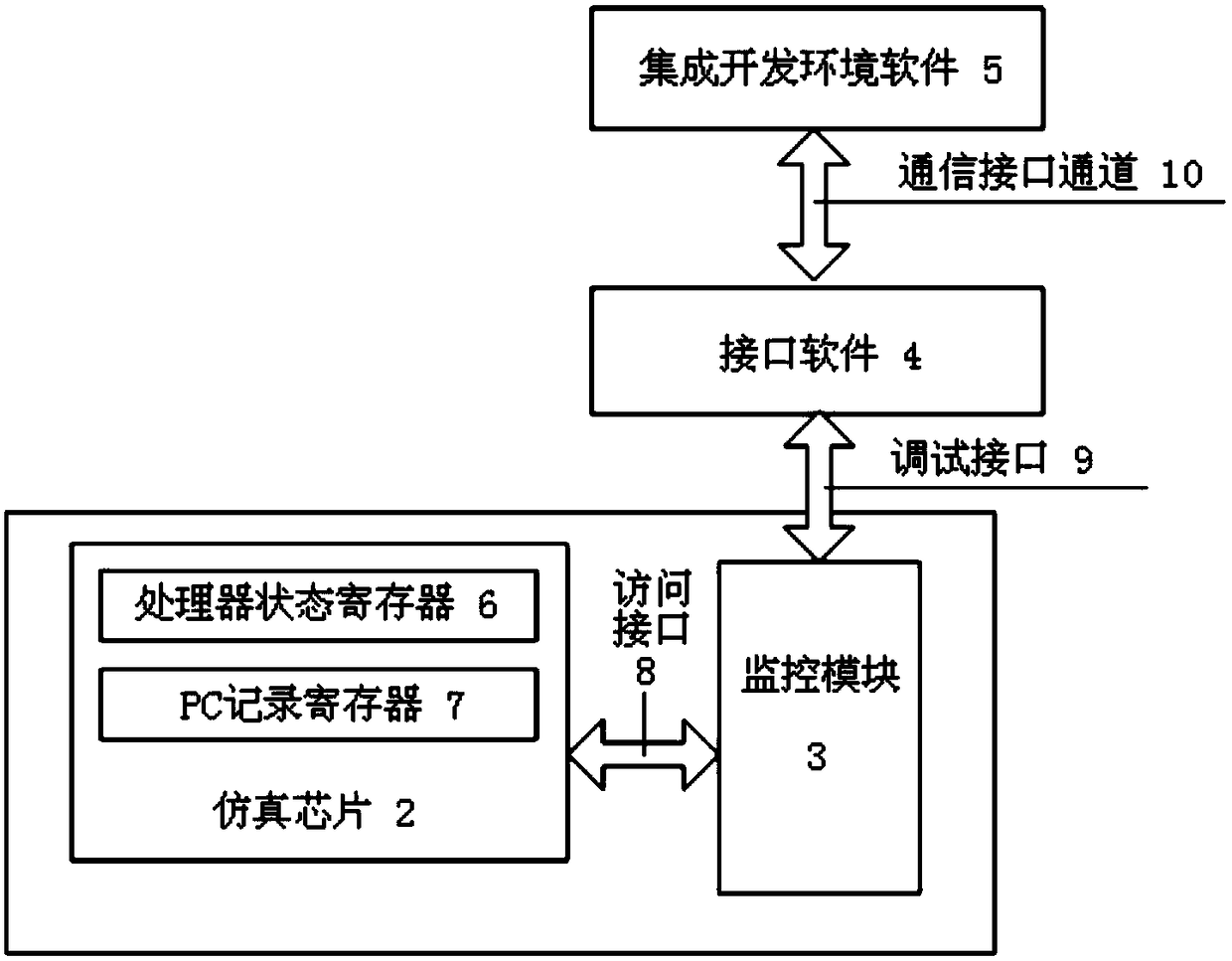

[0011] Such as figure 1 As shown, the processor chip emulator includes: an emulation chip 2, a monitoring module 3, and an integrated development environment software 5 and an interface software 4 installed on a user computer. The emulation chip 2 has a processor status register 6 and a PC recording register 7 . The monitoring module 3 is connected with the emulation chip 2 through the access interface 8, and is connected with the user computer through the debugging interface 9 to realize information transmission with the interface software 4, and the interface software 4 communicates with the integrated development environment software through the communication interface channel 10. 5 for information transmission.

[0012] The emulation chip 2 can simulate all functions of the product chip, including the function of entering and exiting the low power consumption state; at the same time, the processor status register 6 and the PC record register 7 belonging to the debugging l...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More