An Adaptive Method for Incremental Step Pulse Programming of Flash Memory

A flash memory, memory cell technology, applied in static memory, read-only memory, digital memory information, etc., can solve problems such as slow programming, low programming efficiency, and long overall programming performance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

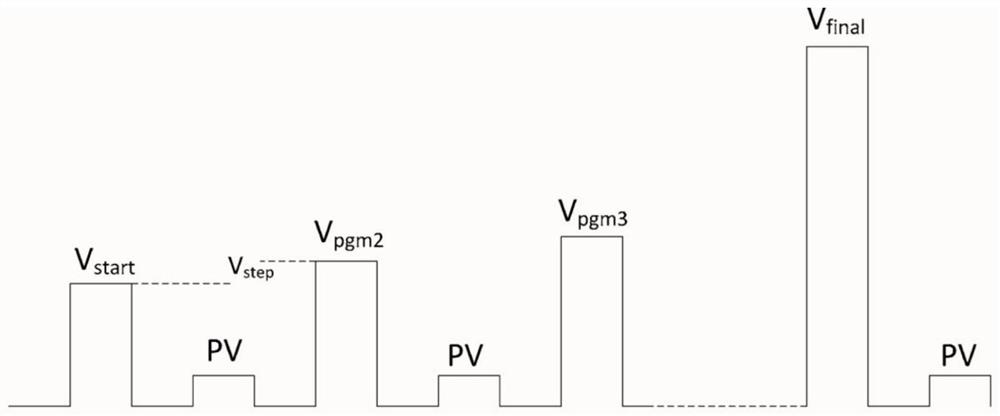

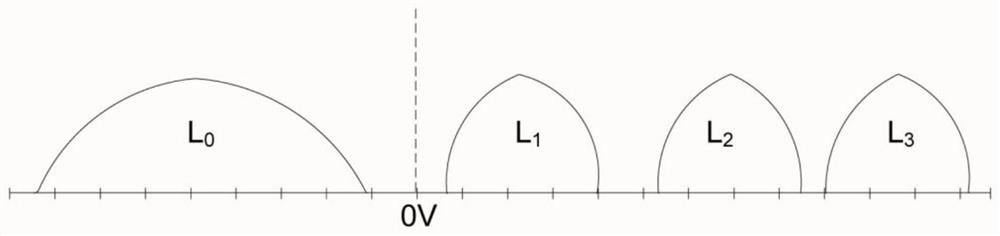

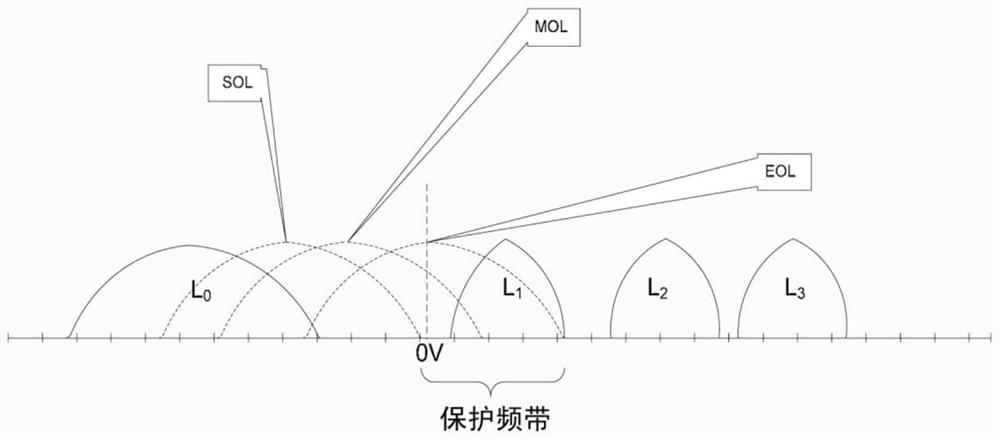

[0029] In the present disclosure, an adaptive programming method for programming flash memory that significantly reduces the total programming time with minimal overhead is described. Figure 4 Is a flowchart 400 illustrating an adaptive programming technique according to some embodiments. At step 402, flash memory programming is initiated. First, the test programming voltage is used to detect the cell programming speed (step 404). Then, adjust the start programming voltage V based on the detected cell programming speed start (Step 406). Then, use V start ISPP is performed on the adjusted value of (step 408). This technology makes V start Changes are made at different stages of the life of the flash memory to cause changes in the programming characteristics of the memory cells. For example, when programming is faster than the end of life (EOL) of the memory device, in the beginning of life (SOL) of the memory device, the adaptive technology results in a higher V start Value, ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com